XiaoMi-AI文件搜索系统

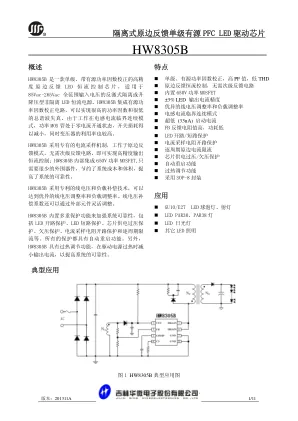

World File Search System隔离式原边反馈单级有源PFC LED驱动芯片- HW8305B

1. 吉林华微电子有限公司的产品销售方式为直销或代理销售,客户订货时请与我公司核实。 2. 我们强烈建议客户在购买我公司产品时仔细查看商标,如有任何问题,请随时与我们联系。 3. 电路设计时请不要超过器件的绝对最大额定值。 4. 吉林华微电子有限公司保留对本规格书进行更改的权利,如有更改,恕不另行通知。

“ AI芯片,可实现高效和高速处理,下一代计算机...

在2020年进行的第一次临时评估中,该公司收到了:项目定位和必要性:评估A(非常重要的)研究和开发管理:评估B(良好)研究和发展结果:评估B(良好的)努力将结果置于实际用途中:评估C(几乎合理)。 作为对评估的评论,尽管该公司对其业务状况,NEDO的管理和开发结果进行了评估,但Nedo有必要收集有关全球技术趋势的信息,并考虑并扩大措施以获取市场。此外,关于下一代计算技术的开发,还需要开发人力资源并创建与可能成为用户的业务实体进行沟通的场所。 回应评估结果:为了收集有关全球技术趋势的信息,我们将同时进行研究和开发项目1和2,从2021年开始,将对技术趋势和知识产权策略进行调查。获得的信息被送回了运营商,Nedo还进行了管理。此外,关于R&D项目1,作为促进工业应用的衡量标准,该公司还根据调查结果和临时评估的结果制定了“与节能AI半导体和系统有关的技术开发”的新政策,并正在通过FY22的授予项目促进研究结果的实际应用和商业化。 关于研究和开发项目,作为人力资源开发的一部分,开发的量子计算机通用软件不仅在云环境中免费公开,而且还通过举办竞赛和经验尖端技术来使公司对人力资源开发的贡献。此外,大脑计算成立了一个咨询委员会,将可能成为用户的企业汇集在一起,这些企业有望利用开发的脑型芯片和算法,并通过共享结果并交流开发人员的意见来弥合业务。此外,在光学分散计算中,我们将使用100公里内的数据中心进行分布式信息处理的演示实验,并在20025财年的范围内进行,并发布结果以促进早期商业化。

芯片

Andrew B. Kahng 是加州大学圣地亚哥分校 CSE 和 ECE 的杰出教授,也是高性能计算的特聘教授。他曾担任 Cadence 的客座科学家(1995-97 年)和 Blaze DFM 的创始人/首席技术官(2004-06 年)。他是 3 本书和 500 多篇期刊和会议论文的合著者,拥有 35 项已颁发的美国专利,并且是 ACM 和 IEEE 的研究员。他是 2019 年 Ho-Am 工程奖获得者。他曾担任 IEEE CEDA 赞助的会议(如 DAC、ISPD、SLIP 和 MLCAD)的总主席,并从 2000 年至 2016 年担任国际半导体技术路线图 (ITRS) 设计和系统驱动程序工作组的国际主席/联合主席。2018年6月至2023年12月,他担任美国DARPA“OpenROAD”项目(https://theopenroadproject.org/)的首席研究员,并至2023年8月担任美国NSF人工智能研究所“TILOS”(https://tilos.ai/)的首席研究员和主任。

第 8 章:单芯片和多芯片集成

1. 2020 – 2021 年颠覆、错位和创新历史将把 2020 年和 2021 年标记为全球颠覆、错位和创新迅速发展的时期,其规模在和平时期极为罕见。颠覆包括全球 COVID-19、极端野火和洪水,同时还伴随着气候变化和半导体短缺。2020 年 1 月,HIR 团队和 EPS 圣克拉拉谷分会与 SEMI 同事一起计划于 2 月 23 日至 24 日举办第三届 HIR 研讨会和年会,并满怀激动地庆祝 2019 年 10 月第一届 HIR 的发布。当三星工厂对游客关闭时,我们将年会地点从圣何塞的新三星展示工厂移至了米尔皮塔斯的 SEMI 全球总部。这次会议取得了巨大成功,在正式的工作会议、午餐会、品酒会和名片交换中,大家进行了大量的交流。在这次 HIR 会议的第二天,我们的一些行业同事开始收到公司通知,限制参加会议的旅行,以减轻 COVID-19 风险。我们几乎没有想到我们今天所知道的 COVID-19 大流行的程度和破坏性。下面显示的是来自世界卫生组织 2021 年 10 月 6 日仪表板的数据。

第 8 章:单芯片和多芯片集成

第 1 部分:执行摘要和范围简介集成电路发明 60 多年来,一直有人定期预测摩尔定律将终结。虽然设计和工艺技术方面正在进行重大创新,以继续推动向下一个节点的发展,但摩尔定律的经济效益即将终结,先进节点的一些关键性能指标正在趋于稳定,正如商业杂志《经济学人》2016 年 3 月 12 日的一篇文章所描述的“摩尔定律饱和”(图 1.1)。半导体行业正在实施 EUV、FinFET 和 FinFET 后继者。5 纳米节点已处于早期生产阶段,3 纳米节点即将到来。摩尔博士自己对摩尔定律技术终结的预测正在接近目标年份。2016 年 3 月 12 日文章中的信息在今天仍然具有现实意义。

芯片最后扇出作为芯片优先的替代方案

我们将介绍一种新的芯片优先 FOWLP 替代方案,该替代方案可满足大量需要 FOWLP 等封装技术的应用的需求。这种新封装已在 ASE 投入生产一年多,并使用“芯片最后”方法来解决增加可用互连焊盘面积的问题。已用铜柱 (Cu) 凸块凸起的芯片被批量回流到低成本无芯基板上,然后进行包覆成型,该包覆成型也用作芯片底部填充。Cu 柱允许以 50 µm 或更小的间距直接连接到芯片焊盘,从而无需在芯片上形成 RDL。使用嵌入式迹线允许细线和间距低至 15µm 或更小,并直接键合到裸铜上。Cu 柱键合到铜迹线的一侧,焊球或 LGA 焊盘直接位于铜的另一侧。这使得基板实际上只与走线中使用的铜一样厚,并使最终封装的厚度达到 400µm。由于这使用现有的大批量封装基础设施,因此可以轻松实现更复杂的组装,包括多个芯片、包含无源元件和 3D 结构。我们将此封装结构指定为“扇出芯片后封装 (FOCLP)”对于高端应用,我们将展示使用高密度基板工艺用于要求更高的芯片后扇出封装的能力关键词芯片先、芯片后、扇出、晶圆级封装

异构芯片集成打造超级芯片

本文介绍了一种新型超大面积集成电路 (ELAIC) 解决方案(我们称之为“巨型芯片”),适用于将不同类型的多个芯片(例如,内存、专用集成电路 [ASIC]、中央处理器 [CPU]、图形处理单元 [GPU]、电源调节)组合到通用互连平台上的单个封装中。巨型芯片方法有助于重新构建异构芯片平铺,以开发具有所需电路密度和性能的高度复杂系统。本文重点介绍了最近关于大面积超导集成电路连接多个单独芯片的研究,特别关注了在单个芯片之间形成的高密度电互连的处理。我们重新制造了各种巨型芯片组件,并使用多种技术(例如扫描电子显微镜 (SEM)、光学显微镜、共聚焦显微镜、X 射线)对其进行了表征,以研究集成质量、最小特征尺寸、硅含量、芯片间间距和间隙填充。二氧化硅、苯并环丁烯 (BCB)、环氧树脂、聚酰亚胺和硅基电介质用于间隙填充、通孔形成和重分布层 (RDL)。对于巨型芯片方法,通过减少芯片间 (D2D) 间隙和增加硅含量来提高热稳定性,从而使组装人员能够缓解不同基板/模块集成方案的热膨胀系数 (CTE) 不匹配的问题,这对于实现从回流到室温甚至低温操作的宽温度范围稳定性非常重要。 Megachip 技术有助于实现更节省空间的设计,并可容纳大多数异构芯片,而不会影响稳定性或引入 CTE 不匹配或翘曲。各种异构芯片

异构芯片集成打造超级芯片

D 集成是先进封装和异构集成中的关键技术——它有助于系统级性能扩展。虽然封装的发展引入了 3D 集成,从封装系统发展到堆叠集成电路 (IC) 和 3D 片上系统,但该行业目前正在见证另一个重要转折点:背面供电网络 (BSPDN)。在传统的扩展方法中,信号和供电共存于晶圆的正面。然而,对电力(尤其是供电)日益增长的需求,越来越限制了实现可扩展解决方案的能力。高效的晶体管扩展对于实现更高的晶体管密度至关重要,这需要按比例扩展供电网络。然而,这遇到了巨大的 IR 压降挑战,导致晶体管性能受损。此外,信号和电源的互连设计变得高度相互依赖,构成了供电布线过程的很大一部分(至少 20%)。此外,随着扩展到下一个节点,功率密度会迅速增加。行业共识是通过实施 BSPDN 来分离信号和电源。这涉及隔离晶圆正面的信号网络,并利用晶圆对晶圆键合来高效地访问晶体管背面以进行电源分配和管理。主要优势包括更宽的电源线和更低的 IR 压降、更均匀的电压分布,以及最重要的,更多的设计空间,从而进一步缩小标准单元高度。BSPDN 消除了在晶圆正面共享信号和电源线之间互连资源的需要。顾名思义,背面供电将电源重新定位到背面