XiaoMi-AI文件搜索系统

World File Search SystemCMOS 数字隔离器取代工业光耦合器...

CMOS 数字隔离器的基本操作类似于光耦合器,只是使用 RF 载波代替光(图 1b)。CMOS 数字隔离器由两个相同的半导体芯片组成,它们在标准 IC 封装内连接在一起,形成由差分电容隔离屏障隔开的 RF 发射器和接收器。数据使用简单的开关键控 (OOK) 从输入传输到输出。当 VIN 为高电平时,发射器生成 RF 载波,该载波通过隔离屏障传播到接收器。当检测到足够的带内载波能量时,接收器在 VOUT 上断言逻辑 1。当 VIN 为低电平时,发射器被禁用,并且不存在载波。因此,接收器未检测到带内载波能量并将 VOUT 驱动为低电平。

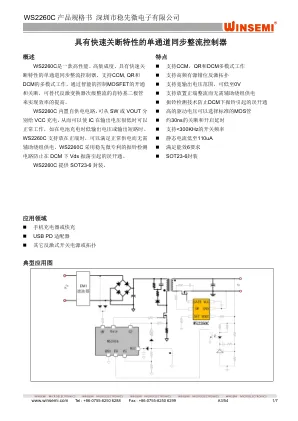

具有快速关断特性的单通道同步整流控制器

当同步整流管完全开启后, VDS 两端压降完全跟 随次级电流 Is 。随着次级续流电流的减小 VDS 电压升 高,当 VDS 电压增大到 -30mV 时, Gate 驱动电路的 上管供电被关断 , 驱动电压随内部电阻及漏电流开始缓 慢降低;当 VDS 电压增大到 -20mV 时, Gate 驱动电 压会被钳位在 3.3V 左右。如果 VDS 电压增大到 -1mV 时, WS2260C 会在 25ns 的时间内快速将 GATE 电压 拉到 0V 。同时,关断屏蔽时间开始计时,此期间 GATE 保持低电平。直到 VDS 电压大于 2V ,退出关断屏蔽 计时。

ICL7135-TME

当为高电平(或打开)时,A/D 将以每 40,002 个时钟脉冲等间隔的测量周期自由运行。如果为低电平,转换器将继续进行其正在进行的整个测量周期,然后在 R/H 保持低电平期间保持此读数。短正脉冲(大于 300 纳秒)现在将启动新的测量周期,从 1 到 10,001 个自动归零计数开始。如果脉冲在完成整个测量周期(40,002 个计数)之前发生,则不会识别该脉冲,转换器将仅完成其正在进行的测量。完成整个测量周期的外部指示是第一个选通脉冲(见下文)将在此周期结束后 101 个计数发生。因此,如果 Run/HOLD 为低,并且至少持续 101 次计数,则转换器处于保持状态,并准备在脉冲为高时开始新的测量。

ICL7135 - Farnell

当为高电平(或打开)时,A/D 将以每 40,002 个时钟脉冲等间隔的测量周期自由运行。如果为低电平,转换器将继续进行其正在进行的整个测量周期,然后在 R/H 保持低电平期间保持此读数。短正脉冲(大于 300 纳秒)现在将启动新的测量周期,从 1 到 10,001 个自动归零计数开始。如果脉冲在完成整个测量周期(40,002 个计数)之前发生,则不会识别该脉冲,转换器将仅完成其正在进行的测量。完成整个测量周期的外部指示是第一个选通脉冲(见下文)将在此周期结束后 101 个计数发生。因此,如果 Run/HOLD 为低,并且至少持续 101 次计数,则转换器处于保持状态,并准备在脉冲为高时开始新的测量。

MCP9804 - Microchip Technology

注 1:所有值均指 V IL MAX 和 V IH MIN 电平。2:如果 t LOW > t OUT 或 t HIGH > t OUT ,则温度传感器 I 2 C 接口将超时。通信需要重复启动命令。3:此设备可用于标准模式 I 2 C 总线系统,但必须满足要求 t SU:DI MIN。此设备不会延长 SCL 低电平时间。4:作为发送器,该设备提供内部最小延迟时间 t HD:DO MIN ,以桥接 SCL 下降沿 t F MAX 的未定义区域,以避免意外生成启动或停止条件。5:作为接收器,不应在 SCL 下降沿对 SDA 进行采样。SCL 切换为低电平后,SDA 可以转换 t HD:DI。6:I 2 C 快速模式规范或总线频率高达 400KHz 的时序适用于日期代码为 1145 的设备。

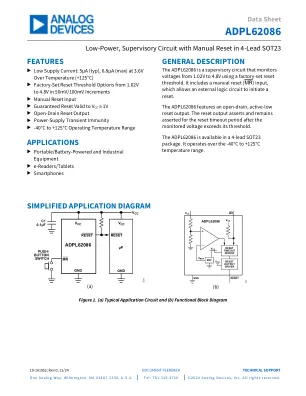

ADPL62086 | 数据表

手动复位输入 ( MR ) 许多基于微处理器 (μP) 的产品需要手动复位功能,允许操作员、测试技术人员或外部逻辑电路启动复位。MR 上的逻辑低电平可使复位有效。在 MR 为低电平期间以及在 MR 返回高电平后的复位有效超时周期 (t RP ) 或延迟 (t ON ) 内,复位保持有效。此输入具有内部 50kΩ 上拉电阻,因此如果不使用,可以保持悬空。MR 可以用 TTL 或 CMOS 逻辑电平驱动,也可以用开漏/集电极输出驱动。对于手动操作,将一个常开瞬时开关从 MR 连接到 GND;无需外部去抖动电路。如果 MR 由长电缆驱动,或者如果设备在嘈杂环境中使用,请将一个 0.1μF 电容从 MR 连接到地以提供额外的抗噪能力。

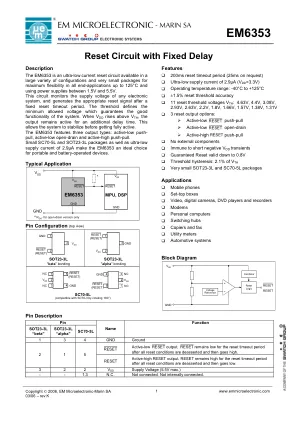

EM6353 - 带手动复位功能的复位电路

EM6353 是一款超低电流复位电路,具有多种配置和超小封装,可在高达 125°C 的所有终端应用中实现最大灵活性,电源电压为 1.5V 至 5.5V。该电路可监控任何电子系统的电源电压,并在固定的复位超时时间后生成适当的复位信号。阈值定义了允许的最低电压,可确保系统正常运行。当 V DD 升至 V TH 以上时,输出将保持有效状态一段时间。这可使系统在完全激活之前稳定下来。EM6353 具有三种输出类型:低电平有效推挽、低电平有效开漏和高电平有效推挽。小型 SC70-5L 和 SOT23-3L 封装以及 2.9µA 的超低电源电流使 EM6353 成为便携式和电池供电设备的理想选择。典型应用

绝对式编码器 ENA36IL-R***-SSI

SSI 输出格式 标准 • 空闲状态下,信号线“Data +”和“Clock +”处于高电平 (5 V)。 • 时钟信号首次从高电平切换到低电平时,开始传输数据,其中当前信息(位置数据 (D n ) 和特殊位 (S))存储在编码器中。 ± • 最高位 (MSB) 通过第一个脉冲上升沿应用于编码器的串行数据输出。 • 下一个连续的低位通过每个后续的脉冲上升沿传输。 • 传输最低位 (LSB) 后,数据线切换到低电平,直到单稳态触发器时间 T m 到期。 • 直到数据线再次切换到高电平或时钟暂停时间 T p 到期,才能开始后续数据传输。 • 时钟序列完成后,单稳态触发器时间 T m 通过最后一个脉冲下降沿触发。 • 单稳态触发器时间 T m 决定最低传输频率。

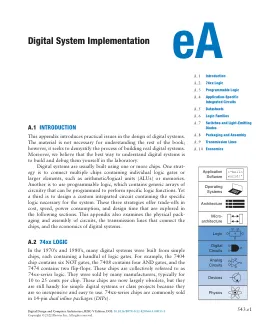

数字系统实施 - Elsevier

图 eA.1 显示了包含基本逻辑门的各种流行 74xx 系列芯片的引脚分布图。这些有时被称为小规模集成 (SSI) 芯片,因为它们由几个晶体管构成。14 针封装通常在顶部有一个凹口或在左上角有一个点来指示方向。引脚编号从左上角的 1 开始,沿封装逆时针方向排列。芯片需要分别在引脚 14 和 7 处接收电源 (V DD = 5 V) 和接地 (GND = 0 V)。芯片上的逻辑门数量由引脚数量决定。请注意,7421 芯片的引脚 3 和 11 未连接 (NC) 任何东西。7474 触发器具有常见的 D 、 CLK 和 Q 端子。它还具有互补输出 Q 。此外,它还接收异步设置(也称为预设或 PRE )和重置(也称为清除或 CLR )信号。这些都是低电平有效;换句话说,触发器在 PRE = 0 时设置,在 CLR = 0 时重置,在 PRE CLR = = 1 时正常运行。低电平有效

DAC5688 - 德州仪器

传输使能输入。内部下拉。TXENABLE 有两个用途。在所有模式下,TXENABLE 必须为高电平,才能启用 DAC 的 DATA。当 TXENABLE 为低电平时,数字逻辑部分被强制为全 0,并且任何输入数据都被忽略。在交错数据模式下,TXENABLE 可用于将数据同步到通道 A 和 B。第一个 A 通道样本应与 TXENABLE 的上升沿对齐。