XiaoMi-AI文件搜索系统

World File Search System研究文章有效地设计了QCA全贴纸,低功耗

对高性能和能量计算系统的连续市场需求已将计算范式和技术转向纳米级量子量子点蜂窝自动机(QCA)。在本文中,已经提出了新型的能量和有效的基于QCA的加法器/减法器设计。首先,设计了一个基于QCA的3输入XOR门,然后实现了完整的加法器和完整的减法器。通过QCAPRO估计器工具在开尔文温度t 2上通过不同类型的能量(C 0.5 EK,C 1.0 EK和C 1.5 EK)测试了所提出的设计的功耗。qcadesigner 2.0.03软件用于评估所提出设计的仿真结果。在细胞数,区域和功率耗散方面,提出的设计比常规设计具有更好的复杂性。

教育技术团队教学: -

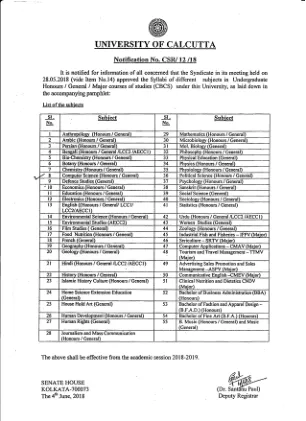

CMS-A-CC-1-1-TH:数字逻辑核心课程1:理论:04学分:60小时集成电路:(5小时)双极逻辑系列:DTL,TTL Not Gate,TTL NAND NAND NAND GATE,TTL NAND NON GATE,TTL NON GATE,TTL NOR GATE,TTL NON GATE,OPEN COLLECTOR,FANOR,fan-in-fan-in,fan,Out; MOS Logic Families: NMOS, PMOS, CMOS, SSI, MSI, LSI and VLSI classification Number Systems : (5 hours) Weighted and Non-Weighted Codes, positional, Binary, Octal, Hexadecimal, Binary coded Decimal (BCD), Gray Codes, Alphanumeric codes, ASCII, EBCDIC, Conversion of bases, Parity bits, Single Error bit detection and校正代码:锤击代码,固定和浮点算术:加法,减法,乘法和除法。Boolean Algebra: (8 hours) Fundamentals of Boolean Expression: Definition of Switching Algebra, Basic properties of Switching Algebra, Huntington's Postulates, Basic logic gates (AND, OR, NOT), De- Morgan's Theorem, Universal Logic gates (NAND, NOR), Minterm, Maxterm, Minimization of Boolean Functions using K-Map up-to four variables, Two level and multilevel使用逻辑门实现,简化逻辑表达式。组合电路:(20小时)一半加法器,完整加法器(3位),半减法器,全部减法器(3位)以及使用基本逻辑大门(OR和,不是)和通用逻辑门(NAND&NOR)(NAND&NOR),Multibit Adder-ripple-ripp-ripp-cruction-nourter corral and and and and and bcd aDder,bcd adder a adder a adder a dractor bcd adder a adder a dracter,bcd adder a adder,1 and and and and and and and bcd adder a adder a adder a adder,1 1位,2位,3位和4位比较器使用基本逻辑门。数据选择器 - 多工器:扩展(级联),还原,功能实现,通用函数实现,多功能实现。

辅修课程

课程先决条件:基础电气科学。课程目标:了解数字系统的工作原理。应更深入地研究数字逻辑/计算机的各种硬件组件。课程成果 (CO): CO1:应用布尔代数和卡诺图简化数字逻辑电路。CO2:设计和实现基本组合电路,如加法器、减法器、比较器、解码器、编码器、多路复用器和解复用器。CO3:分析各种触发器(SR、D、JK 和 T)的行为并设计顺序电路,如计数器、移位寄存器和序列检测器。CO4:使用状态图和表表示的状态机对数字系统进行建模,并执行状态最小化以实现高效设计。CO5:了解逻辑系列(例如 ECL、CMOS)的原理并使用硬件描述语言(Verilog/VHDL)进行数字系统建模。

R19 技术硕士十/十

高级数字系统设计 (PC – I) 单元 - I 处理器算法:二进制补码系统 - 算术运算;定点数系统;浮点数系统 - IEEE 754 格式,基本二进制代码。单元 - II 组合电路:CMOS 逻辑设计,组合电路的静态和动态分析,时序风险。功能块:解码器、编码器、三态设备、多路复用器、奇偶校验电路、比较器、加法器、减法器、进位超前加法器 - 时序分析。组合乘法器结构。单元 - III 序贯逻辑 - 锁存器和触发器,序贯逻辑电路 - 时序分析(建立和保持时间),状态机 - Mealy & Moore 机,分析,使用 D 触发器的 FSM 设计,FSM 优化和分区;同步器和亚稳态。 FSM 设计示例:自动售货机、交通信号灯控制器、洗衣机。单元 - IV 使用功能块进行子系统设计 (1) - 设计(包括时序分析)不同复杂程度的不同逻辑块,主要涉及组合电路:

R18 B.Tech。 EEE教学大纲Jntu Hyderabad 1

高级数字系统设计(PC - I)单元 - I处理器算术:Two的补体编号系统 - 算术操作;固定点号系统;浮点数系统 - IEEE 754格式,基本二进制代码。单元-II组合电路:CMOS逻辑设计,组合电路的静态和动态分析,时机危害。功能块:解码器,编码器,三态设备,多路复用器,奇偶校验电路,比较器,加法器,减法器,随身携带的浏览器 - 定时分析。组合乘数结构。单位-III顺序逻辑 - 锁存和触发器,顺序逻辑电路 - 时序分析(设置和保持时间),状态机 - Mealy&Moore机器,分析,使用D触发器,FSM设计,FSM设计,FSM优化和分区;同步器和标准化。FSM设计示例:自动售货机,交通信号灯控制器,洗衣机。单元 - IV子系统设计使用功能块(1) - 设计(包括时间分析)的不同逻辑块的不同复杂性的不同逻辑块,主要涉及组合电路:

Fredkin CSWAP 量子门的设计

Fredkin 门以物理学家 Edward Fredkin 的名字命名,他引入了可逆计算的概念,并为可逆逻辑门的发展做出了贡献。可逆门在量子计算中非常重要,因为它们可以保存信息,因此可用于构建信息不能丢失的量子电路。Fredkin 门,也称为受控交换 (CSWAP) 门,是量子计算和可逆计算中的三位可逆门。它对三位执行受控交换操作。如果第一位(控制位)设置为 1,Fredkin 门会交换第二位和第三位,如果控制位为 0,则保持不变。可逆逻辑也称为信息无损逻辑,因为嵌入在电路中的信息如果丢失可以恢复。人们设计和发明了许多可逆门。例如 Fredkin 门、Toffoli 门、Peres 门和 Feynman 门。可逆逻辑具有广泛的应用,被认为是未来技术之一。但逻辑电路设计基于不可逆的逻辑门。这些逻辑门有助于未来实现更高端的电路。本文尝试使用可逆门设计逻辑门,并设计了一些高端电路,例如二进制到灰度、灰度到二进制、加法器、减法器等。

使用CNTFET的高速低功率4位ALU设计

摘要 - 由于电子半导体部门经历了缩小规模,因此存在许多挑战,包括缩放,短通道影响,泄漏电流和稳定性。碳纳米管(CNT)已成为一种令人兴奋的新发明,可以克服CMO的局限性,同时保持高效率和可靠性。算术和逻辑单元(ALU)是微处理器和实时计算机芯片中存在的中央操作可编程逻辑组件。传统的算术逻辑单元(ALUS)是利用CMOS技术创建的,导致高功率使用,延迟以及晶体管计数。本文专门讨论了采用碳纳米管现场效应晶体管(CNTFET)的混合算术逻辑单元(ALU)的概念化和开发。首先,开发了XOR和MUX的组合,然后将其用于创建混合加法器和减法器。该研究展示了利用碳纳米管(CNT)技术的增强算术逻辑单元(ALU)的开发,模拟和评估,并将其与使用32 NM技术节点进行了将其与传统的CMOS实施进行了比较。使用碳纳米管(CNT)技术的ALU在功率使用情况,传播延迟和功率 - 延迟产品(PDP)方面的性能较高,而与CMOS技术相比。

典型的 PIC 微控制器

2.1 74LS00 四路 2-I/P NAND 封装。.....................18 2.2 输出结构。.........................................19 2.3 开路集电极缓冲器驱动共用线路。..。。。。。。。。。。。。。。。。20 2.4 共享总线。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。.................20 2.5 74LS138 和 ’139 MSI 自然解码器。..................21 2.6 74LS688八进制相等检测器。..........。。。。。。。。。。。。。。23 2.7 加法。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。....24 2.8 实现可编程加法器/减法器。 div>............25 2.9 74LS382 ALU。< /div>....。。。。。。。。。。。。。。。。。。。。。。。。...... div>........25 2.10 ROM 实现的 1 位加法器。............. div>............. . 26 2.11 2764 可擦除 PROM。 . 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 . . . . . . div> . . . . 27 2.12 浮栅 MOSFET 链接 . < div> 。 。..26 2.11 2764 可擦除 PROM。.。。。。。。。。。。。。。。。。。。。。。。。。...... div>....27 2.12 浮栅 MOSFET 链接 .< div> 。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。27 2.13 RS锁存器...。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。29 2.14 使用 RS 锁存器对开关进行去抖处理。。。。。。。。。。。。。。。。。。。。。。。30 2.15 D锁存器和触发器。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。31 2.16 74LS74 双 D 触发器。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。32 2.17 74LS377 八进制 D 触发器阵列。。。。。。.....................33 2.18 74LS373八进制D锁存器阵列。..。。。。。。。。。。。。。。。。。。。。。。。。..34 2.19 8位ALU累加器处理器。.................。。。。35 2.20 SISO 移位寄存器。。。。。。。。。。。。。。。。。。。.....................36 2.21 T 触发器。....。。。。。。。。。。。。。。。。。。。。。。。。...................36 2.22 模 16 波纹计数器。...。。。。。。。。。。。。。。。...............37 2.23 生成时序波形。........。。。。。。。。。。。。。。。。。。。。。。38 2.24 6264 8196 × 8 RAM。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。39

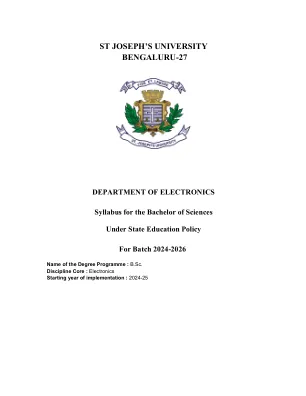

电子产品

单元 1:放大器 16 小时 多级放大器:多级放大器的需求和使用、总增益、级联与共源共栅。RC 耦合放大器。达林顿放大器 - 电路、电流增益、Zi、Zo、优点。功率放大器:电压与功率放大器、功率放大器的需求、分类 A 类、C 类(仅提及)B 类:推挽放大器、工作、效率(推导)、交叉失真、谐波失真、互补对称(无变压器)。比较。调谐放大器:需要单调谐和双调谐、工作、频率响应曲线、优点和缺点、耦合说明。JFET - 类型 - p 沟道和 n 沟道、工作和 IV 特性 - n 沟道 JFET、参数及其关系、BJT 和 JFET 的比较。共源放大器、MOSFET:E&D、MOSFET – n 沟道和 p 沟道、构造、工作、符号、偏置、漏极和传输特性、CMOS 逻辑、CMOS 反相器 - 电路、工作和特性。单元 2:反馈放大器和振荡器 10 小时反馈:反馈类型正反馈和负反馈、框图、反馈对 Av、BW、Zi 和 Zo 的影响(仅适用于电压串联反馈放大器电路)。振荡器的需求;正反馈、储能电路 – 振荡、谐振频率。巴克豪森振荡准则、LC 调谐振荡器 - Colpitts 和 Hartley 振荡器、振荡频率(无推导)、最小增益、优点和缺点、RC 振荡器 - 相移和 Wein 桥振荡器(无推导)、频率和最小增益、晶体振荡器、压电效应、等效电路、串联和并联谐振电路、Q 因子。非正弦振荡器:非稳态多谐振荡器,工作波形,频率公式(仅提及),单稳态多谐振荡器,双稳态多谐振荡器(触发器概念)。 单元 3:集成电路 04 小时 IC555 框图和引脚图。 IC555 应用 - 非稳态(推导)和单稳态多谐振荡器,压控振荡器。 施密特触发器。 IC 稳压器:LM317,IC78XX,79XX 系列(框图) 单元 4:运算放大器(Op-Amp) - 理论与应用 11 小时 Op-Amp 框图,引脚图 IC741,规格,理想和实际运算放大器参数的特性 - 输入偏置电流,输入失调电压,输出失调电压,CMRR,斜率 SVRR,失调零,开环运算放大器限制,闭环运算放大器。负串联反馈放大器的框图,反相和非反相反馈电路,增益,R if ,R of 。虚拟接地,单位增益带宽积。应用:加法器 - 反相和非反相,减法器,比例变换器,缓冲器,积分器,微分器(理想和实用)。比较器,过零检测器,有源滤波器 - 巴特沃斯一阶低通、高通、带通、带阻、全通滤波器。二阶滤波器(仅提及)。自学:04 小时 IC 制造技术。推荐教科书 1、运算放大器和线性电路,Ramakanth Gayakwad PHI,第 5 版,2015 年。2. 应用电子学教科书,RS Sedha

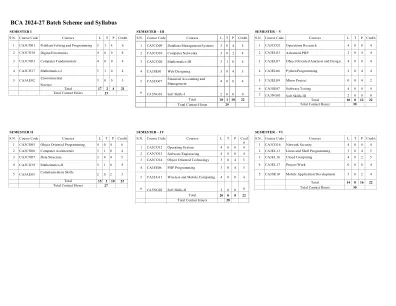

BCA 2024-27批处理方案和教学大纲

单元数系统系统:二进制,八进制,十六进制,从一个碱基到另一个碱基的转换,二进制算术,未签名的二进制数,签名的幅度数,2的补体表示,2的补充算术。ASCII代码,BCD代码,EBCDIC代码,多余的代码和灰色代码。算术电路:加法器,减法器,二进制乘数和分隔线。单元II逻辑门:不,或,或,或,或,或,或者,或者,nor,ex-Or和ex-nor Gates,二极管和晶体管作为开关。 布尔代数:布尔代数的定律,逻辑大门,使用k-映射对布尔方程的简化。 单元III组合电路:多路复用器,弹能器及其用作逻辑元素,解码器。 加法器/字样。 编码器,解码器触发器:S-R- J-K。 T. D,时钟的触发器,围绕状态竞争,主人触发器。 单元IV位移登记册:串行串行,并行序列,并行串行和平行 - 外向,双向移位寄存器。 计数器:异步和同步戒指计数器和约翰逊计数器,Tristate Logic。 a/d和d/a转换器:采样并保持电路。 单元-V内存:内存单元格,主内存 - RAM,ROM,PROM,EPROM,EPROM,EEPROM,CACHE内存,闪存存储器,DDR,DDR,辅助内存及其类型,物理内存和虚拟内存的介绍,内存访问方法:串行和随机访问。 教科书:数字原理和应用,Malvino&Leach,McGraw Hill。 数字集成电子产品,Taub&Schilling,MGH Thomas C Bartee,数字计算机基础,MacGrawhill参考:R.P.单元II逻辑门:不,或,或,或,或,或,或者,或者,nor,ex-Or和ex-nor Gates,二极管和晶体管作为开关。布尔代数:布尔代数的定律,逻辑大门,使用k-映射对布尔方程的简化。单元III组合电路:多路复用器,弹能器及其用作逻辑元素,解码器。加法器/字样。编码器,解码器触发器:S-R- J-K。 T. D,时钟的触发器,围绕状态竞争,主人触发器。单元IV位移登记册:串行串行,并行序列,并行串行和平行 - 外向,双向移位寄存器。计数器:异步和同步戒指计数器和约翰逊计数器,Tristate Logic。a/d和d/a转换器:采样并保持电路。单元-V内存:内存单元格,主内存 - RAM,ROM,PROM,EPROM,EPROM,EEPROM,CACHE内存,闪存存储器,DDR,DDR,辅助内存及其类型,物理内存和虚拟内存的介绍,内存访问方法:串行和随机访问。教科书:数字原理和应用,Malvino&Leach,McGraw Hill。数字集成电子产品,Taub&Schilling,MGH Thomas C Bartee,数字计算机基础,MacGrawhill参考:R.P.Jain,数字电子产品,麦格劳山莫里斯·马诺(McGraw Hill Morris Mano),数字设计,Phi Gothmann,数字电子,Phi Tocci,数字系统原理和应用,Pearson Education Asia Asia Asia Donald D Givone,数字原理和设计,TMH