XiaoMi-AI文件搜索系统

World File Search System采用 TiO2 模板原子层沉积技术在金刚石膜上制备高 Q 纳米光子谐振器

电子束光刻:根据应用,将电子束光刻胶 (950K PMMA A4,MicroChem) 旋涂至 270 nm-330 nm 的厚度。接下来,在顶部热蒸发 20 nm Au 的导电层,以避免光刻过程中电荷积聚。为了进一步减轻充电效应,我们使用了相对较低的束电流 (0.3 nA)、多通道曝光 (GenISys BEAMER) 和减少电子束在一个区域持续停留时间的写入顺序。光刻胶的总曝光剂量为 1200 uC/cm2,电压为 100 kV (Raith EBPG5000 plus)。曝光后,我们用 TFA 金蚀刻剂 (Transene) 去除导电层,并在 7 C 的冷板上将光刻胶置于 1:3 MIBK:IPA 溶液中显影 90 秒,然后用 IPA 封堵 60 秒,再用 DI 水冲洗。原子层沉积:在进行 ALD 之前,我们在 ICP RIE 工具 (PlasmaTherm Apex) 中使用 10 sccm O2 和 50 W ICP 功率进行三秒等离子曝光,以去除残留聚合物。使用此配方,PMMA 蚀刻速率约为 2.5 nm/s。对于 TiO 2 沉积,我们使用商用热 ALD 室 (Veeco/Cambridge Savannah ALD)。使用四(二甲酰胺)钛 (TDMAT) 和水在 90 C 下沉积非晶态 TiO 2,交替脉冲分别为 0.08 秒和 0.10 秒。沉积期间连续流动 100 sccm N 2,前体脉冲之间的等待时间为 8 秒。沉积速率通常为 0.6 A/循环。 ICP 蚀刻程序:我们通过氯基 ICP RIE 蚀刻(PlasmaTherm Apex)去除过填充的 TiO 2,基板偏压为 150 W,ICP 功率为 400 W,Cl 2 为 12 sccm,BCl 为 8 sccm。蚀刻速率通常为 1.5-1.7 nm/s。SEM 成像:在 5 nm Cr 导电层热沉积后,使用 Carl Zeiss Merlin FE-SEM 对纳米光子结构进行成像。FDTD 模拟:使用 Lumerical 有限差分时域软件模拟环形谐振器、光子晶体腔和光栅耦合器。透射光谱:我们使用自制的共焦显微镜装置,该装置具有独立的收集和激发通道,以进行透射光谱。脉冲超连续源 (430-2400 nm,SC-OEM YSL Photonics) 和光谱仪 (1200 g/mm,Princeton Instruments) 用于宽带测量。为了对单个腔体谐振进行高分辨率扫描,我们使用 50 kHz 线宽、可调 CW 激光器 (MSquared) 进行激发,并使用雪崩光电二极管 (Excelitas) 进行检测。金刚石膜:通过离子轰击 34 生成 500 nm 厚的金刚石膜,并在阿贡国家实验室通过化学气相沉积进行覆盖。在对离子损伤层进行电化学蚀刻后,去除悬浮膜并用 PDMS 印章翻转。然后使用 ~500 nm 的 HSQ 抗蚀剂将它们粘附到 Si 载体上,并在氩气中以 420 C 的温度退火 8 小时。最后,使用 ICP 蚀刻法将膜蚀刻至所需厚度,蚀刻气体为 25 sccm Ar、40 sccm Cl2、400 W ICP 功率和 250 W 偏压功率。蚀刻速率通常为 1.2-1.4nm/s。

利用高通量原子层沉积工艺降低锂离子电池制造成本和能耗

该项目将在三个预算期 (BP) 内完成,每个 BP 之间都有一个通过/不通过决策点。此 NEPA 审查适用于所有三个 BP 中的工作活动。在 BP1 期间,将采购 R2R 工具并进行安装规划。将开发和表征新涂层。然后将合成、涂覆和测试隔膜。将使用现有的批量 ALD 系统进行涂层。将选出性能最佳的涂层进行进一步测试。BP2 活动将包括 R2R 工具安装、隔膜合成和使用 R2R ALD 系统进行涂层。将在涂层隔膜上进行性能测试。还将进行初步技术经济分析 (TEA)。BP3 活动将包括电池制造、隔膜和电池单元的性能测试、与现有商用电池堆垛机在线演示 R2R ALD 涂层系统以及完成 TEA。

通过分子层沉积生长的具有双芳香族连接体的 MOF 薄膜

反应室,使其与之前的表面反应至饱和。在新的清洗步骤之后,以循环方式重复该过程,直到获得所需厚度。由于每个脉冲的自限制生长,每个脉冲只能将每种前驱体最多一个单层添加到基板上。当前驱体是成为薄膜一部分的较大有机分子时,通常将该过程称为分子层沉积 (MLD),16 我们的研究就是这种情况。MLD 技术可用于制备有机薄膜或有机 - 无机混合薄膜,以用于 Meng 等人在综述文章中总结的广泛应用。 17 最近的文献中出现了一些使用 MLD 制备 MOF 薄膜的例子,18 – 21 例如 UiO-66 生长的演示,22 以及具有氨基功能化连接体的类似 MOF 结构的生长。23

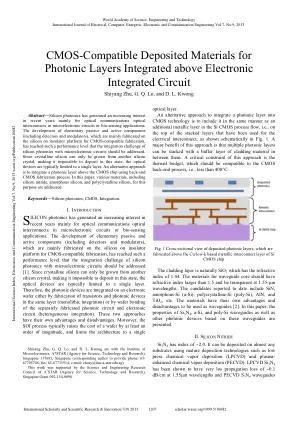

用于集成在电子集成电路上方的光子层的 CMOS 兼容沉积材料

摘要 — 近年来,硅光子学引起了越来越多的关注,主要用于微电子电路或生物传感应用中的光通信光互连。主要在绝缘体上硅平台上制造的用于 CMOS 兼容制造的基本无源和有源元件(包括探测器和调制器)的开发已达到如此高的性能水平,以至于应该解决硅光子学与微电子电路的集成挑战。由于晶体硅只能从另一个硅晶体中生长,因此无法在这种状态下沉积,因此光学器件通常仅限于单层。另一种方法是使用后端 CMOS 制造工艺在 CMOS 芯片上方集成光子层。本文讨论了用于此目的的各种材料,包括氮化硅、非晶硅和多晶硅。关键词 — 硅光子学、CMOS、集成。

天然洞穴中的 μ 子层析成像实验

lászlóOláhLászlóOláhG。G. G. G. G.Barnaföld,G。Bencédi,G。Hamar,G。Hamar,H。Féleh,G。Surányi,D。VargaG. G. G. G. G. G. G. G. G. G. G.Barnaföld,G。Bencédi,G。Bencédi,G。Hamar,G。Hamar,H.Féleh,G。Féleh,G。Varganyi,Div>

以液态铜(I)酰胺前驱体为原料,原子层沉积超薄铜金属膜

我们报道了一种通过原子层沉积 ALD 在长宽比超过 35:1 的非常窄的孔内共形生产薄的、完全连续且高导电性的铜膜的方法。纯铜薄膜由新型铜 I 脒基前体、铜 IN、N -二仲丁基乙脒和分子氢作为还原剂生长。该铜前体在汽化过程中为液态,因为其熔点 77°C 低于其汽化温度 90-120°C 。因此,前体蒸汽的传输非常可重复且可控。碳和氧杂质低于 1 原子%。每个循环的生长在 SiO 2 或 Si 3 N 4 表面上为 1.5-2 Å/循环,但在金属 Ru、Cu 和 Co 表面上仅为 0.1-0.5 Å/循环。在氧化物表面,铜原子形成孤立的铜晶体,经过更多沉积循环后合并为粗糙的多晶膜。在 Ru 和 Co 金属表面上,ALD Cu 密集成核,形成光滑且附着力强的薄膜,即使对于薄至 4 个原子层的薄膜,这些薄膜也是连续的。在 2 nm Ru 基底上沉积 4 nm Cu 时,薄层电阻低于 50 / ,这足以制作用于电镀 Cu 互连线的种子层。© 2006 电化学学会。DOI:10.1149/1.2338632 保留所有权利。