XiaoMi-AI文件搜索系统

World File Search System人工智能在预测和预防高风险环境中汽车故障中的作用

人工智能模仿人类智能,用于预测和预防关键的汽车故障。这些故障通常发生在测试情况下,可能很危险。了解组件行为对于实施有效的故障防御措施至关重要。目前,预测随机组件故障具有挑战性。人工智能通过智能模拟真实世界条件来实现预测性故障模拟。通过将模拟的组件行为与实际数据进行比较,可以实现故障预测。这对于维护和备件供应计划非常有价值。汽车系统中的人工智能技术正在不断发展,对于解决当前问题和防止未来故障至关重要。模拟和预防性维护对于了解系统行为和防止故障至关重要。

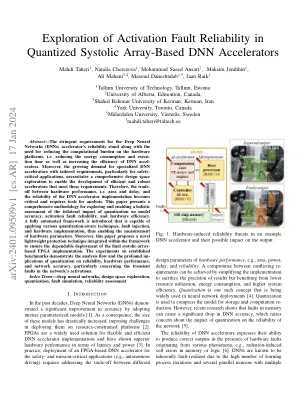

量化脉动阵列 DNN 加速器中激活故障可靠性的探索

摘要 — 深度神经网络 (DNN) 加速器可靠性的严格要求与减少硬件平台计算负担的需求相伴而生,即降低能耗和执行时间以及提高 DNN 加速器的效率。此外,对具有定制要求的专用 DNN 加速器的需求不断增长,特别是对于安全关键型应用,这需要进行全面的设计空间探索,以开发出满足这些要求的高效且强大的加速器。因此,硬件性能(即面积和延迟)与 DNN 加速器实现的可靠性之间的权衡变得至关重要,需要分析工具。本文提出了一种全面的方法来探索和实现对量化对模型精度、激活故障可靠性和硬件效率的三方影响的整体评估。介绍了一个完全自动化的框架,该框架能够应用各种量化感知技术、故障注入和硬件实现,从而实现硬件参数的测量。此外,本文提出了一种集成在框架内的新型轻量级保护技术,以确保最终基于脉动阵列的 FPGA 实现的可靠部署。在已建立的基准上进行的实验展示了分析流程以及量化对可靠性、硬件性能和网络准确性的深远影响,特别是关于网络激活中的瞬态故障。索引术语 — 深度神经网络、设计空间探索、量化、故障模拟、可靠性评估

针对基于 FPGA 的设计的周期精确软错误漏洞分析框架

摘要 — 许多航空航天和汽车应用在其设计中使用 FPGA,因为它们具有低功耗和可重构性要求。同时,此类应用对系统可靠性也提出了很高的标准,这使得基于 FPGA 的设计的早期可靠性分析变得非常关键。在本文中,我们提出了一个框架,可以快速准确地对基于小型 FPGA 的设计进行软错误漏洞的早期分析。我们的框架首先从 FPGA 设计中提取综合后网表。然后,它使用我们提出的接口软件将位翻转配置故障插入到设计网表中。之后,它将网表的黄金副本和故障副本无缝地输入到开源模拟器 Verilator 中,以进行周期精确仿真。最后,它生成原始设计的漏洞得分直方图以指导可靠性分析。实验结果表明,在 ITC'99 基准上分析注入的位翻转故障时,我们的框架比具有周期级精度的 Xilinx Vivado 故障模拟运行速度快 53 倍。索引词——FPGA、可靠性、CAD 框架、软错误。

跨域模拟故障注入用于设计稳健智能系统

摘要 — 在工业 4.0 革命的压力下,以及现在的《欧洲芯片法案》,智能系统在所有工业领域(例如汽车和航空航天)中无处不在。此类系统包含属于多个物理域(例如电气和机械)的数字和模拟组件。为了确保稳健性,必须在开发周期的早期验证整个系统,并考虑所有这些域,正如 ISO 26262 标准对汽车系统等情况所建议的那样。不幸的是,包括故障注入和模拟在内的验证技术在模拟方面并不像数字方面那么先进:i) 它们没有完全标准化 ii) 它们高度依赖于领域,并且 iii) 它们与数字流分开执行。本文提出通过在多个物理域中进行模拟故障注入来生成故障场景,从而改进智能系统的设计。通过利用这些故障场景,可以提高模拟部分的稳健性,同时提高控制系统功能的数字部分的质量。介绍了一个包含微控制器和三轴加速度计的多领域案例研究,以证明所提方法在许多工业环境中的有效性。索引术语——故障模拟、设计自动化、设计稳健性、多领域模拟。

ZuSE-KI-Mobile AI 加速器 SoC

摘要 —ZuSE-KI-Mobil (ZuKIMo) 是一个国家资助的研究项目,目前处于中期阶段。ZuKIMo 项目的目标是开发一个新的片上系统 (SoC) 平台和相应的生态系统,以实现具有特定要求的高效人工智能 (AI) 应用。借助 ZuKIMo,我们专门针对移动领域的应用,即自动驾驶汽车和无人机。初始生态系统由来自德国学术界和工业界的七个合作伙伴组成的联盟建立。我们围绕一种新颖的 AI 加速器设计开发 SoC 平台及其生态系统。可定制的加速器从头开始构思,以满足雄心勃勃的用例所产生的功能和非功能性要求。计划于 2023 年采用 22 nm FDX 技术进行流片。除了片上系统硬件设计本身之外,ZuKIMo 生态系统还旨在提供软件工具,以便轻松部署新用例和硬件-CNN 协同设计。此外,在安全关键型应用(如我们的移动用例)中,AI 加速器必须满足安全要求。因此,我们研究了用于深度神经网络 (DNN) 故障分析的新设计方法,并介绍了我们用于 AI 加速器的新冗余机制。索引术语 — 片上系统、AI 加速器、开发方法、故障模拟、功能安全

年度报告 - TIMA 实验室 - 格勒诺布尔阿尔卑斯大学

稳健性和可靠性 许多领域在经典的设计约束列表中都具有功能安全性,例如汽车领域的 ISO 26262 标准。我们的工作旨在改进对可靠性的早期评估。环境干扰引起的错误。目标是降低开发和生产成本,能够在设计的早期阶段准确评估软错误和永久错误的潜在功能影响。我们最近提出了一种跨层故障模拟方法来执行关键嵌入式系统的稳健性评估,该方法基于事务级模型 (TLM) 和寄存器传输级 (RTL) 描述中的故障注入,以在模拟时间和模拟高级故障行为的真实性之间进行权衡。该方法的另一个重要特征是考虑全局系统规范,以便区分实际的关键故障和导致对系统行为没有实际影响的故障。该方法已应用于机载案例研究。2021 年,该方法通过迭代流程得到改进,既可以全局减少故障注入持续时间,又可以随着迭代改进 TLM 模型,从而实现在 TLM 和 RTL 级别注入故障的后果之间的良好相关性。2021 年开始的另一项研究旨在更好地评估(和预测)软件工作负载对微控制器和 SoC 等复杂数字组件可靠性的影响。最终,一个目标是定义一组代表性基准,以便在实际应用程序可用之前对关键系统进行可靠性评估。第一步是开发一种基于适用于多种处理器的虚拟平台的多功能分析工具,与 QEMU 的修改版本相对应。该分析流程已应用于 RISC-V 目标和 Mibench 软件,使我们能够更好地了解软件负载对 SoC 容错的影响。我们提出的指标“似然百分比”表明,使用我们的工具进行高级评估可以非常有效地获得有关程序行为的重要信息,与从参考指令集模拟器和硬件架构获得的结果一致。我们还表明,我们的分析工具使我们能够比较多个程序的行为并表现出特定的特征。主要目标是在 SoC 设计领域传输和应用 RAMS 方法和工具。这些数据有助于理解处理器架构将如何用于每个应用程序,从而了解根据软件负载可以预期的容错级别。我们提出了三个假设,这些假设必须通过更多的程序示例、多个硬件平台的使用以及最终在粒子束下的实际测试来证实。在自动质量或安全保证水平评估领域,我们提出了第一种方法,用于自动提取片上系统内有效和故障状态机的过程。通过此方法自动提取的数据是行为建模和 FMEA(故障模式和影响分析)分析的相关输入。该方法基于一种半自动化方法,用于在单粒子翻转 (SEU) 或触发器卡住的假设下系统地提取数字设计的故障模式。此过程旨在增强人为故障分析,并在复杂设备的质量保证过程中为 RAMS(可靠性、可用性、可维护性和安全性)框架提供输入。已经在 I2C - AHB 系统上进行了实验结果,为对整个 SoC [CI3] 进行完整且更复杂的分析奠定了基础。 由于技术规模扩大和晶体管尺寸越来越小并更接近原子尺寸,上一代 CMOS 技术在各种物理参数中呈现出更多的可变性。此外,电路磨损退化会导致额外的时间变化,可能导致时序和功能故障。为了处理此类问题,一种传统方法是在设计时提供更多的安全裕度(也称为保护带)。因此,使用延迟违规监视器成为必须。放置监视器是一项关键任务,因为设计师必须仔细选择最容易老化且可能成为给定设计中潜在故障点的位置。