XiaoMi-AI文件搜索系统

World File Search System数字系统实施 - Elsevier

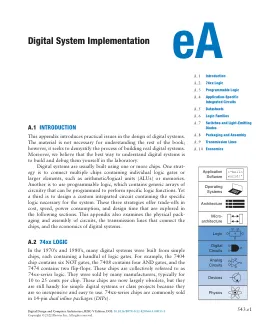

图 eA.1 显示了包含基本逻辑门的各种流行 74xx 系列芯片的引脚分布图。这些有时被称为小规模集成 (SSI) 芯片,因为它们由几个晶体管构成。14 针封装通常在顶部有一个凹口或在左上角有一个点来指示方向。引脚编号从左上角的 1 开始,沿封装逆时针方向排列。芯片需要分别在引脚 14 和 7 处接收电源 (V DD = 5 V) 和接地 (GND = 0 V)。芯片上的逻辑门数量由引脚数量决定。请注意,7421 芯片的引脚 3 和 11 未连接 (NC) 任何东西。7474 触发器具有常见的 D 、 CLK 和 Q 端子。它还具有互补输出 Q 。此外,它还接收异步设置(也称为预设或 PRE )和重置(也称为清除或 CLR )信号。这些都是低电平有效;换句话说,触发器在 PRE = 0 时设置,在 CLR = 0 时重置,在 PRE CLR = = 1 时正常运行。低电平有效

数字系统II-理工学院

3.6。 div>RS232,RS422和RS485。 div>4。编程。 div>4.1。 div>结构化编程。 div>4.2。 div>汇编语言。 div>4.3。 div>语言C. 5。其他微控制器。 div>5.1。 div>PIC 16F877。 div>5.2。 div>64HC11。 div>5.3。 div>AT89S8252。 div>6。实时系统简介。 div>6.1。 div>实时定义(实时)。 div>6.2。 div>实时系统的示例。 div>6.3。 div>实时设计设计技术。 div>6.4。 div>操作系统简介。 div>6.5。 div><实时内核。 div>7。<实时内核。 div>7.1。 div>调查的循环系统。 div>7.2。 div>由中断管理的系统。 div>7.3。 div>缓冲数据。 div>7.4。 div>邮箱。 div>7.5。 div><消息的发言人。 div>7.6。 div>交通信号灯。 div>7.7。 div>关键区域。 div>7.8。 div>事件标志。 div>7.9。 div>内存管理。 div>7.10。 div>任务管理。 div>7.11。 div>时间管理。 div>8。带有微控制器的项目。 div>

数字系统中聚合的设计框架...

该方法首先分析物理系统复杂性,以确定与管理复杂性相关的关键需求。然后引入合适的需求分类,以帮助将需求转化为 DT 系统应满足的需求。还引入了分层聚合作为管理复杂性的主要架构方法。分层聚合允许关注点分离、计算负载分配、增量开发和模块化软件设计。设计框架分为六个步骤:1)需求和约束分析,2)物理系统分解,3)服务分配,4)性能和质量考虑,5)实施考虑以及6)验证和确认。

nexedge® 肯伍德数字系统

NXDN ® 空中接口的一个关键元素是 AMBE+2™ 声码器,它可以数字化语音,同时保留自然语音的细微差别,执行降噪,引入 FEC 并压缩语音数据以适应陆地移动无线电频谱带宽和数据速率。接下来,无线电的数字信号处理器 (DSP) 协议将声码器、信令、控制和 FEC 数据打包在一起,将其转换为调制发射器的独特滤波 4 级 FSK 数字波形。这会产生低误码率 (BER) 数字空中接口,因此即使在信号强度较弱的区域,您也可以获得稳定的通信。

使用数字系统进行胸腔引流管理

肺部手术后促进恢复的手术表明,数字引流系统比模拟系统具有多种优势 (4)。数字引流系统的优点如下:(I) 这些设备重量轻、结构紧凑,并且由于集成了抽吸泵,因此不需要连接到壁吸装置,这有利于患者转移。(II) 可以客观地量化和存储有关漏气的信息,并随时间推移进行存储,从而消除临床判断的变化。因此,关于胸管拔除的决策更加容易 (5)。避免外部吸入和使用数字引流系统均被证明具有低级别证据,但具有强烈的推荐级别。还应注意,与胸腔积液量相关的胸管拔除推荐标准是最多 450 mL/24 小时(证据级别:中等;推荐级别:强)。Thoraguard 手术引流系统(Centese,内布拉斯加州奥马哈)是一部新颖的

用于改善工人安全和健康的智能数字系统

为了研究智能数字工具和新的职业安全与健康监测系统的实际实施情况,以改善工人的安全和健康 4 ,欧盟职业安全与健康管理局开展了大量案例研究。这组案例研究包括从提供商/开发者层面审视的智能数字系统案例,也包括公司部署/实施此类系统的案例。根据《人工智能法案》,提供商是开发人工智能系统并将其投放市场的个人或实体。部署者是使用人工智能系统的个人或实体。本报告将使用“开发者”和“部署者”角色,因为本报告基于使用这些术语的案例研究。5 因此,案例研究调查了与开发阶段和实施阶段相关的方面。所有案例研究都考虑了包括工人参与在内的职业安全与健康方面,同时考虑到案例研究的类型。此外,所有案例研究都研究了安全有效实施的可能驱动因素、障碍和成功因素。

智能数字系统,可在工作中更好地安全和健康

有两种关键的智能数字工具和系统的主要总体方法:一种主动的方法,旨在防止伤害和促进健康,以及一种反应性方法,旨在应对事故和紧急情况。主动方法通过使其更快,更轻松,更便宜,有时连续(即24/7)。反应性方法最大程度地减少了已经发生的事故和紧急情况的后果,例如通过使事故报告更快,自动化,更便宜,更容易且污名化,同时改善事故调查,从而改善了事故报告。

关节炎患者血管和骨状态的关联数字系统

向广告的转变是破坏性和复杂的,尤其是从监管角度来看。AVS需要与以前的车辆不同的要求,因此需要制定新车辆法规和交通规则。AVS必须能够在各种交通状况和驾驶条件下与其他道路使用者(尤其是未受保护的道路使用者)安全互动;预测和检测风险,并以一定安全的范围驾驶,以防止事故和伤害;并遵守流量规则。(甚至可能必须与今天的交通规则不同。)“车辆法规”设定了应如何设计和运行车辆的要求,而“交通规则”设定了对道路用户在交通方面的行为的要求。在AD中,必须遵守交通规则,而不是驾驶员。这意味着必须设计AV符合流量规则。需要从监管的角度考虑这一点。同时,AVS的用户可能需要具有不同的流量规则,以使其与这些车辆相关。立法者还需要考虑这一点。

![[4065] - 148 ME(电子学)(数字系统/计算机)](/simg/f\f578ff03216fc42157b868d99d38fac4fcf7b0bc.webp)