XiaoMi-AI文件搜索系统

World File Search SystemEE (P) 538 传感器系统模拟电路课程大纲 2024 年冬季 SLN 13710

在本课程中,我们将探讨模拟电路分析和设计的高级主题,重点是与传感器接口相关的概念。我们将重点介绍离散电路和基于运算放大器的电路,即由运算放大器和无源元件(如电阻器和电容器)以及晶体管(BJT 和 MOSFET)组成的电路。我们将深入研究噪声(约翰逊噪声、散粒噪声、闪烁噪声),并学习如何设计电路以在实际设计约束(例如功率、成本、组件可用性)下实现特定的性能目标。我们将探讨线性的概念以及具有非线性特性的器件(例如晶体管、二极管和运算放大器)如何影响电路和系统性能。我们将讨论使用反馈设计精密电路的优势。我们将概述数据转换器(ADC 和 DAC),并探讨各种架构(奈奎斯特、过采样、Delta-Sigma)及其性能限制(噪声、线性、功率、速度)。

通过冻结-解冻贝叶斯优化技术实现模拟电路产量优化

摘要 —尽管 VLSI 社区关心的是工艺变化下高成品率的设计,但昂贵的计算成本使得传统的模拟电路成品率优化方法在工业应用中效率低下。本文提出了一种基于冻融贝叶斯优化技术的模拟电路高效成品率优化方法。成品率分析被集成到贝叶斯优化的探索过程中。通过指定的高斯过程回归方法,灵活的冻融贝叶斯优化技术被用于自动引导设计空间中的搜索并控制工艺空间中成品率分析的精度。制定并解决了性能优化问题以挖掘先验知识,并进一步加速。实验结果表明,与最新方法相比,所提出的方法可以获得 2.47 × –5.73 × 的加速,而不会损失精度。

通过冻结-解冻贝叶斯优化技术实现模拟电路产量优化

摘要 —尽管 VLSI 社区关心的是工艺变化下高成品率的设计,但昂贵的计算成本使得传统的模拟电路成品率优化方法在工业应用中效率低下。本文提出了一种基于冻融贝叶斯优化技术的模拟电路高效成品率优化方法。成品率分析被集成到贝叶斯优化的探索过程中。通过指定的高斯过程回归方法,灵活的冻融贝叶斯优化技术被用于自动引导设计空间中的搜索并控制工艺空间中成品率分析的精度。制定并解决了性能优化问题以挖掘先验知识,并进一步加速。实验结果表明,与最新方法相比,所提出的方法可以获得 2.47 × –5.73 × 的加速,而不会损失精度。

pvtsizing:基于涡轮-RL的批处理抽样优化框架,用于PVT-ROBUST模拟电路合成

摘要 - 随着CMOS技术的发展和电路的复杂性的增长,对模拟/混合信号设计自动化工具的需求正在迅速增加。尽管已经开发了一些工具来应对这一挑战,但是较少考虑了过程,电压和温度(PVT)变化引起的性能降低。本文介绍了PVTsizing,这是PVT-强大模拟电路合成的优化框架。pvtsizing采用信任区域贝叶斯优化(Turbo),用于高质量的初始数据集和参考点。多任务加固学习(RL)用于PVT操作。涡轮和RL均对批量友好,可以并行对设计解决方案进行采样。同时,提出了提高批评的修剪和缩放目标指标,以提高样本效率并降低运行时。此外,该框架自然支持随机不匹配而尺寸。在4个现实世界电路上,带有TSMC 28/180NM工艺,PvtSizing实现1。9× - 8。8×样品效率和1。6× - 9。8×时间效率的提高。索引术语 - Bayesian优化,增强学习,PVT变化,模拟电路合成

ALIGN:自动化模拟布局系统

摘要 —ALIGN(“从网表智能生成的模拟布局”)是一种用于模拟电路的开源自动布局生成流程。ALIGN 将输入的 SPICE 网表转换为特定于给定技术的输出 GDSII 布局,由一组设计规则指定。该流程首先自动检测电路网表中的层次结构,并将布局综合转换为层次化模块组装问题。在最低级别,使用设计规则的抽象生成参数化单元;然后在几何和电气约束下组装这些模块以构建电路布局。ALIGN 已被用于为多种模拟电路系列生成布局:低频模拟模块、有线电路、无线电路和电力输送电路。

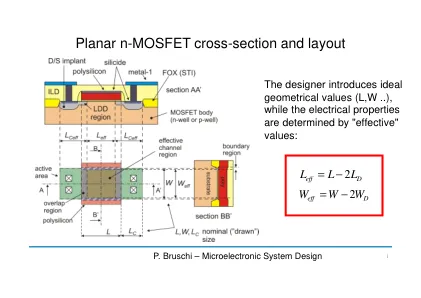

平面 n-MOSFET 横截面和布局

• 如果电路具有明确的静态工作点(如大多数模拟电路),则将工作点中实际作为源工作的端子标记为源会很方便。这将方便读取模拟器以文本或图形输出生成的设备电压。

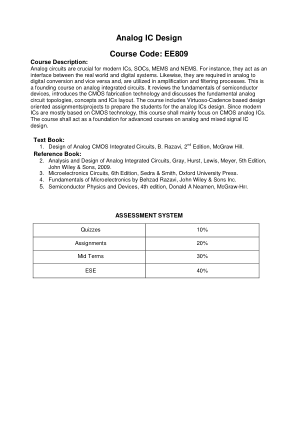

模拟 IC 设计课程代码:EE809

课程代码:EE809 课程描述:模拟电路对于现代 IC、SOC、MEMS 和 NEMS 至关重要。例如,它们充当现实世界和数字系统之间的接口。同样,它们在模拟到数字转换和反之亦然中是必需的,并且用于放大和滤波过程。这是模拟集成电路的基础课程。它回顾了半导体器件的基础知识,介绍了 CMOS 制造技术,并讨论了基本的模拟电路拓扑、概念和 IC 布局。该课程包括基于 Virtuoso-Cadence 的设计导向作业/项目,以帮助学生为模拟 IC 设计做好准备。由于现代 IC 大多基于 CMOS 技术,因此本课程将主要关注 CMOS 模拟 IC。该课程将作为模拟和混合信号 IC 设计高级课程的基础。