XiaoMi-AI文件搜索系统

World File Search System探索电源电压和温度

摘要。本文深入研究了在XOR-XNOR细胞中应用的常规和非常规设计方法。这些单元在各种算术逻辑电路中起着至关重要的作用,在低压和功率水平下运行的VLSI设计中具有很大的计算能力。本文研究了与常规和非规定设计策略相关的困难。此外,它对当前文献中有关电路设计参数的不同XOR/XNOR单元进行了相对评估。这项研究的结果表明,低技术节点中碳纳米管现场效应晶体管(CNTFET)技术的采用显着降低了电路延迟,而浮动栅极金属氧化物半导体(FGMOS)技术在电路电力效率方面显示出卓越的解释。讨论还涵盖了FinFET技术在创建XOR/XNOR细胞中的利用。本文评估了这些XOR/XNOR细胞的电压和温度弹性。使用22nm技术节点的HSPICE工具进行了分析。基于FGMO的XOR/XNOR细胞表明,对电压和温度波动的弹性最高。采用非常规技术遇到的主要挑战涉及缺乏适当的仿真模型和复杂的制造过程。这些挑战特别阻碍了这些开拓性方法的进步和采用。

低电源电压±0.82V下最低功耗的基于VDTA的电调谐波有源滤波器的CMOS实现

本文介绍了一种基于电压差分跨导放大器 (VDTA) 的波有源滤波器的高阶电压和电流模式低通或高通滤波器。针对波有源滤波器的基本有源构建模块,提出了波等效变量技术和拓扑模拟以及使用波变量技术的操作实现。将所提出的波等效技术与正确选择端子连接一起应用于波有源滤波器。本文提出,实现波有源滤波器的基本元件是串联电感和并联接地电容。通过使用 SPICE 模拟和 0.18 µm TSMC CMOS 技术参数,实现了最低功耗为 ±0.82 V 的 4 阶低通和高通巴特沃斯滤波器,从而验证了所提出的波有源滤波器。

字母A 30 Gbps 1.25 pJ/b CMOS接收器模拟前端,低电源电压

摘要 本文提出了一种30 Gbps 1.25 pJ/b光接收机模拟前端(Rx_AFE),主要由有源电压电流反馈跨阻放大器(AVCF-TIA)和交错有源反馈限幅放大器(LA)组成。通过在所提出的TIA中采用有源电压电流反馈技术,大输入电容得到很好的隔离,而不受低电源电压的限制,并且显著缓解了跨阻增益和输出极点频率之间的直接矛盾。同时,通过在LA设计中采用交错有源反馈技术,带宽进一步扩展。所提出的Rx_AFE采用40 nm bulk-CMOS工艺制造,跨阻增益为63.8 dB Ω,3 dB带宽为24.3 GHz。从电源电压 1.0 V 开始,当运行 30 Gbps PRBS 时,电路的功耗和功率效率分别为 37.5 mW 和 1.25 pJ/b。核心电路占用的芯片面积为 920 µ m × 690 µ m。关键词:光接收器、跨阻放大器 (TIA)、有源电压-电流反馈、交错有源反馈、限幅放大器 (LA)、CMOS 分类:集成电路(存储器、逻辑、模拟、RF、传感器)

字母 A 具有低电源电压的 30 Gbps 1.25 pJ/b CMOS 接收器模拟前端

摘要 本文提出了一种30 Gbps 1.25 pJ/b光接收机模拟前端(Rx_AFE),主要由有源电压电流反馈跨阻放大器(AVCF-TIA)和交错有源反馈限幅放大器(LA)组成。通过在所提出的TIA中采用有源电压电流反馈技术,大输入电容得到很好的隔离,而不受低电源电压的限制,并且大大缓解了跨阻增益和输出极点频率之间的直接矛盾。同时,通过在LA设计中采用交错有源反馈技术进一步扩展了带宽。所提出的Rx_AFE采用40 nm bulk-CMOS工艺制造,跨阻增益为63.8 dBΩ,3 dB带宽为24.3 GHz。从电源电压 1.0 V 开始,当运行 30 Gbps PRBS 时,电路的功耗和功率效率分别为 37.5 mW 和 1.25 pJ/b。核心电路占用的芯片面积为 920 µ m × 690 µ m。关键词:光接收器、跨阻放大器 (TIA)、有源电压-电流反馈、交错有源反馈、限幅放大器 (LA)、CMOS。分类:集成电路(存储器、逻辑、模拟、RF、传感器)

“使用逻辑进行设计” - 德州仪器

2 电源电压降低时的行为1 .......................。。。。。。。。。。。。。。。。。。。。。。。。..........2.1 电源电压关闭时的行为 1 ............。。。。。。。。。。。。。。。。。。。。。。。。...............2.1.1 双极电路 1 ..........。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。2.1.2 CMOS 电路 3.。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。2.2 低电源电压下的行为 3 .。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。2.3 部分关闭电源电压 4 .。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。2.4 更改通电子系统 6 .。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

AD52095 2x50W 立体声/1x100W 单声道 D 类音频...

AD52095 是一款具有可调功率限制功能的高效立体声 D 类音频放大器。扬声器驱动器的工作电源电压为 4.5V~26V,模拟电路的工作电源电压为 5V。它可以在 21V 电源电压下向 4 扬声器提供 50W/CH 输出功率,THD+N 低于 10%。

ad52068 2x20W立体声级音频放大器与...

AD52068是具有可调节功率限制功能的高效率立体声级音频放大器。扬声器驱动器的操作性为4.5V〜26V电源电压,模拟电路在5V电源电压下运行。它可以在24V电源电压下1%THD+N内传递20W/CH输出功率,并在播放音乐时没有外部散热器。

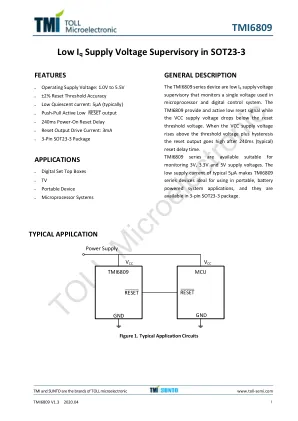

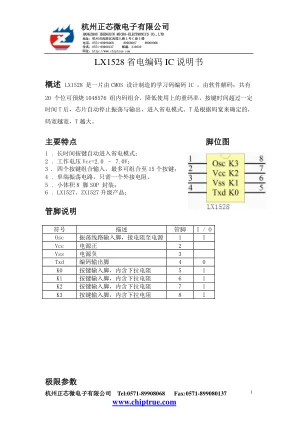

LX1528 省电编码IC 说明书

HANGZHOU ZHENGXIN MICRO-ELECTRONICS CO.,LTD 地址:杭州市西湖区西园八路 2 号 C 座 3 楼 电话: 0571-89908068 89908067 89908066 传真: 0571-89908137 邮编: 310030 网址: http://www.chiptrue.com 符号 参数 条件 范围 单位 Vcc 电源电压 -0.3 ~ 7 V VI 输入电压 -0.3 ~ Vcc+ 0.3 V VO 输出电压 -0.3 ~ Vcc+ 0.3 V Tst 储存温度 -40 ~ 125 ℃ Top 工作温度 - 20 ~ 70 ℃ Pdis 最大功耗 Vcc = 6V (空载) 10 mW