XiaoMi-AI文件搜索系统

World File Search System全文(PDF)

摘要。考虑了一种新型的注入方式——非复合注入方式,在非平衡载流子的双极扩散方向和非平衡载流子漂移方向相反的条件下,可以在 p - n - n + 型结构中沿电流正向实现这种注入方式。只有当 n - n + 结处的积累强于通过 p - n 结的注入时,即 n 基极与 n - n + 结边界处的载流子浓度高于 n 基极与 p - n 结边界处的载流子浓度时,才有可能实现这种注入方式。在这种模式下,电流对电压的依赖性呈现 J ~ V 类型,然后是 J ~ V 2 类型。实验中,在 Al–Al 2 O 3 –CdTe 结构中观察到了这种电流-电压特性行为。

偶极-偶极相互作用辅助量子点自组装用于高效发光二极管

当前最先进的量子点发光二极管的外部量子效率受限于较低的光子输出耦合效率。采用纳米棒、纳米片和点盘纳米晶体等取向纳米结构的发光二极管有利于光子输出耦合;然而,它们的内部量子效率往往会受到影响,因此实现净增益一直颇具挑战性。本文报道了各向同性形状的量子点,其特征是由纤锌矿相和闪锌矿相组成的混合晶体结构。纤锌矿相促进偶极-偶极相互作用,从而使溶液处理薄膜中的量子点定向,而闪锌矿相则有助于提升电子态简并度,从而实现定向光发射。这些特性的结合在不影响内部量子效率的情况下改善了光子输出耦合。制备的发光二极管的外部量子效率为 35.6%,并且可以在初始亮度为 1,000 cd m –2 的情况下连续运行 4.5 年,性能损失最小约为 5%。

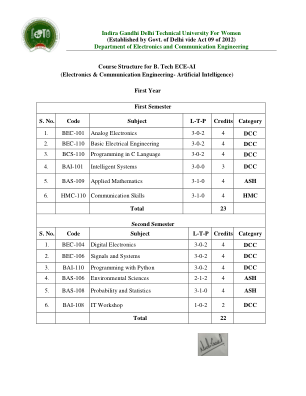

B. Tech ECE-AI(电子与通信工程-人工智能)课程结构

UNIT-I 12 小时 回顾半导体物理、p-n 结二极管、p-n 二极管特性及其操作、p-n 结电容(耗尽和扩散)、p-n 二极管击穿 二极管应用:削波和钳位电路、整流电路、齐纳二极管、齐纳二极管作为调节器、电压倍增器、p-n 二极管的开关行为 双极结型晶体管:晶体管的介绍和类型、结构、CB、CE 和 CC 模式下的 BJT 特性、工作点、交流/直流负载线、漏电流、饱和和截止工作模式、Ebers-moll 模型 偏置稳定:稳定需求、各种偏置方案、相对于 Ico、V BE 和 β 变化的偏置稳定性、稳定因素、热稳定性。

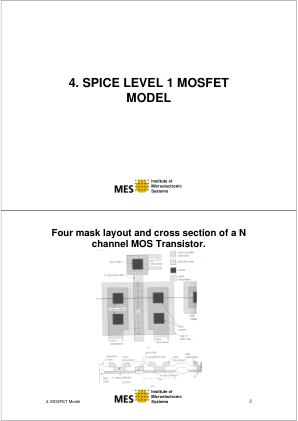

4. SPICE LEVEL 1 MOSFET 模型 - dvdtang.nl

RS- 源极电阻( Ω ) RSH- 漏极/源极扩散的薄层电阻( Ω / ) CBD- 零偏置漏极-体结电容(F) CBS- 零偏置源极-体结电容(F) MJ- 体结渐变系数(无量纲) PB- 体结的内置电位(V) • 使用 CBD、CBS、MJ 和 PB,SPICE 可计算漏极-体和源极-体电容的电压依赖性:

Sedra smith 微电子电路第 8 版国际版 pdf

您需要登录或创建帐户才能获得或声明访问权限。可用主题包括: 与二极管相关的额外主题 与 JFET 和 GaAs 器件和电路相关的额外主题 与有用的晶体管配对相关的额外主题 与输出级和功率放大器相关的额外主题 与内部运算放大器电路相关的额外主题 与滤波器和调谐放大器相关的额外主题 与波形生成和整形相关的额外主题 与双极数字集成电路相关的额外主题 与 MOS 数字集成电路相关的额外主题 要访问内容或兑换资源,用户必须登录或创建帐户。所提供的文本涵盖了与电子和数字设计相关的各种主题,包括双极结型晶体管 (BJT)、MOS 场效应晶体管 (MOSFET)、放大器、运算放大器电路、CMOS 数字逻辑电路和 VLSI 制造技术。重点关注领域包括集成电路放大器的构建模块、差分和多级放大器、输出级和功率放大器、运算放大器电路、CMOS 数字逻辑电路以及数字设计原理(例如功率、速度和面积)。文本还涉及 SPICE 设备模型、仿真示例和双端口网络参数。此外,它还涵盖了采用 CMOS 和双极工艺制造的 IC 设备的标准电阻值、单位前缀、典型参数值,并提供了所选问题的答案。

极化子跳跃在所有无定形阴极电致色素氧化物中诱导的双波段吸收

图1个极化子跳跃在WO 3中诱导的双波段吸收。A在不同时间间隔的GalvanoStatic电荷插入后WO 3膜的原位光学透射率。b,在450 nm(表示可见范围)和1100 nm(代表NIR范围)的WO 3膜的电荷能力的函数。c,od光谱是波长的函数,以及北极理论的吸收系数的理论计算。理论曲线已分解为下两个面板中的两个偏振子峰。d,在电荷插入过程中在不同时间的WO 3(W 4 F峰)膜的XPS光谱。e,d中XPS光谱得出的相应的W值的比例。XPS光谱和其他电荷插入状态的比例可在图中看到S6。f,C(A 1,A 2;左侧尺度)的两个峰的振幅显示为LI插入时间的函数,并将其与位点饱和理论获得的跳跃效率(H.E;右手尺度)相比。H.E.通过45分钟XPS的插值在D下降到零,从而获得了15和30分钟的点。

项目 2021-07 - 极寒天气...

– I2 发电资源(包括发电机端子)通过升压变压器的高压侧连接到 100 kV 或以上的电压:a) 单个总铭牌额定值大于 20 MVA。或者,b) 工厂/设施总铭牌额定值大于 75 MVA – I4 分散式发电资源,总容量大于 75 MVA(总铭牌额定值),并通过一个系统连接,该系统主要用于将这种容量输送到电压为 100 kV 或以上的公共连接点 o BES 定义中确定的黑启动资源,包含 I3 适用性部分未规定的排除

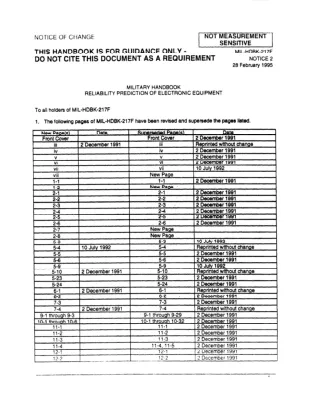

MIL-HDBK-217F - TQU GROUP

6: 分立半导体 分立半导体,简介 ................................................................00.......... 二极管,低频 .............................................................................................., 二极管,高频(微波,RF) ................................................................ 晶体管,低频,双极 ........................................................................................ 晶体管,低频,Si FET ........................................................0................................ 单结晶体管 ................................................................................................ 晶体管,低噪声,高频,双极 .............. G O.*......**.*.......................... 晶体管,大功率,高频,双极 .......0..... ........................................ 晶体管,高频,GaAs FET ............ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ....... ....... ....... ....... ....... .......

用于原位计算的双磁隧道结两位存储器和非易失性逻辑

在百亿亿次计算中,大量数据需要实时处理。传统的基于 CMOS 的计算范式遵循读取、计算和写回机制。这种方法在计算和存储数据时会消耗大量电力和时间。原位计算(在内存系统内处理数据)被视为百亿亿次计算的平台。自旋转移力矩垂直磁隧道结 (PMTJ) 是一种非易失性存储设备,具有多种潜在优势(快速读写、高耐久性和 CMOS 兼容性),有望成为下一代内存解决方案。双磁隧道结 (DMTJ) 由两个垂直排列的 PMTJ 组成。在本文中,DMTJ 不仅提供了构建独立和嵌入式 RAM 的可能性,还提供了基于 MTJ 的 VLSI 计算的可能性。介绍了一种支持非易失性逻辑计算范式的基于 DMTJ 的两位存储单元。多级单元支持高速读写两位存储单元和实时计算和存储输入数据的非易失性逻辑门。