XiaoMi-AI文件搜索系统

World File Search SystemIntel®快速攻击技术(Intel®QAT)软件...

4.1我有一个名为XYZ的应用程序,目的是使用系统中两个芯片组(PCH)设备的每个加密实例(总共四个实例)。配置文件会是什么样?............................................................................................................................................................................................................................................................ 21 4.2 cy name参数是否应在每个配置文件中使用唯一值?................................................................................................................................................................... 21 4.3 The firmware does not load.我该如何解决?...................................................................................................................................................................................................................................... 21 4.4当我尝试启动驱动程序时,我会看到与内存分配有关的错误(包括内核消息)。我该怎么做才能避免这种情况?....................................................... 21 4.5 When loading the package modules, I see kernel log warnings related to the signing of the modules.我需要做什么?.................................................................................................. 22 4.6 Why does Intel® QAT performance drop around buffer/packet sizes of 2kB?............... 22 4.7 I am receiving failures or hangs when sending perform requests to the Intel® QAT API after a fresh boot or after hotplug events.如何解决这些问题?............................ 22 4.8 How do I get the Intel® QAT driver to automatically start in SUSE Linux*?........................................................ 22

'半导体:

比较大的SOC(较小的硅区域)可行,但能够合并以近似较大(更昂贵)的SOC。航空航天应用寻求高性能,但低量使它很困难,因为即使是单个应用程序案例,大型定制ASIC的费用也很难,而在各种航空航天项目中发现的多样性都要少得多。使用chiplet概念,可以承销较小的图1。四核SOC参考体系结构。图2。参考体系结构的扩展。4个基本块,可以在许多安排中结合使用,以适合这些不同的应用程序,以适合许多单独的自定义设计的价格。与当代的耐受性处理器相比,该处理器是内置的,这些处理器是内置的,即尾随边缘半导体技术(例如150 nm),即使是建立在更先进的节点(例如32nm)中的单个芯片组也代表了替代性能的增长。追求chiplet作为模块化策略的希望是要比以前的处理器的逐步实现越来越多地实现,而是提供一种能够将有效扩展到更高水平的性能和更大的功能的方法。很高兴地,奇普特概念可以收获嵌入式构成中的重要发展。主要的是MulɵcoreCompuɵng的出现。现在不是这种情况,很难忘记清洁大型conty的大型耦合的单片locaɵon的方法,而芯片组的想法可能会不利。出于多种原因,在过去的15年中越来越有能力的整体式(单核)组合的进展(借助时钟速度的升级速度标记),将企业推向了整体式的企业,以将整体式的量化计划(核心)(核心)(内核)保存为整体性能,以保持整体性能。嵌入式组合中的第二种criɵcal时尚是朝着异质构成的方式,那里有许多类型的计算机存在于同一复杂的小工具中。在这种情况下,使用“样式”,我们指出,人们相信,几种倾向于通过常规结构驱动(例如,可预测的基于流的处理,可以利用管道上的“可电路”形式,这些形式可以在区域可编程阵列中实现,甚至可以随机地进行了更少的预测分支(又有一个更加可预测的分门形状)(甚至更易于预测的形状)(并且都具有更大的分支形式(以及一个更大的线程形状)(并且都具有一个更大的分类形状(和图形)。没有任何单个处理体系结构可以彻底完成所有操作,主要用于包含处理类型的组合的结构。通常将具有mulɵcore处理器(对于标准 - 摩尔vecompuɵng,尤其是在深度处理中的线程处理),照片处理单元(用于大量的基于移动的处理),以及几个虚拟指示器处理单元(用于额外的型号的频率和无线电频率)。对,再次,chiplet的想法可以通过使用

具有多路复用伪确定性光子源......

可靠、确定性地生产值得信赖的高质量单光子是离散变量光学量子技术的关键组成部分。对于基于单光子的完全纠错量子计算系统,估计需要光子源以超过 1 GHz 的速率产生可靠的光子流 (Vigliar 等人,2021)。光子复用是一种潜在的解决方案,其中低概率源与交换网络相结合,将成功的生产事件路由到输出,但需要极快的单光子切换和超低的损耗率。在本文中,我们研究了开关元件的具体属性,并提出了一种新设计,该设计利用了常见开关元件(例如导热垫)的一般单向属性。通过将多个开关引入基本的时间复用设备,我们可以在以更快的速率泵送的多路复用源中使用慢速开关元件。我们在多个错误通道下对这种设计进行建模,并表明预期性能现在受到集成光子芯片组内光波导的固有损耗率的限制。虽然开发的设计没有达到必要的 1 GHz 光子速率,但我们展示了当底层技术改进时可能变得有用的设计元素。

Z890 Aorus Elite X Ice

AMD Ryzen ™ 8000 Series -Phoenix 2 Processors support PCIe 4.0 x2 SSDs 1 x M.2 connector (M2C_SB), integrated in the Chipset, supporting Socket 3, M key, type 25110/22110/2580/2280 PCIe 4.0 x4/x2 SSDs 4 x SATA 6Gb/s connectors RAID 0, RAID 1, and RAID 10 support for NVMe SSD storage devices RAID 0, RAID 1, and RAID 10 support for SATA storage devices USB CPU: - 1 x USB Type-C ® port on the back panel, with USB 3.2 Gen 2 support - 1 x USB 3.2 Gen 2 Type-A port (red) on the back panel - 1 x USB 3.2 Gen 1 port on the back panel CPU+USB 2.0 Hub: - 3 x USB 2.0/1.1后面板芯片组上的端口:-1 X USB Type -C®端口,带USB 3.2 Gen 2X2支持,可通过内部USB标头获得-4 x USB 3.2 Gen 1端口(后面板上有2个端口,可通过内部USB标题可用的2个端口)-4 x USB 2.0/1.1端口 - 通过内部USB内部连接器可用。

Chiplet时代电路封装技术研究专门委员会成立宗旨

随着半导体的物理尺寸达到极限,以生成性人工智能为代表的对大规模计算能力的需求正在推动芯片上晶体管元件密度的持续增加。 FinFET结构可提高元件密度,同时抑制传统平面场效应晶体管(FET)小型化所导致的漏电流,目前该结构已开始量产,未来将向GAA(Gate-All-Around)纳米片结构迈进,该结构可将电流通道的控制面从FinFET的三面增加到四面。因此,晶体管的结构变得更加复杂,导致量产时产品良率下降、成本增加。另一方面,人们担心所需计算能力的扩大将超过半导体元件密度的扩大,导致电路规模超过曝光的光罩极限。在此背景下,为了缓解成本上升的问题,一种根据架构将半导体芯片物理地划分为芯片小体(chiplet)的方法已经投入量产。此外,未来还将考虑采用安装技术对适合光罩极限的芯片进行封装和扩大的方法。此外,Chiplet超越了单片芯片的简单划分,可以把不同代半导体芯片或已有芯片组合起来,有望缩短开发周期,改变供应链,有望成为未来半导体产业的一大趋势。

B13DET——超微

Supermicro B13DET 支持双第四代英特尔® 至强® 可扩展处理器(插槽 E1 LGA 4677-1),具有三个 UPI(最高 16GT/s)和高达 350W 的 TDP(热设计功率)。B13DET 采用英特尔 C741 芯片组构建,支持 4TB(最高)3DS RDIMM/RDIMM DDR5 ECC 内存,在 16 个 DIMM 插槽中速度高达 4800MT/s(下面的注释 1)。这款主板具有出色的 I/O 可扩展性和灵活性,包括两个支持 SATA 6G/NVMe 的 HDD 连接器、一个支持 PCIe 5.0 的 M.2 连接器、两个支持子转接卡的夹层插槽、一个支持 25GbE 以太网 LAN 的中板,以及来自 PCH 的用于支持 SATA 6.0 的额外 SATA 连接器。它还提供最先进的数据保护,支持硬件 RoT(信任根)和 TPM(可信平台模块)(见下文注释 2)。B13DET 针对 4U/8U SuperBlade 系统进行了优化,具有高密度和高速输入/输出能力。它是高性能计算 (HPC)、云计算、财务建模、企业应用程序、具有数据密度应用程序的科学和工程计算的理想选择。请注意,此主板仅供专业技术人员安装和维修。有关处理器/内存更新,请参阅我们的网站 http://www.supermicro.com/products/。

B13DET-超微

Supermicro B13DET 支持双第四代 Intel® Xeon® 可扩展处理器(插槽 E1 LGA 4677-1),具有三个 UPI(最高 16GT/s)和高达 350W 的 TDP(热设计功率)。B13DET 采用 Intel C741 芯片组构建,支持 4TB(最高)3DS RDIMM/RDIMM DDR5 ECC 内存,在 16 个 DIMM 插槽中速度高达 4800MT/s(见下文注释 1)。该主板具有出色的 I/O 可扩展性和灵活性,包括两个支持 SATA 6G/NVMe 的 HDD 连接器、一个支持 PCIe 5.0 的 M.2 连接器、两个支持子转接卡的夹层插槽、一个支持 25GbE 以太网 LAN 的中板,以及一个来自 PCH 的用于支持 SATA 6.0 的附加 SATA 连接器。它还提供最先进的数据保护,支持硬件 RoT(信任根)和 TPM(可信平台模块)(下面的注释 2)。B13DET 针对具有高密度和高速输入/输出能力的 4U/8U SuperBlade 系统进行了优化。它是高性能计算 (HPC)、云计算、财务建模、企业应用程序、具有数据密度应用程序的科学和工程计算的理想选择。请注意,此主板仅供专业技术人员安装和维修。有关处理器/内存更新,请参阅我们的网站 http://www.supermicro.com/products/。

Patrick Munnich*,Stefanie Dederichs,Paula Klein和Carl Bruno Figura语音清晰度:实时监控的横向LISP检测

摘要:在语音中纠正LISP对许多人来说可能会非常困难,因为它们可能没有意识到它们是否正在倾斜。为了帮助受影响的人,我们已经开发了一种简单的算法,以实时识别sigmatismus flashalis在“ s”声音中通过频域中的分析中的语音声音。算法在校准后识别LISP频带内的峰值。已经确定了3000-4000 Hz的频带对于LISP通常是准确的,对于单个男性测试对象,对于lisp而言,对于lisp的频段来说,频段为2500-3000 Hz。将语音记录分为较小的段,并比较了这些段中检测到的LISP和非LISP的数量以分类。从测试中,确定的段长度为0.5 s会产生最佳结果。该算法并未检测到每个LISP部分,但是它不会引起误报。我们在朱莉娅(Julia)的实施,具有多线程的每文件分析能够在高通Snapdragon 860智能手机芯片组上分析5 s至10 s长度之间的20个长度的文件,这意味着分析的速度远远快。提出的算法是一种简单的原型算法,能够在频域中对音频进行实时分析,以识别给定窗口中横向Lisps是否是主导的发音。该方法仅针对单个测试主题进行测试。但是,提出了向新个体调整参数的校准算法。该算法本身应该很容易扩展,以识别其他语音障碍。

电源管理集成电路

关于导师:Qadeer Khan 教授是印度理工学院马德拉斯分校电气工程系集成电路与系统组的助理教授。他于 1999 年获得印度新德里贾米亚米利亚伊斯兰大学电子与通信工程学士学位,并于 2012 年获得美国俄勒冈州立大学电气与计算机工程博士学位。他的博士工作重点是开发高性能开关直流-直流转换器的新型控制技术。2012 年至 2015 年,他担任高通公司圣地亚哥分公司的电源管理系统主管工程师,2015 年至 2016 年在班加罗尔高通公司工作,参与定义骁龙芯片组各种电源管理模块的系统和架构,以满足不同的智能手机市场需求。 1999 年至 2005 年,他曾就职于摩托罗拉和印度飞思卡尔半导体公司,主要负责设计用于基带和网络处理器的混合信号电路以及用于高压电机驱动器的全芯片集成解决方案。Qadeer Khan 博士拥有 18 项美国专利,并在模拟、混合信号和电源管理 IC 领域撰写/合作撰写了 20 多篇 IEEE 出版物。他担任 IEEE 固态电路杂志、IEEE 超大规模集成系统交易、IEEE 电力电子交易和 IEEE 电力电子快报的审稿人。他的研究兴趣涉及高性能线性稳压器、LDO、开关直流-直流转换器和用于便携式电子产品和能量收集的电源管理 IC

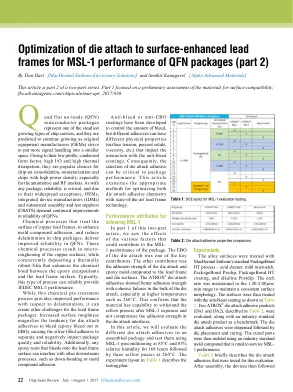

优化芯片与表面增强引线框架的连接,以实现 QFN 封装的 MSL-1 性能

扁平无引线 (QFN) 半导体封装是增长最为稳定的芯片载体类型之一,随着原始设备制造商 (OEM) 努力将更多的信号处理功能放入更小的空间,预计 QFN 封装将继续增长。由于 QFN 封装体积小、尺寸紧凑、输入/输出高、散热性好,因此成为芯片组整合、小型化和高功率密度芯片的热门选择,尤其是汽车和射频市场。与任何封装一样,可靠性至关重要,由于 QFN 封装被广泛接受,OEM、集成设备制造商 (IDM) 和外包组装和测试供应商 (OSATS) 要求继续提高 QFN 封装的可靠性。化学工艺处理铜引线框架的表面,以增强模塑化合物的附着力,并减少芯片封装中的分层,从而提高 QFN 封装的可靠性。这些化学工艺导致铜表面微粗糙化,同时沉积一层耐热薄膜,增强环氧封装材料和引线框架表面之间的化学键合。通常,这种工艺可以可靠地提供 JEDEC MSL-1 性能。虽然这种化学预处理工艺在分层方面提供了更好的性能,但它会给引线框架封装商带来其他挑战。表面粗糙度的增加会加剧芯片粘接粘合剂渗出(环氧树脂渗出或 EBO)的趋势,导致银填充粘合剂分离并对封装质量和可靠性产生负面影响。此外,渗入引线框架表面的任何环氧树脂都会干扰其他下游工艺,例如向下粘合或模塑料粘合。