XiaoMi-AI文件搜索系统

World File Search System实现 BaTiO3 中的超低压开关

用于计算超越互补金属氧化物半导体的铁电体。双极晶体管和互补金属氧化物半导体 (CMOS) 晶体管的微缩(即减小尺寸或增加总数 1 )取得了巨大成功,但随着半导体工艺的每一代发展,随着器件接近基本尺寸极限 2 ,微缩变得越来越困难。虽然摩尔微缩定律一直在延续,但工作电压的降低速度要慢得多,因为 Dennard 的微缩方案 3 只持续到 2003 年左右。研究人员目前正在探索其他方法,以继续遵循摩尔定律,使器件具有低工作电压(< 100 mV)和相应的低工作能量(每位 1-10 aJ),同时保持可接受的器件开关延迟(< 0.1 ns)。这推动了一系列替代的、超越 CMOS 的计算途径(例如,基于自旋、极化、应变等的途径)4、5 的研究。铁电体可实现非挥发性和低读/写能量,在存储器(例如铁电随机存取存储器)、逻辑或存储器内逻辑(例如铁电场效应晶体管 (FeFET) 应用 6、7 和负电容场效应晶体管)8、9 中引起了越来越多的关注。尽管引起了人们的关注,但问题在于大多数铁电器件都在高电压 6、7 (> 1 V) 下工作,因此与低功率操作不兼容 5。解决这个问题将标志着向前迈出的重要一步,并可能为铁电材料在超 CMOS 器件的出现中开辟道路。

评估超低压放大器 ASIC 的测量方法

摘要:本文介绍了为对全差分放大器(FDDA)原型芯片样品进行实验评估而开发的测量电路和测试板。被测设备(DUT)是采用130nm CMOS技术设计和制造的超低压、高性能集成FDDA。FDDA的电源电压为400mV。在带有制造的FDDA芯片的测试板上实现了测量电路,以评估其主要参数和特性。在本文中,我们重点评估以下参数:输入失调电压、共模抑制比和电源抑制比。开发并验证了测试板。测得的测试板误差为38.73mV。FDDA的失调电压为-0.66mV。测得的FDDA增益和增益带宽分别为48dB和550kHz。除了测量板外,还开发了一个图形用户界面,以简化测量期间对被测设备的控制。

适用于2.5V纳米集成电路的超低压触发可控硅ESD保护装置

可控硅整流器 (SCR) 因其对 ESD 应力的高稳定性而成为最具吸引力的 ESD 防护元件 [1]。然而,传统 SCR 器件具有较高的触发电压 (Vt1) 和较低的维持电压 (Vh) [2,3]。因此,它无法在大多数电路中提供有效的 ESD 防护。为了解决这些问题,许多基于局部的改进 ESD 防护方案被提出,例如改进型横向 SCR (MLSCR)、低触发 SCR (LVTSCR) 和二极管串触发 SCR (DTSCR) [4,5]。其中,DTSCR 能够实现非常低且灵活的触发电压,近年来许多基于 DTSCR 的改进结构被提出。例如,Chen、Du 等人提出了一种称为 LTC-DTSCR 的新型 DTSCR [6]。 LTC-DTSCR通过抑制DTSCR寄生SCR的触发,进一步降低了触发电压。但DTSCR结构相对较高的过冲电压和较慢的导通速度限制了其在充电器件模型(CDM)保护中的应用[7]。此外,DTSCR不适用于2.5 V及以上电路的ESD防护,因为触发二极管数量的增加会因达林顿效应而导致较大的漏电和闩锁风险。LVTSCR与传统SCR存在同样的问题:触发电压过高,难以调整以适应先进CMOS工艺的ESD设计窗口。目前,[8,9]中已提出了几种改进的LVTSCR结构,但它们均侧重于提高保持电压,这些器件的触发电压仍然较高(~8 V)。此外,还有许多新型SCR结构被提出。 Lin 等通过在 SCR 中引入两个栅极,实现了低触发电压、低漏电、低寄生电容的新型 SCR 器件 [10],但需要外部 RC 电路辅助触发,会造成巨大的额外面积消耗。P. Galy 等将 SCR 嵌入 BIMOS 中 [11],实现了超紧凑布局、低触发电压、低导通电阻,但其保持电压较低,如果施加的电压域较高,会增加闩锁风险。

0.4-V 6.6-µW 75-dB SNDR Δ-Σ 调制器...

摘要 本文介绍了一种用于植入式生物医学设备的超低压 (ULV) 高分辨率低功耗连续时间 delta-sigma 调制器。二阶单比特调制器采用前馈架构和新型全差分 ULV 放大器,在 0.4 V 电源下实现高信噪比加失真比 (SNDR) 和节能运行。该放大器采用栅极输入 AB 类输出拓扑和局部共模反馈 (CMFB) 环路,以实现大输出摆幅,从而减少谐波失真并降低功耗。采用强大的时钟发生器来确保调制器在 ± 10% 电源变化范围内的一致性能。该调制器采用 130 nm CMOS 技术制造,带有常规 VT 晶体管。测量结果表明,在 500 Hz 带宽内,在标称 0.4 V 电源下,该调制器实现了 75.5 dB SNDR,功耗为 6.6 µ W。在最近报道的用于植入式生物医学应用的 0.4 V 或以下电压下工作的 DSM 中,所实现的 SNDR 是最好的。即使在 0.32 V 电源下工作,该调制器也能实现 69 dB SNDR,功耗为 3.7 µ W。关键词:连续时间、Delta-Sigma 调制器、生物医学设备、模拟数字转换器、超低压放大器、超低压电路分类:集成电路(存储器、逻辑、模拟、射频、传感器)

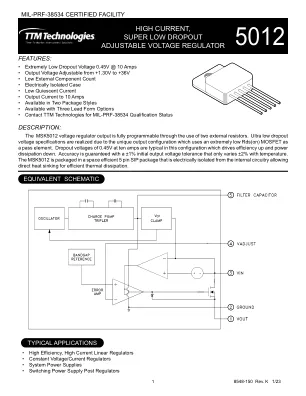

数据表 - 5012 系列

MSK5012 稳压器输出可通过使用两个外部电阻器完全编程。由于独特的输出配置使用极低 Rds(on) MOSFET 作为传输元件,因此实现了超低压差电压规格。在此配置中,10 安培时的典型压差为 0.45V,这可提高效率并降低功耗。精度可保证,初始输出电压公差为 ±1%,且仅随温度变化 ±2%。MSK5012 采用节省空间的 5 针 SIP 封装,与内部电路电气隔离,可直接散热,实现高效散热。

调节弹簧复位执行器 Belimo EF24A-SR-S2,具有紧急功能,用于调节通风和空调系统中的风门

安全 防护等级 III 超低压 UL 2 级电源 防护等级 IP54 NEMA2,UL 外壳类型 2 EMC 低压指令 CE 符合 2004/108/EC CE 符合 2006/95/EC 认证 符合 IEC/EN 60730-1 和 IEC/EN 60730-2-14 cULus 符合 UL 60730-1A 和 UL 60730-2-14 以及 CAN/CSA E60730-1:02 操作模式 类型 1.AA.B 额定脉冲电压 执行器 辅助开关 0.8 kV 2.5 kV 控制污染等级 3 环境温度 –30 ... +50°C 非工作温度 –40 ... +80°C 环境湿度 95% 相对湿度,无凝结 维护 免维护

2023 年通用登记文件

据 Rexel 集团所知,目前尚无有关该市场的权威外部报告,无法全面涵盖或分析低压和超低压电气产品的专业分销情况。因此,Rexel 集团根据多种来源进行了估算,包括内部调查、独立第三方或电气产品分销商专业联合会的研究和统计数据、专业出版物(如《电气商业新闻》和《电气批发》)、Rexel 集团竞争对手发布的数据以及运营子公司的数据。Rexel 集团认为这些研究可靠,但尚未经过独立专家的验证。Rexel 集团不保证第三方使用其他方法分析或汇编市场数据会获得相同的结果。此外,Rexel 集团的竞争对手可能对其市场有不同的定义。

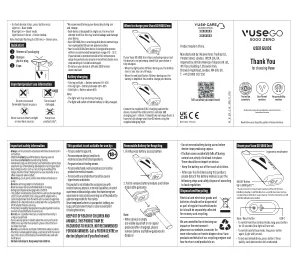

谢谢-Vuse

• 请勿拖拽、挤压、刺穿、焚烧或将设备浸入水中。 • 请勿将异物插入设备。 • 充电时切勿让设备无人看管。 • 通用充电线的额定输入为 5VDC 1A。 • 本产品只能连接到额定 5VDC、0.5A 的安全超低压 (SELV) 电路。使用电流输出低于此值的 AC/DC 适配器会导致充电时间变长。 • 遵守您使用的 AC/DC 适配器用户指南中详述的所有安全信息。 • 如果以制造商未指定的方式使用,设备提供的保护可能会受损。 • 当您或附近的任何人使用氧气罐时,请勿使用电子烟。 • 如果您对 Vuse GO 5000 Zero 或任何其他 Vuse 产品的使用有任何疑问或疑虑,请联系 Vuse 客户服务团队。 • 请勿在海拔 3000 米的高度使用您的设备。 • 如果电池损坏或漏液,请避免接触皮肤或眼睛。如果发生这种情况,请立即用水冲洗并就医。• 包含小部件。请远离儿童。

LOT 2:配电和电力变压器任务 1-7

我们的简要发现(按任务顺序)如下:任务 1:变压器被定义为用于电力传输和配电系统。这些变压器可以根据其应用进行细分。配电变压器由配电系统运营商或最终用户安装,并且最常提供与低压 (LV) 配电网 (230/400 VAC) 的连接。这些变压器包括用于连接分布式能源 (DER)(例如风力涡轮机)的变压器。由输电系统运营商安装的变压器也称为“电力变压器”。它们用于中压 (MV) 和/或高压 (HV) 电网。另一类较小的工业变压器是隔离(分离)变压器或安全超低压 (SELV)(控制)外部电源变压器。较小的工业变压器是根据其他标准制造的,并且不连接到中压系统,因此很容易区分。根据 EN 60076-1(IEC 60076-1),电力变压器一般被视为 1 kVA 单相和 5 kVA 多相以上的变压器(包括自耦变压器),因此本研究不考虑较低的额定值。任务 1 还准确地揭示了正在使用的立法和标准。变压器最重要的效率参数是空载和负载损耗,它们是使用阶段电力损耗的原因。根据变压器类型,这些参数由不同的标准涵盖: