XiaoMi-AI文件搜索系统

World File Search SystemNiO/β-TiO2不稳定性实验研究...

摘要:制备了NiO/β-Ga2O3异质结栅场效应晶体管(HJ-FET),并通过实验研究了在不同栅极应力电压(VG,s)和应力时间(ts)下器件的不稳定性机制。发现了器件在负偏压应力(NBS)下的两种不同退化机制。在较低的VG,s和较短的ts下,NiO体陷阱捕获/脱捕获电子分别导致漏电流的减少/恢复。在较高的VG,s或较长的ts下,器件的传输特性曲线和阈值电压(VTH)几乎永久地负移。这是因为界面偶极子几乎永久地电离并中和了异质结界面上的空间电荷区(SCR)中的电离电荷,导致SCR变窄。这为研究NiO/β-Ga2O3异质结器件在电力电子应用中的可靠性提供了重要的理论指导。

一种具有增强驱动能力的新型沟槽型三栅极晶体管

摘要 — 本文介绍了 40 nm 嵌入式非易失性存储器技术中新型高密度三栅极晶体管的设计、实现和特性。深沟槽用于集成与主平面晶体管并联的两个垂直晶体管。由于内置沟槽,所提出的制造工艺增加了晶体管的宽度,而不会影响其占用空间。平面 MOS 结构的电压/电流特性与新型三栅极晶体管的特性进行了比较。新架构提供了改进的驱动能力,导通状态漏极电流是其等效标准 MOS 的两倍,并具有较低的阈值电压,适用于低压应用。最后,在工作电压范围内验证了栅极氧化物和结的可靠性。索引术语 — 多栅极晶体管、MOS 器件、沟槽晶体管、驱动能力、闪存。

BTI 老化现象对模拟放大器影响的研究

摘要 CMOS 技术的扩展允许设计更复杂的系统,但同时也带来了一些可靠性问题。特别是,大幅扩展的微电子技术受到偏置温度不稳定性 (BTI) 老化现象的影响,这种现象导致晶体管阈值电压的绝对值随老化时间增加,从而降低微电子电路的可靠性。在本文中,我们估计了 BTI 对开环配置的运算放大器 (OPAMP) 以及基于 OPAMP 的三个卓越模拟放大器的性能下降。结果表明,BTI 会严重影响所研究电路的性能,并且这种性能下降会随着工作温度的升高而恶化。我们还简要介绍了一种可能的低成本监控方案,用于检测由 BTI 引起的 OPAMP 性能下降。我们的监控器的有效性已通过布局前电气模拟得到验证,结果表明它可以可靠地用于评估 OPAMP 的老化性能下降。

灵活的现场效应晶体管构建技术,简短的评论

1.1 F-FET结构通常,F-FET由源,排水和门组成。它在绝缘底物上收缩。源和排水量沉积在半导体上,并通过导电电极(通常是金,铜或银)连接到外部电源。FET的门通常在基板的顶部或底部制造,这就是FET结构称为顶部或底部门的原因(图1)。基本上,电荷载体在施加的栅极电压的控制下流过FET。V GS和I DS之间的关系是I DS = µ(WC/2L)(V GS -V T)2,其中I DS是从排水源流到源的电流,C是绝缘体电容,V t是阈值电压,W是通道的差异,L是其长度,L是其长度,Schneider,Schneider等。[1]。

VLSI 设计 (R20A0419)

第一单元简介:集成电路技术简介——摩尔定律、微电子演进、制造:NMOS、CMOS(n 阱、p 阱、双管)MOS 晶体管的基本电气特性:I DS - V DS 关系、MOS 晶体管阈值电压-V T 、品质因数-ω 0 、跨导- gm 、g ds ;传输晶体管、NMOS 反相器、由另一个 NMOS 反相器驱动的 NMOS 反相器的上拉与下拉比(Z=4:1)、各种上拉、CMOS 反相器的分析和设计。第二单元 VLSI 电路设计流程:VLSI 设计流程(Y 图)、MOS 层、棒图、设计规则和布局、基于 Lambda(λ) 的导线、触点和晶体管设计规则、NMOS 和 CMOS 反相器和门的布局图 MOS 电路的缩放、缩放的局限性

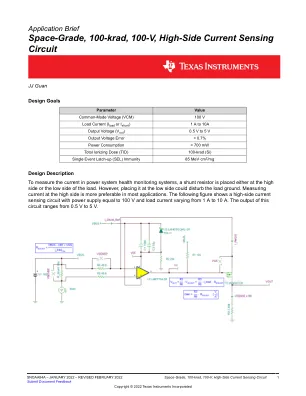

航天级、100krad、100V、高侧电流感应电路 (Rev. A)

• PMOS 选择 1. PMOS 的阈值电压 |V th | 的绝对值需要足够小,以便运算放大器能够打开和关闭 PMOS 栅极。 2. PMOS 的零栅极电压漏极电流 (I DSS ) 定义栅极电压等于 V bus 时的漏电流。I DSS 设置较低的 V out 范围。 3. 如果从运算放大器输出 (V o ) 到栅极的线路电阻过大,则 PMOS 栅极电容会影响稳定性。此电容在 1/ ꞵ 曲线中增加了一个零点。如果零点位于 1/ ꞵ 和 Aol 截距点的左侧,相位裕度会减小。因此,最好使用小的栅极电容。 4. 根据军用标准,漏极-源极击穿电压必须是 V bus 的两倍,至少需要 200V 的击穿电压。

高 k 电介质材料对电气的影响...

摘要:本文介绍了使用不同高介电常数 (高 k) 栅极介电材料的双栅极 (DG) 和栅极环绕纳米线 (GAA) MOSFET 的电气行为。为了研究高 k 介电材料对 DG 和 GAA 的影响,使用 Atlas Silvaco TCAD 工具模拟器件并确定电气特性。本研究选择的高 k 材料是氮化硅 (Si3N4)、氧化铝 (Al2O3)、氧化锆 (ZrO2) 和氧化铪 (HfO2)。栅极介电材料在设计新型高性能纳米级电气器件方面发挥了重要作用。可以观察到,当接近更高的介电常数值时,导通电流增加,而亚阈值斜率 (SS) 阈值电压 (Vth) 和漏电流减少。可以观察到,与其他模拟介电材料相比,HfO2 对 DG 和 GAA MOSFET 都表现出最佳性能。

对欧姆 p-GaN 功率 HEMT 进行预处理,以实现可重复的 Vth 测量

在 GaN HEMT 的可靠性研究中,阈值电压 (V th ) 的波动对监测电漂移提出了挑战。虽然欧姆 p-GaN 等技术可以减轻 V th 波动,但可恢复电荷捕获的问题仍然存在。因此,在进行可靠性研究时采用新颖的特性分析方法至关重要,这样才能测量内在变化而不是即使在未退化的晶体管中也存在的电荷捕获效应。本文阐述的一种方法可以可靠且可重复地测量欧姆 p-GaN 栅极 HEMT GaN 的 V th 。在阈值电压测量之前立即引入专用的栅极偏置曲线以使其稳定。这个预处理阶段需要负偏置电压,然后再施加适当高的电压才能有效。所介绍的新协议也被证明适用于其他 HEMT GaN 结构。

温度对双极晶体管特性影响的研究

摘要。电子电路板的温度升高会对电子电路产生明显的影响,从而导致电路元件的基本参数发生一些变化。本文旨在研究和分析高温对双极晶体管静态和动态特性的影响。这项研究是通过在不同温度下研究和分析 NPN BJT 晶体管 2SC2120 的几个参数进行的实验。结果表明,随着温度从 25 °C 升高到 130 °C,集电极电流从 0.19 A 显著增加到 0.23 A,电流增益从 0.14 显著增加到 0.22。至于阈值电压,发现其值从 0.6 伏降低到 0.4 伏。结果还表明,对于动态特性,随着温度升高到 130 °C,发射极-基极结的扩散电容从 10.1 nF 增加到 45.02 nF。最后发现,在相同的温度范围内,栅漏结的反向电容从41.4 pF增加到47.3 pF。