XiaoMi-AI文件搜索系统

World File Search System适用于全水凝胶生物电子学的 3D 可打印高性能导电聚合物水凝胶

工程应变加统一。d,Pt 电极和 BC-CPH 在第 1 次、第 5,000 次和第 10,000 次循环的电流密度与电位图。e,Pt 电极和 BC-CPH 的电荷存储容量 (CSC) 与循环伏安法 (CV) 循环的关系。f,Pt 电极和 BC-CPH 在第 1 次和第 1M 次循环的双相输入脉冲 (顶部) 和相应的电流密度与时间图 (底部)。g,Pt 电极和 BC-CPH 的电荷注入容量 (CIC) 与电荷注入循环的关系。全部 10

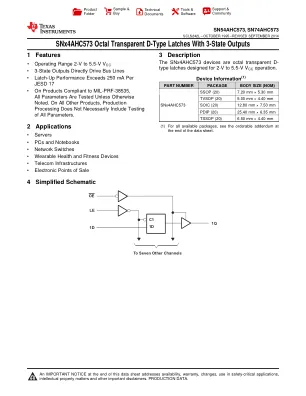

SN54AHC573、SN74AHC573 (Rev. L) - 所有产品

注意:A. CL 包括探针和夹具电容。B. 波形 1 适用于具有内部条件的输出,即输出为低,除非被输出控制禁用。波形 2 适用于具有内部条件的输出,即输出为高,除非被输出控制禁用。C. 所有输入脉冲均由具有以下特性的发生器提供:PRR ≤ 1 MHz、ZO = 50 Ω、tr ≤ 3 ns、tf ≤ 3 ns。D. 每次测量一个输出,每次测量一个输入转换。E. 并非所有参数和波形都适用于所有设备。

SN74LVC1G125 具有三态输出的单总线缓冲门

注意:A. C 包括“探针”和“夹具”电容。 B. 波形 1 用于具有内部条件的输出,即输出为低,除非被输出控制禁用。波形 2 用于具有内部条件的输出,即输出为高,除非被输出控制禁用。C. 所有输入脉冲均由具有以下特性的发生器提供:PRR 10 MHz,Z = 50 。D. 每次测量一个输出,每次测量一个转换。E. t 和 t 与 t 相同。F. t 和 t 与 t 相同。 G. t 和 t 与 t 相同。H. 所有参数和波形并不适用于所有设备。

基于通用逻辑门的基于CADENCE VIRTUOSO的电路模拟:董事会教程Indranil Maity电子和通信部

抽象的门级设计和电路模拟是构建复杂数字电路的基本过程。本文着重于两个通用数字逻辑门的设计和电路模拟。NAND和NOR GATES使用Cadence Virtuoso软件。研究利用了在每个逻辑门上进行的瞬态分析的多功能环境,以模拟对输入脉冲信号的输出响应。将模拟的结果绘制为瞬态图,以正确地可视化门操作。模拟结果表明,NAND和NOT门都经过了适当的操作,这通过其真实表得到了进一步验证。当两个输入信号都高时,NAND门仅产生低输出信号。当所有输入信号都较低时,NOR GATE才会产生一个很高的输出信号。通过严格的模拟和细致的分析,这项研究发现了这些逻辑门的动态行为,从而阐明了它们的功能和性能特征。1。简介

1100/2200 大型机技术的历史和演变

真空管 1103 真空管中大多数都是三极管。三极管包含一个灯丝,灯丝由通过它的电流加热,并放置在靠近“阴极”的位置,阴极反过来变热,导致电子从阴极表面的稀土涂层发射出来。带负电的电子被吸引到周围带正电的阳极或“板”。当在阴极和板之间放置一个称为“网格”的细网时,它充当控制元件。网格上的负电压可以大大减少流向板的电流。通常向板上施加约 100 到 200 伏电压,网格上的约 -20 伏电压可以切断管电流。一个管壳中包含两个三极管,这一对可以构成一个触发器。一个触发器,存储一个信息位,可以设置为“一”,清除为“零”,或切换,即,改变为相反状态。后一个功能在某些逻辑和算术运算中非常方便。电容器将触发器的状态存储一小段时间,因此它不会因单个输入脉冲而切换两次。另一个三极管通常连接到每个触发器输出作为“阴极跟随器”(带有

优化脑启发神经网络中的信息处理

摘要。人们认为,大脑网络保持高传输效率的方式是理解大脑活动的基础。由更多细胞组成的大脑使信息传输更加可靠,对噪声的鲁棒性更强。另一方面,在更大的网络中处理信息需要额外的能量。最近的研究表明,复杂性、连通性和功能多样性,而不仅仅是神经元的大小和数量,可能有利于记忆、学习和更高级认知的进化。在本文中,我们使用香农信息理论定量解决传输效率问题。我们将神经网络描述为通信通道,然后将信息测量为刺激和网络响应之间的互信息。我们采用基于 Levy 和 Baxter 提出的方法的概率神经元模型,该模型包含基本的定性信息传输机制。在本文中,我们概述并讨论了我们之前关于大脑启发网络的定量结果,并在更广泛的文献背景下探讨了它们的定性后果。结果表明,在非常嘈杂的环境中,例如,只有三分之一的输入脉冲被允许通过嘈杂的突触并深入网络,互信息通常会最大化。此外,我们还表明,抑制连接以及适当位移的长距离连接通常可以显著提高传输效率。从高等数学的角度深入理解大脑过程对于解释大脑效率的本质起着重要作用。我们的研究结果证实,在进化过程中出现的基本大脑成分是为了优化传输性能而产生的。

神经形态入门套件的披露

神经形态计算是一种受大脑启发的计算方法。神经形态计算的主要构造是脉冲神经网络 (SNN),许多资料对此进行了解释 [20]、[24]。我们使用术语“神经处理器”来定义一种计算设备,在该设备上可以加载脉冲神经网络,然后将输入脉冲暂时应用于特定的输入神经元。神经处理器处理脉冲并运行 SNN,在整个网络中传播脉冲。有指定的输出神经元,可以从外部读取脉冲。有许多神经处理器模拟器 [3]、[5]、[10] 和硬件项目 [1]、[4]、[8]、[24]。然而,大多数硬件项目都是商业性的,或者由研究项目以各个研究小组独有的方式运行。我们这项工作的目的是提供一种低成本、灵活的硬件套件,研究人员可以使用它来探索神经形态计算。具体来说,我们的目标是让该套件能够实现一种简单且廉价的机制,用于开发由神经处理器驱动的物理应用。我们的灵感之一来自代尔夫特大学的一个项目,其中的作者实现了一个神经形态 PID 控制器,用于调整 MAV 的高度 [28]。作者显然需要一个小型、轻便、自封装的系统,用于将传感器输入转换为脉冲,将这些脉冲发送到神经处理器,然后解释输出脉冲。我们设计了该套件用于类似这样的用例。在本文的后续部分中,我们将描述套件的组件、它们的组成、示例套件和物理应用。

Vasil Penchev。量子信息保守性及其解释为“可区分性 /无法区分性”和“ CLA < / div>),“少两个位” < / div>

摘要本文重点介绍了带通(BP)负数组延迟(NGD)功能的时间域分析。创新的NGD调查基于“ lill” - 形状被动微带电路的创新拓扑的时域实验。描述了特定微带形状构成的概念证明(POC)的设计原理。NGD电路的灵感来自最近分布的“ Li” - 拓扑。在时间域调查之前,研究了所研究电路的BP NGD规格是学术上定义的。作为基本定义的实际应用,本文的第一部分介绍了“ lill” - 电路的频域验证。POC电路是由2.31 GHz NGD中心频率和27 MHz NGD带宽的-8 NS NGD值指定的。“ Lill” - 电路的衰减损失约为-6。在NGD中心频率下 2 dB。 然后,用测得的S-参数的Touchstone数据代表的“ Lill”的两端子黑框模型被用于瞬态模拟。 测得的组延迟(GD)说明了测试的“ lill” - 电路在NGD方面作为BP函数,NGD等于-8。 在NGD中心频率处为1 ns。 使用高斯脉冲调节正弦载波进行BP NGD函数的时间域演示。 可以解释具有同时绘制良好同步输入和输出信号的创新实验设置。 可以观察到,正弦载波不超出NGD波段时,输出信号会延迟。2 dB。然后,用测得的S-参数的Touchstone数据代表的“ Lill”的两端子黑框模型被用于瞬态模拟。测得的组延迟(GD)说明了测试的“ lill” - 电路在NGD方面作为BP函数,NGD等于-8。在NGD中心频率处为1 ns。使用高斯脉冲调节正弦载波进行BP NGD函数的时间域演示。可以解释具有同时绘制良好同步输入和输出信号的创新实验设置。可以观察到,正弦载波不超出NGD波段时,输出信号会延迟。通过使用具有27 MHz频率带宽的高斯向上转换的脉冲,使用测量的“ Lill”电路的Touchstone S-参数从商业工具模拟中理解了BP NGD时间域响应。但是,当将载体调谐为大约等于2.31 GHz NGD中心频率时,输出信号包络线在大约-8 ns中。确认BP NGD响应的时间域典型行为,在测试期间考虑了具有高斯波形的输入脉冲信号。但是,必须在NGD带宽的功能中确定输入信号频谱。在测试后,与输入相比,测量的输出信号信封显示前缘,后边缘和时间效率的峰值。当前可行性研究的结果开放了BP NGD功能的潜在微波通信应用,特别是对于使用ISM和IEEE 802.11标准运行的系统。