XiaoMi-AI文件搜索系统

World File Search System电动总线操作和充电过程的建模

摘要:从柴油到电动总线的过渡允许减少温室气体排放。但是,必须评估收费策略对公交服务质量和公用电网的影响,以确保公共交通部门能源过渡的可行性。这项研究通过介绍公交网络的全面建模来研究不同位置和充电基础设施大小的性能。它还估计了局部光伏(PV)生产的潜在受益,以减少对公用电网的负面影响。提出的方法用于对法国Compiègne的一条城市公交线进行建模,并为各种案例研究进行了模拟。结果表明,所提出的方法允许通过确定到达的延迟来分析充电过程对总线服务质量的影响。模拟还显示了充电器放置对车载电池容量的影响,电池充电的总峰值功率需求以及PV自动消费比。直接用来充电总线的PV能量的量仍然很低,尽管场景之间有所不同。PV能量不足以充分充电公交车;但是,夏天可以额外的固定存储空间就足够了。

Ladot Transit零排放总线推出计划

[注意:拟议的法规命令的此版本符合政府法规第11346.2第(a)(3)条。在下划线中显示了所提出的修订,以指示增加和三振出局,以指示现有监管文本中的删除。[括号划定的下划线文本]是这些修正案批准日期的占位符文本。左边缘和右边缘中的文本气球中的垂直线是为了易于参考的更改(实质性和非基础)的标志,而不是拟议的修订。为了易于可读性,Carb还提供了拟议的修正案的版本,可以在下划线/三振出局的修正案和“干净”版本之间切换,其中包含在监管文本中的修正案,可以在附录A-1.1]

北剑桥电池电动总线设施修改

MBTA Capital Delivery – Transit Group • John Schwarz - Acting Deputy Chief of Transit Programs • Jim Caroselli - Senior Director Transit Station and Facilities • Sheryl Diaz - Senior Project Coordinator • Kayla Lang - Resident Engineer • Greg McNally - Senior Project Manager

用于燃料电池总线的绿色氢生产的微电网

GHI全球水平辐照Capex资本支出repex置换费用OPEX运营费用O&M运营和维护LCOE LCOE升级的电力LOCH升级NPC NPC NPC NET NET的成本EFL Entural Ensce EFL Energy Efl Energy Effi fiji Limited RAB调节资产基础资产基础FCCC FCCC FIJI竞争和消费者委员会的电力委员会能源资源

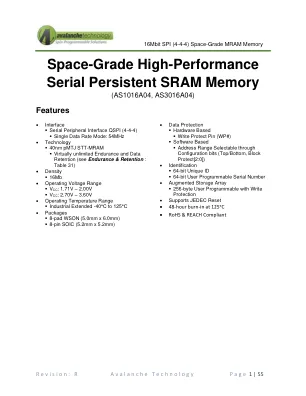

航天级高性能串行持久性 SRAM 存储器

SRAM 闪存 EEPROM MRAM 非易失性 − √ √ √ 写入性能 √ − − √ 读取性能 √ − − √ 耐久性 √ − − √ 功率 − − − √ MRAM 是一种真正的随机存取存储器;允许在内存中随机进行读取和写入。MRAM 非常适合必须存储和检索数据而不会产生较大延迟损失的应用程序。它提供低延迟、低功耗、无限耐久性和可扩展的非易失性存储器技术。ASx016A04 具有串行外设接口 (SPI)。SPI 是一种同步接口,它使用单独的数据和时钟线路来帮助保持主机和从机的完美同步。时钟告诉接收器何时对数据线上的位进行采样。这可以是时钟信号的上升沿(从低到高)或下降沿(从高到低)或两个沿;有关更多详细信息,请参阅本数据表中的指令序列。当接收器检测到正确的边沿时,它可以锁存数据。 ASx016A04 采用小尺寸 8 焊盘 WSON 和 8 引脚 SOIC 封装。这些封装与类似的低功耗易失性和非易失性产品兼容。ASx016A04 已在 -40°C 至 125°C 的工作温度范围内进行了测试,并在 125°C 下进行了 48 小时老化测试。

EN25QX64A (2CPU) 64 兆位 3V 串行闪存...

该设备是一个 64 兆位(8,192K 字节)串行闪存,具有先进的写保护机制。该设备通过标准串行外设接口 (SPI) 引脚支持单比特和四比特串行输入和输出命令:串行时钟、芯片选择、串行 DQ 0 (DI) 和 DQ 1 (DO)、DQ 2 (WP#) 和 DQ 3 (HOLD#/RESET#)。支持高达 133MHz 的 SPI 时钟频率,在使用四路输出读取指令时,允许四路输出的等效时钟速率为 532MHz(133MHz x 4)。使用页面编程指令,可以一次对内存进行 1 到 256 个字节的编程。该设备还提供了一种复杂的方法来保护单个块免受错误或恶意编程和擦除操作的影响。通过提供单独保护和取消保护块的能力,系统可以取消保护特定块以修改其内容,同时确保内存阵列的其余块得到安全保护。这在以子程序或模块为基础修补或更新程序代码的应用中非常有用,或者在需要修改数据存储段而又不冒程序代码段被错误修改的风险的应用中非常有用。该设备设计为允许一次执行单个扇区/块或全芯片擦除操作。该设备可以配置为以软件保护模式保护部分内存。该设备可以对每个扇区或块维持至少 100K 次编程/擦除周期。

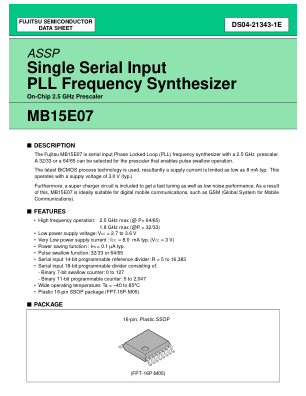

单串行输入 PLL 频率合成器 - SM0VPO

将 PS 引脚设置为低电平,IC 进入省电模式,因此电流消耗可限制为 10 µ A(最大值)。将 PS 引脚设置为高电平,则释放省电模式,IC 正常工作。此外,还包含间歇操作控制电路,有助于从省电模式平稳启动。一般来说,可以通过间歇操作(关闭或唤醒合成器)来节省功耗。在这种情况下,如果 PLL 不受控制地通电,则由于参考频率(fr)和比较频率(fp)之间未定义的相位关系,产生的相位比较器输出信号是不可预测的,并且在最坏的情况下可能需要更长的时间来锁定环路。为了防止这种情况,间歇操作控制电路在通电期间强制相位检测器输出有限的误差信号,从而保持环路锁定。在省电模式下,除省电功能必不可少的电路外,相应部分停止工作,然后电流消耗降至 10 µ A(最大值)。此时,Do 和 LD 变为与环路锁定时相同的状态。即,Do 变为高阻抗。VCO 控制电压自然保持在由 LPF 的时间常数定义的锁定电压。因此,VCO 的频率保持在锁定频率。

EN25QX128A (2V) 128 兆位 3V 串行闪存...

该设备是一个 128 兆位(16,384K 字节)串行闪存,具有先进的写保护机制。该设备通过标准串行外设接口 (SPI) 引脚支持单比特和四比特串行输入和输出命令:串行时钟、芯片选择、串行 DQ 0 (DI) 和 DQ 1 (DO)、DQ 2 (WP#) 和 DQ 3 (HOLD#/RESET#)。支持高达 104Mhz 的 SPI 时钟频率,在使用四路输出读取指令时,允许四路输出的等效时钟速率为 532Mhz(133Mhz x 4)。使用页面编程指令,可以一次对内存进行 1 到 256 个字节的编程。该设备还提供了一种复杂的方法来保护单个块免受错误或恶意编程和擦除操作的影响。通过提供单独保护和取消保护块的能力,系统可以取消保护特定块以修改其内容,同时确保内存阵列的其余块得到安全保护。这在以子程序或模块为基础修补或更新程序代码的应用中非常有用,或者在需要修改数据存储段而又不冒程序代码段被错误修改的风险的应用中非常有用。该设备设计为允许一次执行单个扇区/块或全芯片擦除操作。该设备可以配置为以软件保护模式保护部分内存。该设备可以对每个扇区或块维持至少 100K 次编程/擦除周期。

第三代航天级串行双 QSPI P-SRAM™ ...

Avalanche Technology, Inc. 不对因使用本文档中列出的产品或信息而侵犯 Avalanche Technology, Inc. 或第三方的任何知识产权(包括但不限于专利、版权和电路布局许可)承担任何责任。Avalanche Technology, Inc. 或他人的任何专利、版权或其他知识产权均未获得明示、暗示或其他形式的许可。Avalanche Technology, Inc. 保留更改产品或规格的权利,恕不另行通知。有关 Avalanche Technology 产品的更新或其他信息,请联系 Avalanche Technology 办公室。所有品牌名称、商标和注册商标均属于其各自所有者。©2023 Avalanche Technology, Inc.

第三代航天级串行双 QSPI P-SRAM™ ...

Avalanche Technology, Inc. 不对因使用本文档中列出的产品或信息而侵犯 Avalanche Technology, Inc. 或第三方的任何知识产权(包括但不限于专利、版权和电路布局许可)承担任何责任。Avalanche Technology, Inc. 或他人的任何专利、版权或其他知识产权均未获得明示、暗示或其他形式的许可。Avalanche Technology, Inc. 保留更改产品或规格的权利,恕不另行通知。有关 Avalanche Technology 产品的更新或其他信息,请联系 Avalanche Technology 办公室。所有品牌名称、商标和注册商标均属于其各自所有者。©2024 Avalanche Technology, Inc.