XiaoMi-AI文件搜索系统

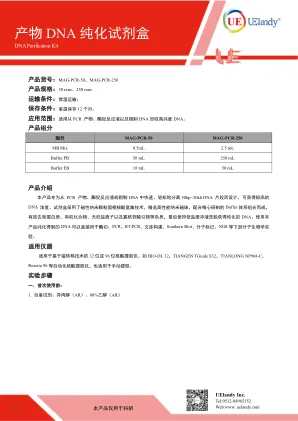

World File Search System产物DNA 纯化试剂盒

适用于基于磁转移技术的 32 位或 96 位核酸提取仪。如 BIO-DL 32 , TIANGEN TGuide S32 , TIANLONG NP968-C ,

abasic位点和DNA单链破裂的影响

抽象的可言位置被认为是最常发生的细胞DNA损伤,并且是自发产生的,也是由于化学或辐射对DNA的损害而产生的。与无碱性位点对DNA聚合酶的影响的丰富信息相反,这些病变与RNA聚合酶如何相互作用知之甚少。使用体外转录系统来确定无碱性位点和单链断裂对转板伸长的影响。DNA模板是构建的,其中包含来自两个不同启动子的独特位置放置在独特位置的单个障碍物或划痕,并由SP6和Escherichia coli RNA聚合酶转录。sp6 RNA聚体最初停滞在Abasic部位,随后,这些病变的有效旁路。大肠杆菌RNA聚合酶也绕过了无碱性位点。相比之下,在无碱性位点引起的单链破裂完全阻断了两个RNA聚合酶的进展。全长转录本的序列分析表明,SP6和大肠杆菌RNA聚合酶插入了原始的,即使不是精心抗拒的腺嘌呤残基与无碱性位点相反。这种FMDing表明,在转录水平上,无碱性位点在体内可能是高度诱变的。

基于忆阻片上系统的超维计算硬件-算法协同设计

超维计算 (HDC) 采用并行计算范式和高效学习算法,非常适合资源受限的人工智能 (AI) 应用,例如边缘设备。基于忆阻设备的内存计算 (IMC) 系统通过提供节能硬件解决方案对此进行了补充。为了充分利用忆阻 IMC 硬件和 HDC 算法的优势,我们提出了一种硬件算法协同设计方法,用于在忆阻片上系统 (SoC) 上实现 HDC。在硬件方面,我们利用忆阻交叉开关阵列固有的随机性进行编码,并采用模拟 IMC 进行分类。在算法层面,我们开发了硬件感知编码技术,将数据特征映射到超维向量中,从而优化了忆阻 SoC 内的分类过程。硬件实验结果表明语言分类任务的准确率为 90.71%,凸显了我们的方法在边缘设备上实现节能 AI 部署的潜力。

研究论文 新型超低功耗镜像折叠级联跨阻放大器

背景和目标:本文首次设计并介绍了一种基于电流镜和折叠级联拓扑组合的新型折叠镜 (FM) 跨阻放大器 (TIA) 结构。跨阻放大器级是接收器系统中最关键的构建块。这种新型拓扑基于电流镜拓扑和折叠级联拓扑的组合,采用有源元件设计。其理念是在输入节点使用电流镜拓扑。在所提出的电路中,与许多其他已报道的设计不同,信号电流(而不是电压)被放大直到到达输出节点。由于使用二极管连接的晶体管作为电流镜拓扑的一部分,所提出的 TIA 具有低输入电阻的优势,这有助于隔离主要输入电容。因此,以相当低的功耗实现了 5Gbps 的数据速率。此外,设计的电路仅使用了六个有源元件,占用的芯片面积很小,同时提供 40.6dBΩ 的跨阻抗增益、3.55GHz 频率带宽和 664nArms 输入参考噪声,并且仅消耗 315µW 功率和 1V 电源。结果证明了所提出的电路结构作为低功耗 TIA 级的正确性能。方法:所提出的拓扑基于电流镜拓扑和折叠级联拓扑的组合。使用 Hspice 软件中的 90nm CMOS 技术参数模拟了所提出的折叠镜 TIA 的电路性能。此外,对晶体管的宽度和长度尺寸进行了 200 次蒙特卡罗分析,以分析制造工艺。结果:所提出的 FM TIA 电路提供 40.6dBΩ 跨阻增益和 3.55GHz 频率带宽,同时使用 1V 电源仅消耗 315µW 功率。此外,由于分析通信应用中接收器电路中输出信号的质量至关重要,所提出的 FM TIA 对于 50µA 输入信号的眼图打开约 5mV,而对于 100µA 输入信号,眼图垂直打开约 10mV。因此,可以清楚地显示眼图的垂直和水平开口。此外,跨阻增益的蒙特卡罗分析呈现正态分布,平均值为 40.6dBΩ,标准差为 0.4dBΩ。此外,FM TIA 的输入电阻值在低频时等于 84.4Ω,在 -3dB 频率时达到 75Ω。通过对反馈网络对输入电阻的影响的分析,得出了在没有反馈网络的情况下,输入电阻可达1.4MΩ,由此可见反馈网络的存在对于实现宽带系统的重要性。结论:本文本文介绍了一种基于电流镜拓扑和折叠级联拓扑组合的跨阻放大器,该放大器可放大电流信号并将其转换为输出节点的电压。由于输入节点存在二极管连接的晶体管,因此 TIA 的输入电阻相对较小。此外,六个晶体管中有四个是 PMOS 晶体管,与 NMOS 晶体管相比,它们的热噪声较小。此外,由于前馈网络中未使用无源元件,因此所提出的折叠镜拓扑占用的片上面积相对较小。使用 90nm CMOS 技术参数的结果显示,跨阻增益为 40.6dBΩ,频率带宽为 3.55GHz,输入参考噪声为 664nArms,使用 1 伏电源时功耗仅为 315µW,这表明所提出的电路作为低功耗构建块的性能良好。

用于神经形态计算的互补金属氧化物半导体和忆阻硬件

数字计算机不断增长的处理能力需求不可能无限期地得到满足,除非计算领域出现范式转变。神经形态计算从大脑的高度并行、低功耗、高速和抗噪声计算能力中汲取灵感,可能带来这样的转变。来自学术界和工业界的许多研究人员一直在研究材料、设备、电路和系统,以实现神经元和突触网络的一些功能,从而开发神经形态计算平台。这些平台采用各种硬件技术设计,包括成熟的互补金属氧化物半导体 (CMOS) 和新兴的忆阻技术,如基于 SiO x 的忆阻器。本文重点介绍了用于神经形态系统的 CMOS、基于 SiO x 的忆阻器和混合 CMOS-忆阻硬件的最新进展。本文提供了各种设备的新成果和已发表成果,这些设备旨在复制神经元、突触和简单脉冲网络的选定功能。结果表明,CMOS 和忆阻设备组装在不同的神经形态学习平台中,以执行简单的认知任务,例如对基于脉冲速率的模式或手写数字进行分类。本文设想,所展示的内容将对非常规计算研究界有用,因为它可以深入了解神经形态硬件技术的进步。

用于神经形态计算的互补金属氧化物半导体和忆阻硬件

除非计算领域出现范式转变,否则数字计算机不断增长的处理能力需求不可能无限期地得到满足。神经形态计算从大脑的高度并行、低功耗、高速和抗噪声计算能力中汲取灵感,可能带来这样的转变。来自学术界和工业界的许多研究人员一直在研究材料、设备、电路和系统,以实现神经元和突触网络的一些功能,从而开发神经形态计算平台。这些平台采用各种硬件技术设计,包括成熟的互补金属氧化物半导体 (CMOS) 和新兴的忆阻技术,如基于 SiO x 的忆阻器。本文重点介绍了用于神经形态系统的 CMOS、基于 SiO x 的忆阻器和混合 CMOS-忆阻硬件的最新进展。本文提供了各种设备的新成果和已发表成果,这些设备是为了复制神经元、突触和简单脉冲网络的选定功能而开发的。结果表明,CMOS 和忆阻设备组装在不同的神经形态学习平台中,以执行简单的认知任务,例如对基于脉冲速率的模式或手写数字进行分类。本文设想,所展示的内容将对非常规计算研究界有用,因为它可以深入了解神经形态硬件技术的进步。

位场数据反演 - 印度科学院

摘要。由于难以获得唯一解,势场数据反演问题是一个具有挑战性的问题。本文确定了各种类型的非唯一性,并认为消除所有类别的非唯一性既不可能也没有必要。某些类型的非唯一性是由于人为的限制和选择造成的,这些类型将永远存在。列出所有解决方案、对可接受的解决方案施加额外约束、先验理想化、使用先验或补充信息、描述所有解决方案的共同点、获得极值解决方案、寻求所有可能解决方案的分布等。面对非唯一性,有各种反应。结果表明,所有这些技术只是改变了非唯一性的形式。讨论了一些用于获得目标函数全局最小值的算法。阐明了看似不同的方法背后的概念共性以及由于不同的公理背景而对相同数值结果进行非唯一解释的可能性。

Renesas Microcomputer 32 位微控制器 V850

注释: 1. 本文档中包含的所有信息截至发布之日均为最新信息。但是,此类信息如有更改,恕不另行通知。在购买或使用此处列出的任何瑞萨电子产品之前,请与瑞萨电子销售办事处确认最新产品信息。此外,请定期仔细关注瑞萨电子将披露的其他信息和不同信息,例如通过我们的网站披露的信息。 2. 对于因使用本文档中描述的瑞萨电子产品或技术信息而导致的或由此引起的第三方专利、版权或其他知识产权的侵权,瑞萨电子不承担任何责任。在此不授予瑞萨电子或其他方的任何专利、版权或其他知识产权的明示、暗示或其他形式的许可。 3. 您不得更改、修改、复制或以其他方式盗用任何瑞萨电子产品,无论是全部还是部分。 4. 本文档中提供的电路、软件和其他相关信息的描述仅用于说明半导体产品的操作和应用示例。您完全有责任将这些电路、软件和信息纳入您的设备设计中。瑞萨电子对您或第三方因使用这些电路而遭受的任何损失不承担任何责任。

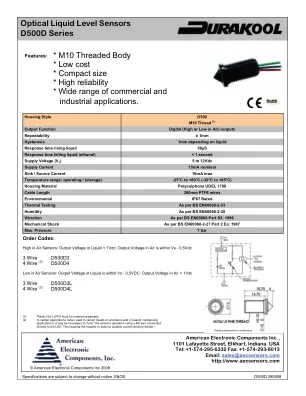

光学液位传感器 D500D 系列

(1) 塑料螺母 LLPK3 必须单独订购。(2) 在某些应用中(在某些液体或乳化液以及重度冷凝应用中使用时),可能需要使用直接连接到 LED 的第 4 根线“调整”传感器的操作。这要求安装人员选择合适的限流电阻器—

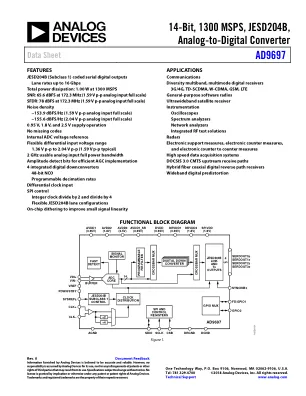

14 位、1300 MSPS、JESD204B 模数转换器

特性 JESD204B(子类 1)编码串行数字输出 通道速率高达 16 Gbps 总功耗:1300 MSPS 时为 1.00 W SNR:172.3 MHz 时为 65.6 dBFS(1.59 V p-p 模拟输入满量程) SFDR:172.3 MHz 时为 78 dBFS(1.59 V p-p 模拟输入满量程) 噪声密度 −153.9 dBFS/Hz(1.59 V p-p 模拟输入满量程) −155.6 dBFS/Hz(2.04 V p-p 模拟输入满量程) 0.95 V、1.8 V 和 2.5 V 电源操作 无丢失代码 内部 ADC 电压基准 灵活的差分输入电压范围 1.36 V p-p 至2.04 V p-p(典型值 1.59 V p-p) 2 GHz 可用模拟输入全功率带宽 幅度检测位,可实现高效的 AGC 实施 4 个集成数字下变频器 48 位 NCO 可编程抽取率 差分时钟输入 SPI 控制 整数时钟除以 2 和除以 4 灵活的 JESD204B 通道配置 片上抖动可改善小信号线性度