XiaoMi-AI文件搜索系统

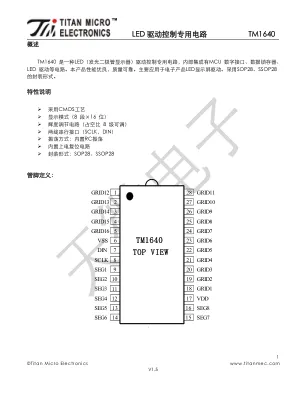

World File Search SystemLED 驱动控制专用电路TM1640

微处理器的数据通过两线总线接口和TM1640 通信,在输入数据时当CLK 是高电平时,DIN 上的信号必须 保持不变;只有CLK 上的时钟信号为低电平时,DIN 上的信号才能改变。数据的输入总是低位在前,高位在后 传输.数据输入的开始条件是CLK 为高电平时,DIN 由高变低;结束条件是CLK 为高时,DIN 由低电平变为高 电平。

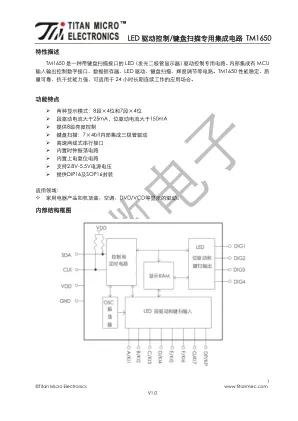

LED 驱动控制/键盘扫描专用集成电路TM1650

接口和TM1650 通信,在输入数据时当SCL 是高电平时,SDA 上的信号必须保持不变;只有SCL 上的 时钟信号为低电平时,SDA 上的信号才能改变。数据输入的开始条件是SCL 为高电平时,SDA 由高变

电镜显微技术

时钟使能 (CKE) 将时钟门控到 SDRAM。如果 CKE 与时钟同步变为低电平(设置和保持时间与其他输入相同),则内部时钟从下一个时钟周期开始暂停,只要 CKE 保持低电平,输出和突发地址的状态就会冻结。CKE 变为低电平后,从下一个时钟周期开始,所有其他输入都将被忽略。当所有存储体处于空闲状态且 CKE 与时钟同步变为低电平时,SDRAM 从下一个时钟周期开始进入断电模式。只要 CKE 保持低电平,SDRAM 就会保持断电模式,忽略其他输入。断电退出是同步的,因为内部时钟被暂停。当 CKE 在时钟高电平沿之前至少“1CLK + t SS ”变为高电平时,SDRAM 将从同一时钟沿变为活动状态,接受所有输入命令。存储体地址 (BA0、BA1)

ICL7135-Farnell-电子工程专辑

当为高电平(或开路)时,A/D 将以每 40,002 个时钟脉冲等间隔的测量周期自由运行。如果为低电平,转换器将继续进行其正在进行的整个测量周期,然后只要 R/H 保持为低电平,转换器就会保持此读数。一个短正脉冲(大于 300 纳秒)现在将启动一个新的测量周期,从 1 到 10,001 个自动归零计数开始。如果脉冲在完成整个测量周期(40,002 个计数)之前发生,则不会识别它,转换器将简单地完成其正在进行的测量。一个完整的测量周期已完成的外部指示是第一个选通脉冲(见下文)将在该周期结束后 101 个计数后发生。因此,如果 Run/HOLD 为低电平并且至少保持 101 个计数为低电平,则转换器处于保持状态并准备在脉冲为高电平时开始新的测量。

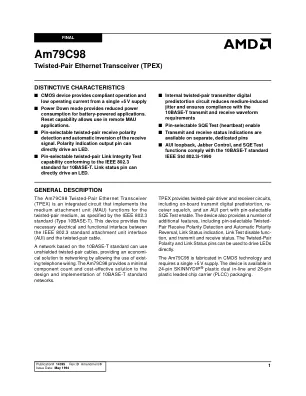

Am79C98 - AMD

除了板载上电复位电路外,PRDN/RST 引脚还用作 TPEX 的主复位。PRDN/RST 必须驱动为低电平至少两微秒才能发生复位。PRDN/RST 引脚还可用于将 TPEX 置于非活动状态,从而使设备消耗更少的电量。此功能在电池供电或低占空比系统中很有用。将 PRDN/RST 驱动为低电平会复位 TPEX 的内部逻辑并使设备进入空闲模式。在此模式下,双绞线驱动器引脚 (TXD+/–、TXP+/–) 驱动为低电平,AUI 引脚 (CI+/–、DI+/–) 驱动为高电平,LNKST 和 RXPOL 引脚处于非活动状态,XMT 和 RCV 为低电平。只要 PRDN/RST 有效,TPEX 就会保持空闲状态。在 PRDN/RST 上的信号上升沿之后,TPEX 会保持复位状态 10

ICL7135-TME

当为高电平(或开路)时,A/D 将以每 40,002 个时钟脉冲等间隔的测量周期自由运行。如果为低电平,转换器将继续进行其正在进行的整个测量周期,然后只要 R/H 保持为低电平,转换器就会保持此读数。一个短正脉冲(大于 300 纳秒)现在将启动一个新的测量周期,从 1 到 10,001 个自动归零计数开始。如果脉冲在完成整个测量周期(40,002 个计数)之前发生,则不会识别它,转换器将简单地完成其正在进行的测量。一个完整的测量周期已完成的外部指示是第一个选通脉冲(见下文)将在该周期结束后 101 个计数后发生。因此,如果 Run/HOLD 为低电平并且至少保持 101 个计数为低电平,则转换器处于保持状态并准备在脉冲为高电平时开始新的测量。

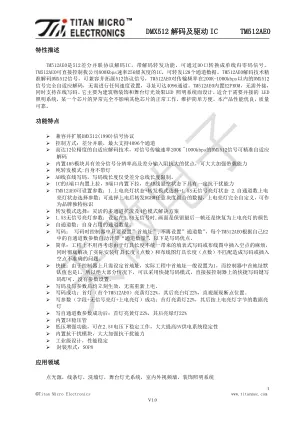

DMX512 解码及驱动IC TM512AE0

特殊说明 TM512AE0 单位 参数名称 参数符号 测试条件 最小值 典型值 最大值 低电平输出电流 Iol Vo =0.4V,ADRO 10 - - mA 高电平输出电流 Ioh Vo =4.6V,ADRO 10 - - mA 输入电流 Ii - - ±1 µA 差分输入共模电压 Vcm 12 V 差分输入电流 Iab VDD=5V 28 µA 差分输入临限电压 Vth 0V

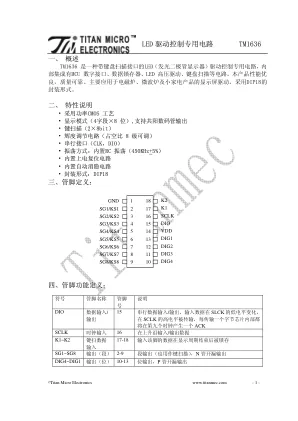

LED 驱动控制专用电路TM1636

在有按键按下时,读键数据如下: SG1 SG2 SG3 SG4 SG5 SG6 SG7 SG8 K1 1110_1111 0110_1111 1010_1111 0010_1111 1100_1111 0100_1111 1000_1111 0000_1111 K2 1111_0111 0111_0111 1011_0111 0011_0111 1101_0111 0101_0111 1001_0111 0001_0111 在无按键按下时,读键数据为: 1111_1111 ; 七、 接口说明 微处理器的数据通过两线总线接口和 TM1636 通信,在输入数据时当 SCLK 是高电 平时, DIO 上的信号必须保持不变;只有 SCLK 上的时钟信号为低电平时, DIO 上的信号 才能改变。数据输入的开始条件是 SCLK 为高电平时, DIO 由高变低;结束条件是 SCLK 为高时, DIO 由低电平变为高电平。 TM1636 的数据传输带有应答信号 ACK ,在传输数据的过程中,在时钟线的第九个 时钟芯片内部会产生一个应答信号 ACK 将 DIO 管脚拉低。 指令数据传输过程如下图(读按键数据时序):

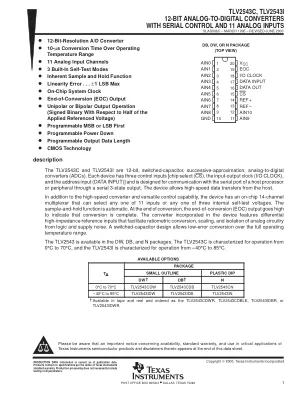

具有串行控制和 11 个模拟输入的 12 位模拟数字转换器数据表 (Rev. C)

在采样期间,其中一个模拟输入内部连接到转换器的电容器阵列以存储模拟输入信号。在四个地址位被输入到输入数据寄存器后,转换器立即开始对所选输入进行采样。采样从 I/O CLOCK 的第四个下降沿开始。转换器保持采样模式,直到 I/O CLOCK 的第八个、第十二个或第十六个下降沿,具体取决于数据长度选择。在最后一个 I/O CLOCK 下降沿的 EOC 延迟时间之后,EOC 输出变为低电平,表示采样周期结束并且转换周期已开始。EOC 变为低电平后,可以更改模拟输入而不会影响转换结果。由于从最后一个 I/O CLOCK 的下降沿到 EOC 低电平的延迟是固定的,因此可以以固定速率数字化随时间变化的模拟输入信号,而不会因时序不确定性而引入系统谐波失真或噪声。