XiaoMi-AI文件搜索系统

World File Search System2.5D/3D 封装和异构集成的技术趋势 Masaya Kawano 新加坡 A*STAR 微电子研究所,kawanom@ime.a-st

除了使用有机基板封装外,为了克服尺寸限制,人们还提出了新的封装技术并将其应用于半导体产品。晶圆级封装 (WLP) 和扇出型晶圆级封装 (FOWLP) 的开发是为了通过采用晶圆工艺而不是基于层压的工艺来进一步缩小封装尺寸。对于亚微米互连,还提出了通过 Si 中介层 (TSI) 进行互连,并用于高密度 2.5D/3D 封装,其中 Cu BEOL 互连可用作再分布层 (RDL)。热压键合 (TCB) 目前用于 2.5D/3D 组装,然而,混合键合将是进一步缩小芯片连接尺寸的关键推动因素,这将在后面讨论。英飞凌于 2006 年提出了一种称为嵌入式晶圆级球栅阵列 (eWLB) 的 FOWLP [1],该技术于 2009 年转让给 STATS ChipPAC 进行批量生产。台积电开发了另一种类型的 FOWLP,称为

山东晶导微电子股份有限公司首次公开发行股票并在创业 ...

声明 ................................................................................................................................................................ 1

幻灯片——用于先进晶圆级封装的苯并环丁烯基介电材料的图案化永久键合

Michael Gallagher、Rosemary Bell、Anupam Choubey、Hua Dong、Joe Lachowski、Jong-Uk Kim、Masaki Kondo、Corey O'Connor、Greg Prokopowicz、Bob Barr、陶氏电子材料

晶圆级芯片封装中早期焊球偶尔脱离对后续微结构演变和焊点疲劳的影响

摘要 — 电子产品的不断小型化与工业和汽车电子产品的严格可靠性要求相结合,是新兴封装技术面临的一大挑战。一方面是增加对环境载荷下损坏的了解。因此,在温度循环测试之后,对组装在印刷电路板 (PCB) 上的晶圆级芯片级封装的焊点进行了分析。在所研究的封装中,有限数量的接头没有与 PCB 铜垫形成适当的机械连接。虽然这并非有意为之,但这些情况会导致这些接头在最初几个热循环内脱落。然而,这种状况提供了一个独特的机会来比较热机械载荷(连接接头)和纯热载荷(脱落接头)后的焊点微观结构,它们直接位于彼此相邻的位置。结果表明,微结构老化效应可以直接与接头中载荷增加的区域联系起来。对于分离的焊点来说尤其如此,它们几乎可以保留其初始微观结构,直到受到热分布高温部分的影响。通过有限元模拟,如果孤立的焊球从板上脱落,可以进一步量化相邻焊点增加的负载。在介绍的一个案例中,角焊点的寿命仅减少了 85%。

在130 nm sige bicmos Technology的Beol中,晶圆级薄膜封装的MM-Wave RF-MEMS开关的单片整合

摘要 - 对于任何微电动机械系统(MEMS)设备的工厂最为明显的挑战之一,是该设备的低成本和高吞吐包装,以保护其免受环境颗粒,水分和配置的影响。在这项工作中,通过晶状级别CMOS(BICMOS)技术的130 nm双极CMOS(BICMOS)技术的RF-MEMS开关单一地整合到基于铝的后端线(BEOL)中,这是通过晶状级级别的薄级薄薄薄层薄层包装(WLE)。在晶片级封装包装之前,开发并证明了用于释放MEMS设备的湿式和蒸气释放技术。最终装置的封装是用Ti/Tin/Tin/Alcu/Ti/Tin层的堆栈实现为3- µm金属网格的晶圆级包装的。最后,将具有高沉积速率(HDR)的二氧化硅沉积过程用于释放孔的完整封装。通过低频C - V和D-Band时高频S-参数测量值评估了封装对RF-MEMS开关性能的影响。结果指示设备的完整功能,没有明显的性能下降。封装不需要额外的掩码,并且将其开发为8英寸晶圆级工艺,因此为RF-MEMS设备封装和包装提供了低成本和高吞吐量解决方案。

优化芯片准备和处理以实现高产量混合芯片到晶圆键合

摘要 混合铜/电介质键合是一种成熟的晶圆对晶圆 (W2W) 键合技术,但将该技术应用于芯片对晶圆 (D2W) 键合却具有挑战性。芯片或晶圆上的极小颗粒可能会导致空隙/非键合区域。用于混合 W2W 的晶圆清洁和激活工艺已经相当成熟,但将其应用于减薄和单片化芯片进行 D2W 键合却非常具有挑战性。为了允许(部分)重复使用现有的晶圆级清洁、计量和激活工艺和设备,我们提出了一个新概念,即在玻璃载体晶圆上对芯片进行单片化、清洁和激活。在完成芯片准备步骤后,直接从载体晶圆上拾取芯片。这种方法不需要额外的拾取和放置步骤,并且避免使用传统的切割胶带。使用这种新方法进行的首次直接电介质 D2W 键合实验显示出非常有希望的键合产量,键合的 50 µm 薄芯片数量众多,完全没有空隙。此外,通过消除切割胶带,减薄晶圆和单个芯片始终由刚性表面支撑,从而实现超薄芯片处理。在本研究中,我们还报告了厚度小于 10 µm 的芯片的处理。关键词载体系统、混合键合、互连、拾取和放置、薄芯片

198/192 系列 200 毫米晶圆运输载具

晶圆加工技术的趋势要求晶圆载体技术不断进步,以支持当今先进的半导体加工设施。我们的 198/192 系列 200 毫米晶圆运输载体可满足当今 200 毫米晶圆厂的自动化、污染控制和生产力要求。这些开放式侧壁晶圆载体专为先进的晶圆运输而设计,与传统的中低端晶圆载体相比,具有显著的性能优势,包括精确的晶圆存取、可靠的设备操作和安全的晶圆保护。

在 300 毫米玻璃晶圆上大规模制造表面离子阱

由于其优异的介电性能,玻璃可以作为表面离子阱制造中石英或蓝宝石的低成本替代材料。与高电阻率(5000 Ω·cm)硅衬底(20 MHz 时的典型损耗角正切为 1.5)相比[24],本文采用的玻璃衬底(Corning SGW 8.5)在 5 GHz 时的损耗角正切为 0.025,体积电阻率为 10 10 Ω·cm(数据可从产品信息表获得)。这省去了硅阱所需的射频屏蔽层和绝缘层,并使制造程序变得更加简单。此外,透明玻璃(波长为 300 至 2400 nm 的透射率为 90%)可以使光的传输和收集更加灵活,例如,通过在下面放置光纤和/或光电探测器。 [25]与其他介电材料(如蓝宝石和石英)相比,玻璃不仅成本低,而且可制造性更先进,可以实现高可靠性的玻璃通孔、[26,27]阳极键合、[28]

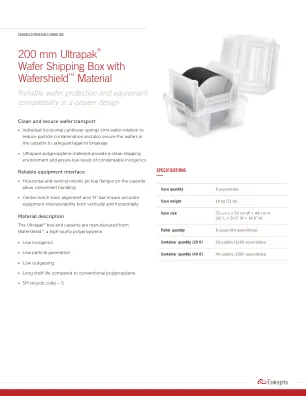

200 毫米 Ultrapak® 晶圆运输盒,采用 Wafershield™ 材料

Entegris ® 、Entegris Rings Design ® 和其他产品名称是 Entegris, Inc. 的商标,如 entegris.com/trademarks 所列。所有第三方产品名称、徽标和公司名称均为其各自所有者的商标或注册商标。使用它们并不表示商标所有者与它们有任何关联、赞助或认可。