XiaoMi-AI文件搜索系统

World File Search System采用有源电感的CMOS 3.5 GHz带宽低噪声放大器

(17)

信函 TSV 电感器的交流电感和品质因数分析模型

片上电感是射频集成电路 (RFIC) 中的重要无源器件 [1]。利用硅通孔 (TSV) 的 3-D 封装技术开创了片上电感、电容、滤波器等无源元件的实现 [2、3、4、5、6、7、8、9、10、11、12、13、14、15、16、17、18、19]。与传统的 2-D 电感相比,基于 TSV 的 3-D 电感具有电感密度高、体积小的优势 [20、21、22、23、24]。一些研究主要针对基于 TSV 的电感的直流电感建模。基于 3-D 全波仿真获得的 Y 参数,提出了经验近似表达式 [25, 26]。但它很耗时并且在物理上不严谨。[27] 提出了一种基于 TSV 的螺旋电感直流电感的解析模型,该模型据称很简单,但用该模型确定电感是一项非常困难的任务,因为它需要至少 4 N + 2 C 2 N + 1 次计算才能获得 N 匝电感的电感,其中 C 2 N 表示组合,它取决于电感匝数。此外,据我们所知,尚无关于基于 TSV 的螺旋电感的交流电感和品质因数的解析模型的报道。在本文中,提出了基于 TSV 的螺旋电感的直流电感公式。基于该公式及等效电路模型,建立了TSV基螺旋电感的交流电感及品质因数的分析模型

tongsheng Times仅使用

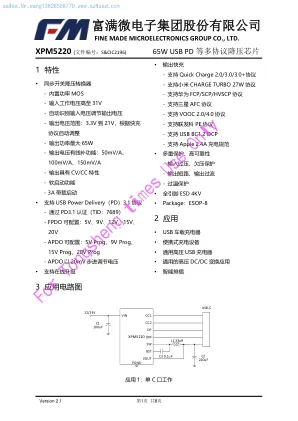

XPM5220 集成双路低阻抗 NMOS ,从而提供较高的转换效率。 High-side NMOS 内阻为 72 mΩ , Low-side NMOS 内阻为 31 mΩ 。在输入接入 100uF 电解电容,输 出接入 220uF 电解电容, 33uH 电感的测试条件下, XPM5220 的转换效率曲线如下 图所示。

超级电容器、超级电感器形式的超级元件

由无源元件组成的电路元件对于实现高能量和功率密度具有重要意义,并且电路的研究结果接近准确。本文阐明了在不同应用中实现高电导率、电感和电容值的可能方法,并讨论了它们的组合。主要目标是获得高电感、电容和电导值。超级电容器是一种适用于脉冲功率应用的脉冲装置,其技术已在各种应用中得到充分认可。然而,超级电感的概念很新,它可以为大量应用开辟可能性。本文旨在通过对超级电容器和超导体超级电感的分析方法,简要介绍和提供有关实现超级电感的可能性的信息,概述相对磁导率和电感值、优点和应用。

八nB层完全平面的150 nm节点...

•为了基于SC2节点,我们使用自换连接器和150 nm的电感器设计测试电路,并进行了制造和测试,例如DC-SFQ和SFQ-DC转换器,平衡比较器,SFQ和QFP逻辑,Ac-Ac-ships exhips cubsister,Ac-Ac-ships expressers,Ac-Ac-ships Expisters等。,我们通过在最接近堆栈中JJ层的NB层上实现了150 nm线宽电感的单层通过在NB层上实现150 nm线宽电感的单层,从而证明了电路密度的增加约2倍。对于具有600-µA/µm 2自换的约瑟夫森连接的移位寄存器,我们达到的电路密度为1.3∙107 JJS/cm 2,因此超过了每1 cm 2芯片的10m JJS阈值,在大尺度超尺寸超大型电子系统中应用所需的集成量表所需的集成规模所需。

基于有源电感、具有大输出电压摆幅的高线性度 10 Gb/s MOS 电流模式逻辑驱动器

一些设计挑战[18,19]。有源电感使用晶体管构建,因此电压摆幅低于无源电感,因为晶体管需要较大的电压余量。并且晶体管的非线性特性使有源电感的电感阻抗随偏置点而变化[20]。当有源电感工作在相对较大的电压摆幅下时,输出阻抗的变化很大。为了增加输出电压摆幅,做了一些其他的工作[21-23]。它们克服了阈值电压的限制,因此所需的电压余量降低了,但是晶体管非线性的影响仍然存在。为了使阻抗变化可接受,它们仅对输出电压摆幅提供有限的增加。

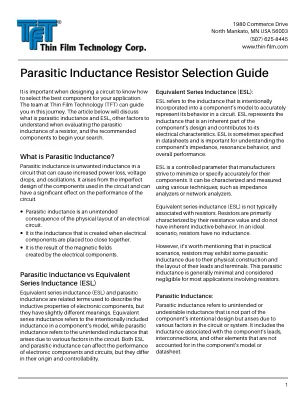

寄生电感电阻选择指南

电流检测电阻是低欧姆电阻,通常小于 1 欧姆。这些电阻不能屏蔽寄生电感的影响,而是有助于整体抵消影响。当电阻较低时,阻抗会随着频率的升高而增加。这意味着具有高频分量的交流电流(例如锯齿波)会产生不准确的检测结果。当交流电流流过低电阻电阻时,电阻两端的电压降是电阻引起的电压降和电感引起的电压降之和。为确保准确的电流检测,建议使用电感最小的低电阻电阻进行大电流检测。

多层超导集成电路中的电感噪声耦合

超导低温电路是一种新兴的节能技术,可以替代或补充现有的 CMOS VLSI 系统。最先进的超导电路利用十多个铌层作为逻辑电路和互连。这些系统中存在多个电感耦合噪声源。本文评估了这些电感噪声源,并讨论了耦合噪声的影响。特别是,本文描述并讨论了无源传输线中耦合噪声的影响,其中数据信号的幅度异常小。本文还描述了偏置电流耦合到逻辑门内电感的影响,因为逻辑门需要精确的偏置条件。本文提供了管理耦合噪声有害影响的指南。

InP HEMT 的分布式小信号等效电路建模方法

2. 1 寄生电感 小信号外参数提取方法的关键是简化图 1 中某一特定偏置点处的等效电路。在冷夹断条件下( V ds =0 , V gs < - V th ),漏源电流源和输出电导可忽略不计,因此耗尽区可以用三个电容 C ig 、 C id 和 C igd 来表征,如图 2 所示。通常先提取寄生电容,无法消除寄生电感的影响,因此在提取寄生电容之前必须先去嵌入寄生电感 L g 、 L d 和 L s ,这也是本文方法与 Gao 等方法的不同之处

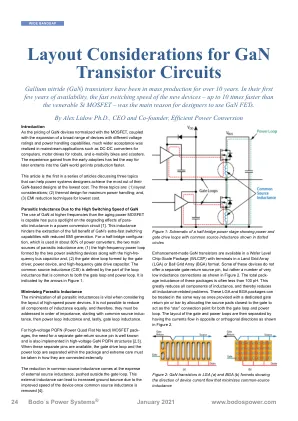

GaN 晶体管电路的布局考虑因素

GaN 高开关速度导致的寄生电感 GaN 的使用频率高于老化功率 MOSFET 所能承受的频率,这使得寄生电感在电源转换电路中的劣化效应成为焦点 [1]。这种电感妨碍了 GaN 超快速开关能力的全部优势的发挥,同时降低了 EMI 产生。对于大约 80% 的电源转换器使用的半桥配置,寄生电感的两个主要来源是:(1) 由两个功率开关器件以及高频总线电容器形成的高频功率环路,以及 (2) 由栅极驱动器、功率器件和高频栅极驱动电容器形成的栅极驱动环路。共源电感 (CSI) 由环路电感中栅极环路和功率环路共有的部分定义。它由图 1 中的箭头指示。