XiaoMi-AI文件搜索系统

World File Search System现场 IT 技术员 - 佐治亚州萨凡纳

• Concur、eTime、RMA、2579 报告等) 差旅/体力需求 认证 EST 职位需要交付、安装和维修涉及我们客户的设备。您需要根据需要操作大型设备。该职位的体力要求有时可能需要大量和/或重复弯曲、停止、抬起和爬梯子。 Henry Schein, Inc. 是一家提供平等就业机会的雇主,不会因种族、肤色、宗教、信仰、国籍、血统、可以合理安置而不会造成过度困难的残疾、性别、性取向、性别认同、年龄、公民身份、婚姻或退伍军人身份或任何其他受法律保护的身份歧视申请人或员工。有关 Henry Schein 职业机会的更多信息,请访问我们的网站:www.henryschein.com/careers

CRPF 萨马查尔:2006eng

共和国日是印度建国的庆典,当看到英勇的士兵向总统和国旗致敬时,所有爱国人士的心都激动不已。现在是重温我们誓言的时候了,誓言要为国家服务到最后一口气。

HI5662 数据表 | 瑞萨电子

HI5662 是一款双 8 位全差分采样流水线 A/D 转换器,具有数字纠错逻辑。图 14 描述了前端差分输入差分输出采样保持 (S/H) 放大器的电路。开关由内部采样时钟控制,该时钟是来自主采样时钟的非重叠两相信号 1 和 2 。在采样阶段 1 ,输入信号施加到采样电容器 C S 。同时,保持电容器 C H 放电至模拟地。在 1 的下降沿,输入信号在采样电容器的底板上进行采样。在下一个时钟相位 2 中,采样电容器的两个底板连接在一起,保持电容器切换到运算放大器输出节点。然后电荷在 C S 和 C H 之间重新分配,完成一个采样保持周期。前端采样保持输出是模拟输入的全差分采样数据表示。该电路不仅执行采样保持功能,还将单端输入转换为转换器核心的全差分输出。在采样阶段,I/Q IN 引脚仅看到开关的导通电阻和 C S 。这些组件的相对较小的值导致转换器的典型全功率输入带宽为 250MHz。

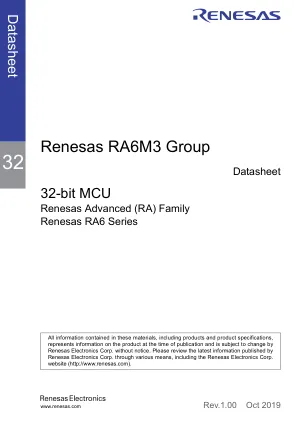

瑞萨 RA6M3 组数据表

USB 2.0 高速 (USBHS) 模块 USB 2.0 高速 (USBHS) 模块可作为主机控制器或设备控制器运行。作为主机控制器,USBHS 支持通用串行总线规范 2.0 中定义的高速传输、全速传输和低速传输。作为设备控制器,USBHS 支持通用串行总线规范 2.0 中定义的高速传输和全速传输。USBHS 具有内部 USB 收发器,并支持通用串行总线规范 2.0 中定义的所有传输类型。USBHS 具有用于数据传输的 FIFO 缓冲区,最多可提供 10 个管道。根据外围设备或通信系统,可以为管道 1 至 9 分配任意端点编号。请参阅用户手册中的第 33 节“USB 2.0 高速模块 (USBHS)”。

PFC 的数字电源控制 - 瑞萨

io_set_cpg :执行 PLL 初始化 WDT.WRITE.WTCSR = 0xa51e; => WDT 停止,WDT 计数时钟设置 => 1/4096 x P 时钟(50MHz;20.97 毫秒) WDT.WRITE.WTCNT = 0x5a85; => 计数器初始设置 10 毫秒 CPG.FRQCR.WORD = 0x0303; => Clockin = 12.5MHz => I 时钟 = 200MHz,B 时钟 = 50MHz => P 时钟 = 50MHz CPG.MCLKCR.BIT.MSDIVS = 1; => MTU2S = 100MHz CPG.ACLKCR.BIT.ASDIVS = 3; => AD = 50MHz STB.CR3.BYTE = 0x02; => 模块待机清除 => HIZ、MTU2S、MTU2、POE2、IIC3、ADC0、保留(1)、FLASH STB.CR4.BYTE = 0xE2; => 模块待机清除 => SCIF3、保留(0)、CMT、保留(1)、EtherC STB.CR5.BYTE = 0x12; => 模块待机清除 => SCI0、SCI1、SCI2、SCI4、ADC1 pfc_init:执行 MTU2 初始化 ADC0.ADCR.BIT.ADCS = 0x0; => AD0 初始化 ADC0.ADANSR.BIT.ANS0 = 0x1; ADC0.ADANSR.BIT.ANS1 = 0x1; ADC0.ADANSR.BIT.ANS2 = 0x1; ADC0.ADANSR.BIT.ANS3 = 0x1; ADC0.ADBYPSCR.BIT.SH = 0x1; ADC1.ADCR.BIT.ADCS = 0x0; => AD1 初始化 ADC1.ADANSR.BIT.ANS0 = 0x1; ADC1.ADANSR.BIT.ANS1 = 0x1; ADC1.ADANSR.BIT.ANS2 = 0x1; ADC1.ADANSR.BIT.ANS3 = 0x1; MTU2S.TSTR.BYTE = 0x0; => 清除 MTU2S 计数器 MTU2S3.TCR.BIT.TPSC = 0x0; => MTU2S3 TCNT 清除禁用 MTU2S3.TCR.BIT.CKEG = 0x0; => MTU2S3 在上升沿计数 MTU2S4.TCR.BIT.TPSC = 0x0; => MTU2S4 TCNT 清除禁用 MTU2S4.TCR.BIT.CKEG = 0x0; => MTU2S4 在上升沿计数 MTU2S.TDDR = 1; => MTU2S 死区时间 MTU2S3.TGRB = 495; MTU2S3.TGRD = 495; MTU2S4.TGRA = 300; => PFC 输出 MTU2S4.TGRC = 300; => PFC 输出 MTU2S4.TGRB = 200; => PFC 输出 MTU2S4.TGRD = 200; => PFC 输出 MTU2S.TCDR = 500; => 三角波形设置 100K MTU2S.TCBR = 500; => 三角波形设置 100K MTU2S3.TGRA = 501; => 三角波形设置 100K MTU2S3.TGRC = 501; => 三角波形设置 100K MTU2S.TOCR1.BIT.PSYE = 0x1; => 切换输出 MTU2S.TOCR1.BIT.TOCS = 0x1; MTU2S.TOCR2.BIT.OLS3N = 0x0; => TIOC4D MTU2S.TOCR2.BIT.OLS3P = 0x1; => TIOC4B MTU2S.TOCR2.BIT.OLS2N = 0x1; => TIOC4C MTU2S.TOCR2.BIT.OLS2P = 0x0; => TIOC4A MTU2S.TOCR2.BIT.OLS1N = 0x0; => TIOC3D MTU2S.TOCR2.BIT.OLS1P = 0x1; => TIOC3B MTU2S3.TMDR.BIT.MD = 0xF; => 峰值时输出高电平 MTU2S.TOER.BIT.OE3B = 0x1; => TIOC3B 引脚输出 MTU2S.TOER.BIT.OE3D = 0x1; => TIOC3D 引脚输出

半导体可靠性手册 |瑞萨

7. 尽管瑞萨电子致力于提高瑞萨电子产品的质量和可靠性,但半导体产品具有以一定比率发生故障和在特定使用条件下发生故障等特定特性。此外,瑞萨电子产品不采用抗辐射设计。请确保实施安全措施,以防止瑞萨电子产品发生故障或故障时造成人身伤害、火灾造成的伤害或损害以及社会损害,例如硬件和软件的安全设计(包括但不限于冗余、火灾控制和故障预防)、老化退化的适当处理或任何其他由您自行负责的适当措施,作为对您产品/系统的保修。由于单独评估微机软件非常困难且不切实际,请评估您制造的最终产品或系统的安全性。

瑞萨 RA6M3 组数据表

USB 2.0 高速 (USBHS) 模块 USB 2.0 高速 (USBHS) 模块可用作主机控制器或设备控制器。作为主机控制器,USBHS 支持通用串行总线规范 2.0 中定义的高速传输、全速传输和低速传输。作为设备控制器,USBHS 支持通用串行总线规范 2.0 中定义的高速传输和全速传输。USBHS 具有内部 USB 收发器,支持通用串行总线规范 2.0 中定义的所有传输类型。USBHS 具有用于数据传输的 FIFO 缓冲区,最多可提供 10 个管道。可以根据外围设备或通信系统为管道 1 至 9 分配任意端点编号。请参阅用户手册中的第 33 节“USB 2.0 高速模块 (USBHS)”。

萨努拉·汗·穆罕默德

本文包含的前瞻性陈述代表 Wipro 对未来事件的看法,其中许多事件本质上具有内在不确定性,不受 Wipro 控制。此类陈述包括但不限于有关 Wipro 的增长前景、未来财务运营业绩以及计划、预期和意图的陈述。Wipro 提醒读者,本文包含的前瞻性陈述受风险和不确定性的影响,可能导致实际结果与此类陈述预期的结果存在重大差异。这些风险和不确定因素包括但不限于:关于我们盈利、收入和利润波动的风险和不确定因素、我们创造和管理增长的能力、完成拟议的公司行动、IT 服务领域的激烈竞争、我们保持成本优势的能力、印度工资上涨、我们吸引和留住高技能专业人员的能力、固定价格、固定时间框架合同的时间和成本超支、客户集中度、移民限制、我们管理国际业务的能力、我们重点关注领域的技术需求减少、电信网络中断、我们成功完成和整合潜在收购的能力、我们服务合同的损害赔偿责任、我们进行战略投资的公司的成功、政府财政激励措施的撤销、政治不稳定、战争、在印度以外筹集资金或收购公司的法律限制、对我们知识产权的未经授权的使用以及影响我们业务和行业的一般经济状况。我们向美国证券交易委员会提交的文件更详细地描述了可能影响我们未来经营业绩的其他风险,包括但不限于 20-F 表年度报告。这些文件可在 www.sec.gov 上查阅。我们可能不时做出额外的书面和口头前瞻性声明,包括公司提交给美国证券交易委员会的文件和我们给股东的报告中包含的声明。我们不承诺更新我们或代表我们不时做出的任何前瞻性声明。