XiaoMi-AI文件搜索系统

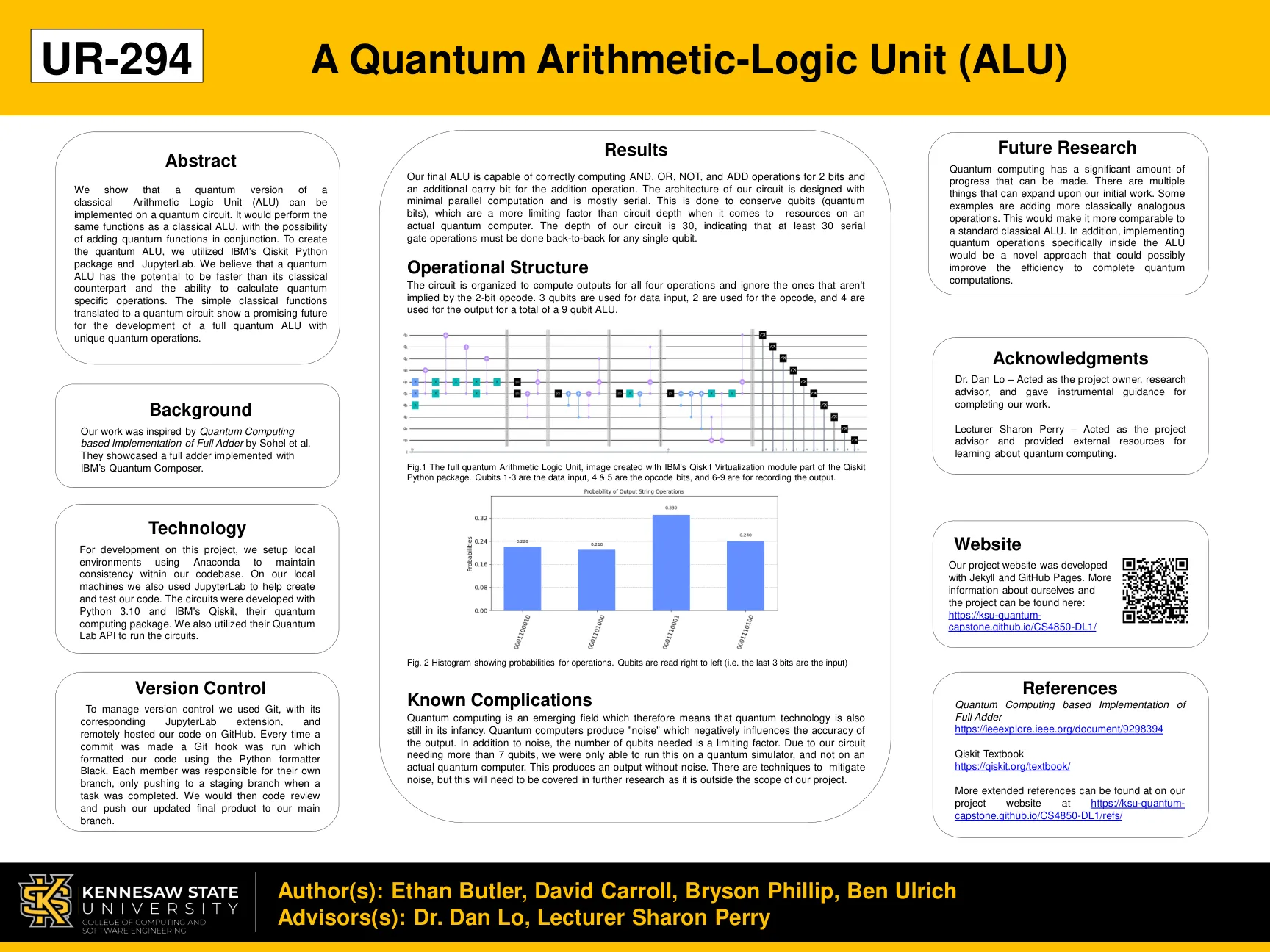

World File Search SystemUR-294量子算术逻辑单元

我们表明,可以在量子电路上实现经典算术逻辑单元(ALU)的量子版本。它将执行与经典ALU相同的功能,并可能在结合中添加量子函数。为了创建量子alu,我们使用了IBM的Qiskit Python软件包和Jupyterlab。我们认为,量子ALU具有比其经典对应物更快的潜力和计算量子特定操作的能力。简单的经典函数转化为量子电路显示出具有独特量子操作的完整量子ALU的前途未来。

使用CNTFET的高速低功率4位ALU设计

摘要 - 由于电子半导体部门经历了缩小规模,因此存在许多挑战,包括缩放,短通道影响,泄漏电流和稳定性。碳纳米管(CNT)已成为一种令人兴奋的新发明,可以克服CMO的局限性,同时保持高效率和可靠性。算术和逻辑单元(ALU)是微处理器和实时计算机芯片中存在的中央操作可编程逻辑组件。传统的算术逻辑单元(ALUS)是利用CMOS技术创建的,导致高功率使用,延迟以及晶体管计数。本文专门讨论了采用碳纳米管现场效应晶体管(CNTFET)的混合算术逻辑单元(ALU)的概念化和开发。首先,开发了XOR和MUX的组合,然后将其用于创建混合加法器和减法器。该研究展示了利用碳纳米管(CNT)技术的增强算术逻辑单元(ALU)的开发,模拟和评估,并将其与使用32 NM技术节点进行了将其与传统的CMOS实施进行了比较。使用碳纳米管(CNT)技术的ALU在功率使用情况,传播延迟和功率 - 延迟产品(PDP)方面的性能较高,而与CMOS技术相比。

新型高功能容错 ALU

小型化、成本、功能性、复杂性和功耗是电路设计中需要注意的重要且必要的设计特性。小型化和功耗之间存在权衡。智能技术一直在寻找新的范例来继续改善功耗。可逆逻辑是部署以避免功耗的智能计算之一。研究人员提出了许多基于可逆逻辑的算术和逻辑单元 (ALU)。然而,容错 ALU 领域的研究仍在进行中。本文的目的是通过使用奇偶校验保留逻辑门来弥补容错领域新研究人员的知识空白,而不是通过各种来源搜索大量数据。本文还介绍了一种基于高功能的新型容错算术和逻辑单元架构。以表格形式显示了优化方面的比较,结果表明,所提出的 ALU 架构在可逆逻辑综合的所有方面都是最佳平衡。所提出的 ALU 架构采用 Verilog HDL 进行编码,并使用 Xilinx ISE design suite 14.2 工具进行仿真。所提出的架构中使用的所有门的量子成本均使用 RCViewer + 工具进行验证。

使用 ... 实现的 32 位 ALU 性能优化

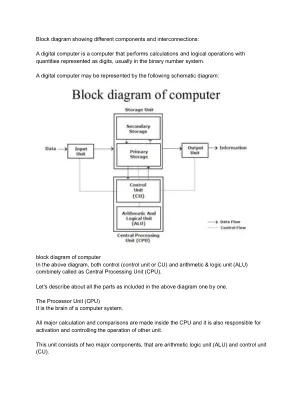

在当今快速发展的技术中,许多设备的尺寸都非常小,通常以纳米为单位,而算术逻辑单元 (ALU) 在这些系统中必不可少。ALU 负责对二进制数据执行数学和逻辑任务,二进制数据由基本计算机语言零和一组成。算术逻辑单元 (ALU) 是中央处理器 (CPU) 处理计算的主要组件,它解码 CPU 命令并执行加法、减法、乘法和比较等运算,以促进有效的数据处理。在获得二进制输入后,ALU 执行诸如加法之类的任务,然后将结果传输到 CPU 以用于其他目的。除了算术函数之外,ALU 还执行逻辑运算,例如 AND、OR、XOR 和 NOT,这些对于数据比较和决策至关重要。作为计算机设计中的关键元素,ALU 在执行从基本数学运算到复杂数据处理的各种功能中起着至关重要的作用,在当今的计算机系统中至关重要。

CIE IGCSE 计算机科学复习笔记 2023

控制单元控制 CPU 周围的数据流。控制单元还向不同组件发送控制信号,指示它们执行哪些操作,例如读取、写入、添加、减去。控制单元解码指令(转换为操作码和操作数)。控制单元控制操作的时间(时钟速度)。算术逻辑单元 (ALU) 执行执行指令所需的计算,包括加法和减法。ALU 还执行逻辑运算,如比较。ALU 有一个内置寄存器,用于存储计算的临时结果

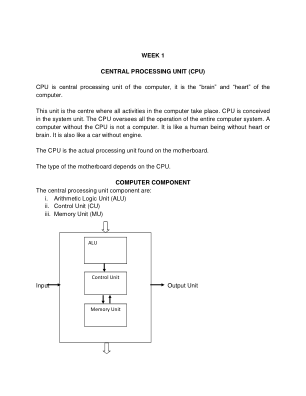

第 1 周 中央处理单元 (CPU) ...

算术逻辑单元也称为整数单元 (IU)。控制单元 (CU) 处理所有处理器控制信号。它指挥所有输入和输出流,从微程序中获取指令代码,并通过提供控制和时序信号指挥其他单元和模型。CU 组件被视为处理器的大脑,因为它向几乎所有事物发出命令并确保正确执行指令。CU 从指令和状态寄存器获取输入。其操作规则或微程序编码在可编程逻辑阵列 (PLA)、随机逻辑或只读存储器 (ROM) 中。控制单元是 CPU 的重要组成部分。它充当计算机的主管。它控制和协调计算机系统的所有活动。它还维护计算机系统中流量和数据流的顺序。计算机内存是存储数据、程序和信息的存储位置。

计算机应用程序 - 注释bba/b.com(ii sem- ...

(2)算术逻辑单元(A.L.U): - 该单元执行所有基本的算术操作,例如加法,减法,乘法,除法,以及逻辑操作,例如数字的比较等。ALU负责在处理操作过程中实际执行指令。存储在内存单元中的数据和指令在需要时转移到ALU中进行处理,并在处理结束时转移回存储器。处理完成后,将最终结果存储在发送到输出单元之前的内存中。alu还组成了许多称为寄存器的小型存储位置。此寄存器的容量很小,并且包含接下来要执行的数据和说明。