XiaoMi-AI文件搜索系统

World File Search System在恒定深度

NISQ(嘈杂的中等规模quantum)之间的方法没有任何证据证明量子优势和完全容忍断层的量子计算,我们提出了一种方案,以实现可证明的可证明的超级物质量子量子(在某些广泛接受的复杂性构想)中,可以与微型误差误差校正要求有稳健的噪声。我们选择一类采样问题,其中包括稀疏的IQP(瞬时Quantum Quantumial多项式时间)电路,我们通过引入Tetrahelix代码来确保其耐断层的实现。通过合并几个四面体代码(3D颜色代码)获得此新代码,并且具有以下属性:每个稀疏的IQP门都允许横向启动,并且逻辑电路的深度可以用于其宽度。结合在一起,我们获得了任何稀疏的IQP电路的Depth-1实现,直到编码状态的制备。这是以一个空间为代价的,这仅在原始电路的宽度中是多毛体。我们还表明,也可以通过经典计算的单一步骤进行恒定深度进行状态准备。因此,我们的构造表现出在恒定深度电路上实现的采样问题,具有强大的超多种量子量子优势,并具有一轮的测量和进率。

制造和应用方面的最新技术进步......

图 1. 当今正在开发的有机电化学晶体管 (OECT) 示意图,涵盖简便的制造技术和广泛的应用。印刷工艺:丝网印刷,经许可改编,[57] 版权所有 2019,Wiley-VCH;喷印,经许可改编,[58] 版权所有 2020,美国化学学会。基于激光的图案化:激光烧蚀图案化,经许可改编,[59] 版权所有 2012,Wiley-VCH;激光图案化 OECT,经许可改编,[60] 版权所有 2020,IOP Publishing Ltd. 纳米压印光刻:S/D 纳米压印,经许可改编,[61] 版权所有 2016,Wiley-VCH;有源层纳米压印,经许可改编,[62] 版权所有 2013 SID。基于纤维的图案化:基于纳米纤维的图案化,经许可改编,[63] 版权所有 2019,美国化学学会;基于编织的,经许可改编,[53] 版权所有 2011,Wiley-VCH。生物传感器:葡萄糖传感器,经许可改编,[64] 版权所有 2019,Springer Nature;离子传感器,经许可改编,[65] 版权所有 2018,Wiley-VCH。逻辑电路:逆变器和 NAND,经许可改编,[46] 版权所有 2019,Springer Nature;惠斯通电桥,经许可改编,[66] 版权所有 2017,Wiley-VCH。神经形态装置:纳米线人工突触,经许可改编,[67]

用于生物医学应用的宽带隙半导体可拉伸 3D 微结构的工程路线 (Adv. Funct. Mater. 34/2023)

宽带隙 (WBG) 半导体引起了广泛的研究兴趣,用于开发广泛的柔性电子应用,包括可穿戴传感器、软逻辑电路和长期植入式神经调节器。传统上,这些材料在标准硅基板上生长,然后使用机械冲压工艺转移到软聚合物上。该技术可以在转移后保留宽带隙材料的优异电学性能并实现柔性;然而,与三维生物系统相比,大多数设备受到二维配置的限制,其机械拉伸性和形态有限。本文提出了一种无冲压微加工工艺,首次实现了三维柔性可拉伸宽带隙电子器件。该方法在独立纳米膜的两侧都应用光刻技术,可以直接在标准硅晶片上形成柔性结构,以调整材料的光学透明度和机械性能。随后,柔性器件从支撑基板上分离,并进行受控机械屈曲,将宽带隙半导体的二维前体转变为复杂的三维中尺度结构。制造具有三维架构的宽带隙材料的能力,这些材料具有器件级可拉伸性,并具有多模传感能力,将极大地促进先进三维生物电子界面的建立。

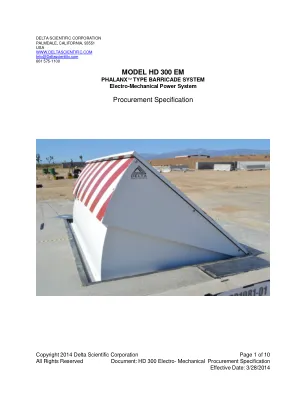

HD300-EM-路障-采购-规范.pdf

全面碰撞认证概要 全面碰撞测试认证 HD 300 路障系统已通过美国最高车辆路障标准的测试和认证。 此路障超过了 ASTM F 2656-07 M50 P1 的标准。独立测试实验室的测试证实,它能够阻止并摧毁高速行驶的重载卡车,并能承受第二次攻击。 1.0 范围 全面碰撞测试认证 本规范定义了 PHALANX SYSTEM、型号 HD 300 EM 的采购,由(一、二、三或四)个车辆路障组成(独立或成组两个、三个或四个)路障,每个路障都安装了独立的机电执行器和专有的平衡系统。 电源系统、控制和逻辑电路、功能和选项,如本文所定义。 安全和环境选项包括信号灯、门臂护栏;安全回路;红外线、加热器和污水泵。 触摸屏控制面板或按钮控制面板。遥控器和主控器。2.0 现场具体要求 2.1 护栏板安装后应提供相对于周围道路的水平或共面表面。(参考联邦公路项目道路和桥梁建设标准规范 FP-96)2.2 护栏板本身应连续,无焊接接头、可拆卸部分或螺栓固定的路板,但小型通道除外

用生物学约束深度学习体系结构解释V1属性

卷积神经网络(CNN)最近已成为腹侧视觉流的有前途的模块。虽然主要视觉皮层(V1)的当前最新模型已经从具有对抗性示例的训练中浮出水面并广泛增强了数据,但这些模型仍然无法解释V1中观察到的关键神经特性,这些神经特性是由生物逻辑电路引起的。为了解决这一差距,我们系统地将神经科学衍生的架构组件纳入CNN中,以确定一组更全面地解释V1活动的机制和体系结构。通过使用建筑组件增强任务驱动的CNN,这些组件模拟了中心旋转的拮抗作用,局部接收场,调整归一化和皮质放大倍数,我们以潜在的表示模型来产生V1神经活动和调谐特性的潜在模型。此外,对这些成分的学习参数和最大激活评估网络神经元的刺激的分析为它们在解释V1的神经特性中的作用提供了支持。我们的结果突出了神经ai领域的重要进步,因为我们系统地建立了一组建筑成分,这些组件有助于v1的前所未有的解释。可以从越来越准确的大脑内部模型中收集的神经科学见解有可能大大推进神经科学和人工智能的领域。

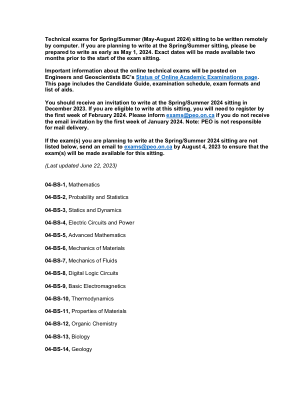

春季/夏季(2024 年 5 月至 8 月)考试的技术考试将通过计算机远程进行。如果您计划参加春季/夏季考试,

春夏季 (2024 年 5 月至 8 月) 技术考试将通过计算机远程进行。如果您计划参加春夏季考试,请准备早在 2024 年 5 月 1 日就参加考试。具体日期将在考试开始前两个月公布。有关在线技术考试的重要信息将发布在 BC 工程师和地球科学家的在线学术考试状态页面上。此页面包括考生指南、考试时间表、考试形式和辅助工具列表。您应该会收到参加 2023 年 12 月春夏季考试的邀请。如果您有资格参加这次考试,您需要在 2024 年 2 月的第一周之前注册。如果您在 2024 年 1 月的第一周之前没有收到电子邮件邀请,请告知 exams@peo.on.ca。注意:PEO 不负责邮件投递。如果您计划在 2024 年春季/夏季考试中参加的考试未在下方列出,请在 2023 年 8 月 4 日之前发送电子邮件至 exams@peo.on.ca,以确保本次考试可以参加。 (最后更新于 2023 年 6 月 22 日) 04-BS-1,数学 04-BS-2,概率与统计 04-BS-3,静力学与动力学 04-BS-4,电路与电源 04-BS-5,高等数学 04-BS-6,材料力学 04-BS-7,流体力学 04-BS-8,数字逻辑电路 04-BS-9,基础电磁学 04-BS-10,热力学 04-BS-11,材料特性 04-BS-12,有机化学 04-BS-13,生物学 04-BS-14,地质学

自动架:用于在量子计算中实现有效的表面代码通信的框架

量子计算机可以使用最强大的古典计算机解决难以纠缠的问题。但是,Qubits是善变的,容易出错。有必要在执行量子电路中积极纠正错误。量子误差校正(QEC)代码是为了启用易于故障的量子计算的。使用QEC,将一个逻辑电路转换为编码电路。大多数关于量子电路汇编的研究都集中在具有10-100吨且不容忍断层的NISQ设备上。在本文中,我们专注于易于故障量子硬件的汇编。特别是,我们专注于优化基于表面代码QEC的通信并行性。表面代码电路的执行涉及对大型纠缠物理量子晶格的非平凡的几何操纵。表面代码中的两个Qubit Gate在时空中以虚拟“管道”的形式实现,称为编织路径。应仔细路由编织路径以避免交通拥堵。Qubits之间的通信被认为是主要的瓶颈,因为它涉及调度和寻找量子位之间的同时路径。我们提供了有效安排编织路径的框架。我们发现,对于具有局部并行性模式的量子程序,我们的框架是一个最佳解决方案,而以前的基于贪婪的 - 基于贪婪的解决方案则不能。此外,我们建议扩展到局部并行分析框架,以解决通信框架。我们的框架在解决了通信瓶颈后取得了数量级的改善。

非常规计算,包括量子计算

II计算物理学29和能量障碍。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 29 B计算热力学。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 35 B.1 von neuman-contry Principple。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 35 B.2机械和热模式。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 43 C可逆计算。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 47 c.1可逆计算与解决方案一样。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 47 C.2保守计算的基础。 div> 。 div> 。 div>II计算物理学29和能量障碍。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>29 B计算热力学。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>35 B.1 von neuman-contry Principple。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>35 B.2机械和热模式。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 43 C可逆计算。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 47 c.1可逆计算与解决方案一样。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 。 div> 47 C.2保守计算的基础。 div> 。 div> 。 div>35 B.2机械和热模式。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>43 C可逆计算。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>47 c.1可逆计算与解决方案一样。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>。 div>47 C.2保守计算的基础。 div>。 div>。 div>。。。。。51 C.3保守的逻辑电路。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 54 C.4普遍性。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 55 C.5常数和垃圾。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 56 C.6无垃圾保守逻辑。 。 。 。 。 。 。 。 。 。 。 。 。 。 57 C.7弹道计算。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 60 d练习。 。 。 。 。 。 。 。 。 。 。 。 。51 C.3保守的逻辑电路。。。。。。。。。。。。。。。。54 C.4普遍性。。。。。。。。。。。。。。。。。。。。。。。。55 C.5常数和垃圾。。。。。。。。。。。。。。。。。。56 C.6无垃圾保守逻辑。。。。。。。。。。。。。。57 C.7弹道计算。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 60 d练习。 。 。 。 。 。 。 。 。 。 。 。 。57 C.7弹道计算。。。。。。。。。。。。。。。。。。。60 d练习。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。65

微电子和超大规模集成电路设计

CO4:识别同步设计中的问题并加以解决。讲座:使用 HDL 进行数字设计方法的介绍 - 设计流程 - 建模抽象级别、门级模型、RTL 模型、行为模型 - 仿真和综合 - ASIC/FPGA 建模 - 语言概念 - 数据类型和运算符 - 结构、数据流和行为模型 - 层次结构 - 组合和顺序电路描述 - 连续和程序分配 - 阻塞和非阻塞分配 - 任务和功能 - 接口 - 延迟建模 - 参数化可重用设计 - 系统任务 - 编译器指令 - 测试平台。数据路径和控制器 - 复杂状态机设计 - 建模 FSM - 状态编码 - 建模内存 - 基本流水线概念 - 流水线建模 - 时钟域交叉 - 算术函数建模 - 同步设计的障碍:时钟偏差、门控时钟、异步输入、同步器故障和亚稳态 - 同步器设计 - 同步高速数据传输 - 时序分析。综合简介 - 逻辑综合 - RTL 综合 - 高级综合、组合逻辑综合、优先级结构、带锁存器和触发器的时序逻辑 - 无意锁存器 - 状态机综合 - 寄存器和计数器 - 时钟 - 循环 - 代码优化 - 设计示例 - 可编程 LSI 技术 - PLA/PAL/PLD - CPLD 和 FPGA - Xilinx/Altera 系列 FPGA - 可编程片上系统 - Zynq SoC 设计概述。实践课程:HDL 模拟器简介、设计和测试平台代码、使用波形查看器进行回溯和调试 – 使用结构、数据流和行为模型对组合/时序逻辑电路进行建模 – 以不同风格对有限状态机进行建模 – FPGA 的综合和后端流程 – 在可重构设备上实现数字电路/系统 – 使用 ILA 进行调试 – 创建自定义 IP 并重复使用。

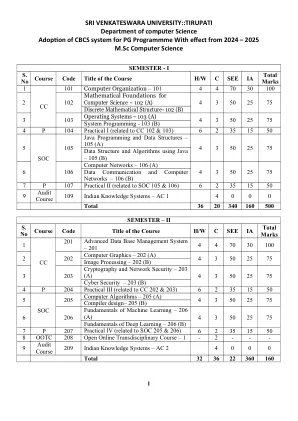

Tirupati计算机科学系的采用...

逻辑电路:逻辑函数 - 逻辑函数的合成 - 逻辑的最小化 - 与NAND合成的最小化和逻辑门的NOR门实现 - flip- flops - dogisters and Shift寄存器 - 寄存器 - 计数器 - 解码器 - 多路复用器 - 多路复用器 - PLDS - PLDS - 顺序电路。计算机的基本结构:功能单元 - 基本操作概念 - 总线结构 - 性能 - 多处理器和多计算机:功能单元 - 基本操作概念 - 总线结构 - 性能 - 绩效 - 历史观点。单元II机器指令和程序:数字,算术操作和字符 - 内存位置和地址,操作 - 指令和指令,排序 - 地址模式。单元III输入/输出组织:访问I/O设备 - 中断 - 直接内存访问 - 总线240接口电路 - 标准I/O接口。单元IV内存系统,概念 - 半导体RAM存储器 - 仅阅读记忆 - 缓存记忆 - 性能考虑 - 虚拟记忆管理要求 - 辅助算术算术:符号成员的添加和减法 - 快速加盖设计 - 快速加盖的设计 - 积极成员的乘法 - 乘法成员 - 快速乘法 - 快速乘法 - 快速乘法 - Integer Division Division -floing Point -Point -Point Point -Point Point -Point -Point -Point Point Point -Point -Point -Point -Point Point -Point -Pointing点数和浮动点数。单元V基本处理单元:概念 - 完整指令的执行 - 多重 - 总线组织 - 硬件控制 - 微型编程控制。管道:概念 - 数据危害 - 指令危害 - 对指导集的影响 - 数据路径和控制构建体 - 超级操作 - 超级SPARC II - 性能考虑。教科书: