XiaoMi-AI文件搜索系统

World File Search System数字电路与逻辑设计 - LPU 远程教育

十六进制数系统在计算机中用作中间系统,例如内存地址的表示或颜色的表示。十六进制数系统也称为 16 进制数系统,因为数字中的每个位置都代表一个以 16 为基数的增量数(见表 1.1)。例如,第一个位置(最右边)表示为 16,第二个位置(最右边)表示为 16,依此类推。要确定“十进制”表示中的实际数字,请取该位置出现的数字,然后将其乘以 16x,其中 x 是幂表示。例如,如果数字出现在最右边的位置,则取最右边位置的数字并将其乘以 16。如果数字中有多个位置(例如:17AF),则将所有结果相加。

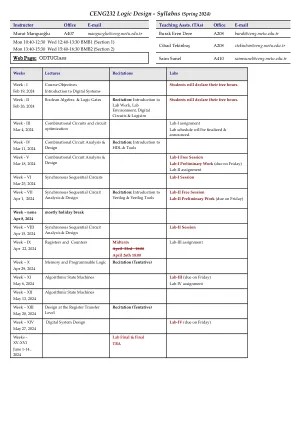

ceng232逻辑设计 - 教学大纲(春季2024)

因残疾而遇到困难并希望获得学术调整和/或辅助艾滋病的学生必须与ODTU残疾人支持办公室和/或课程讲师以及学术部门的残疾学生顾问(对于列表:http://engelsiz.metu.metu.edu.edu.tr/en/Advisor-Students-Disents-Disabitials)。有关详细信息,请访问残疾人支持办公室的网站:https://engelsiz.metu.edu.dr/en/

拓扑量子计算中的三元逻辑设计

量子计算机的运行速度比传统计算机快得多。它基于叠加原理工作。但由于退相干效应,量子态的叠加会因与环境的相互作用而遭到破坏。完全隔离一个量子系统以使其摆脱退相干是一个真正的挑战。这个问题可以通过使用物质的拓扑量子相来规避。这些相具有称为任意子的准粒子激发。任意子是电荷通量复合材料,表现出奇异的分数统计特性。当交换顺序很重要时,任意子被称为非阿贝尔任意子。拓扑超导体中的马约拉纳费米子和某些量子霍尔态中的准粒子是非阿贝尔任意子。这种物质的拓扑相具有基态简并性。两个或多个非阿贝尔任意子的融合可以导致多个任意子的叠加。拓扑量子门是通过非阿贝尔任意子的编织和融合来实现的。容错是通过任意子的拓扑自由度来实现的。这种自由度是非局部的,因此无法受到局部扰动的影响。本文讨论了拓扑量子比特的希尔伯特空间。简要给出了二元门的 Ising 和斐波那契任意子模型。三元逻辑门比二元逻辑门更紧凑,自然出现在一种称为元任意子的任意子模型中。元任意子的融合和编织矩阵的数学模型是重耦合理论的量子变形。我们提出,现有的量子三元算术门可以通过元任意子的编织和拓扑电荷测量来实现。

LNG 船舶可再生能源混合发电状态转换逻辑设计

摘要:就能源生产和消耗而言,船舶是独立且孤立的电力系统,其能源需求与电力需求的类型和种类以及船舶类型(客船或商船)有关。船舶上的电力供应传统上基于发动机热发电机,其使用化石燃料、柴油或天然气。由于船舶热发电机的持续运行,最终会增加对环境的污染气体排放,主要是二氧化碳。可再生能源 (RES) 与传统船舶热机的结合可以减少二氧化碳排放,从而实现船舶与环境之间的“更绿色”互动。由于船舶运行的电力需求各不相同,考虑到长距离航行和入港期间负载需求的不同性质,必须评估 RES 的使用。本文提出了一种新的控制方法,以平衡 LNG 船舶负载需求和 RES 发电,该方法基于实际条件下的精确模型和解决方案。能源管理系统 (EMS) 是使用状态转换的逻辑设计在有限状态机结构中设计和实现的。结果证明,减少化石燃料的消耗是可行的,而且如果与可再生能源相结合,可以减少二氧化碳的排放。

人工智能学士 数据科学硕士 网络安全硕士

第一年 第一学期 计算机科学概论实验室:计算机科学概论 编程基础实验室:编程基础 伊斯兰研究/伦理学 巴基斯坦研究 微积分和解析几何 英语写作与理解 第二学期 面向对象编程技术实验室:面向对象编程技术 数字逻辑设计实验室:数字逻辑设计 线性代数 概率与统计 沟通与表达技巧 第二年 第三学期 数据结构与算法实验室:数据结构与算法 计算机组织与汇编语言实验室:计算机组织与汇编语言 离散数学结构 人工智能实验室:人工智能微分方程 第 4 学期 计算机网络与数据通信实验室:计算机网络与数据通信 数据库系统

第三学期课程信息

2-3 1.4 数字系统 4 5 4-5 1.5 逻辑门 3 8 6-7 2.2 布尔方程 4 12 8-9 2.3 布尔代数 4 16 10 2.4 从逻辑到门 2 18 第 2 单元:组合逻辑设计: 11 2.1 简介 1 19 12 2.5 多级组合逻辑 2 21 13 2.6 X 和 Z 2 23 14-15 2.7 卡诺图 3 26 16 2.8 组合构建块 2 28 17 2.9 时序 2 30 18 4.1 HDL:简介 2 32 19-20 4.2 组合逻辑 2 34 21 4.3结构建模 3 37 22 4.7.1 数据类型 2 39 第 3 单元:时序逻辑设计: 23 3.1 简介 2 41 24-26 3.2 锁存器和触发器 5 46 27-28 3.3 同步逻辑设计 3 49 29-30 3.4 有限状态机 4 53 31-33 3.5 时序逻辑的时序 5 58 34 3.6 并行性 2 60 第 4 单元:硬件描述语言 2: 35-37 4.4 时序逻辑 5 65 38-40 4.5 更多组合逻辑 5 70 41-42 4.6 有限状态机 4 74 43-44 4.8 参数化模块 4 78 45-46 4.9 测试台 4 82 第 5 单元:数字构建模块:

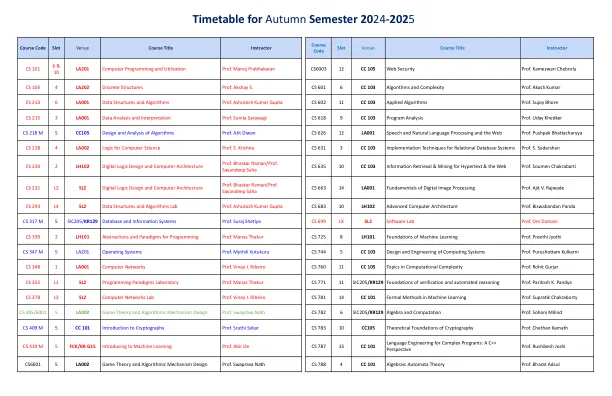

秋季学期2024-2025的时间表-CSE IITB

CS 230 2 LH102数字逻辑设计和计算机架构Bhaskar Raman/Prof.Sayandeep Saha CS 635 10 CC 103超文本的信息检索和采矿和网络教授Soumen Chakrabarti

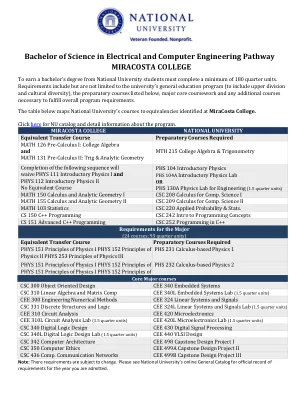

电气和计算机工程途径的理学学士

Core Major courses CSC 300 Object Oriented Design CEE 340 Embedded Systems CSC 310 Linear Algebra and Matrix Comp CEE 340L Embedded Systems Lab (1.5 quarter units) CEE 300 Engineering Numerical Methods CEE 324 Linear Systems and Signals CSC 331 Discrete Structures and Logic CEE 324L Linear Systems and Signals Lab (1.5 quarter units) CEE 310电路分析CEE 420 Microectronics CEE 310L电路分析实验室(1.5季度单位)CEE 420L Microectronics Lab(1.5季度单位)CSC 340数字逻辑设计CEE 430数字信号处理CSC 340L数字逻辑设计实验室(1.5季度) CEE 499A顶峰设计项目II CSC 436 Comp。通信网络CEE 499B顶峰设计项目III

EE 370A 数字电子学 2021-22-I

和稳健性、功率和能量、速度。隔离反相器:不同的反相器实现、MOSFET 作为开关、CMOS 反相器、CMOS 反相器的静态和动态行为、性能指标、设计视角:反相器链分析和缩放影响。组合电路:涉及静态 CMOS 设计、比率逻辑设计、传输晶体管设计和动态逻辑设计的设计指南和权衡。顺序电路设计:静态时序分析 (STA),双稳态电路:静态和动态锁存器和寄存器、流水线和非双稳态顺序电路。基于阵列的逻辑设计:现场可编程门阵列 (FPGA)。CMOS 存储器设计:存储器层次结构和组织、外围电路、静态随机存取存储器 (SRAM) 设计、动态 RAM (DRAM) 设计。向上移动层次结构:系统级设计、数据路径和寄存器传输操作。硬件描述语言 (HDL) 简介。寄存器传输级 (RTL) 到 GDSII 流程(行业专家讲座)。