XiaoMi-AI文件搜索系统

World File Search System完全集成的 384 元件、16 块、W 波段相位...

摘要 — 本文介绍了一种可扩展 W 波段相控阵系统的设计和实现,该系统具有内置自对准和自测试功能,基于采用 TowerJazz 0.18 µ m SiGe BiCMOS 技术制造的 RFIC 收发器芯片组,其 f T / f MAX 为 240/270 GHz。该 RFIC 集成了 24 个移相器元件(16TX/8RX 或 8TX/16RX)以及直接上变频器和下变频器、带素数比倍频器的锁相环、模拟基带、波束查找存储器和用于性能监控的诊断电路。设计了两个带有集成天线子阵列的有机印刷电路板 (PCB) 插入器,并将其与 RFIC 芯片组共同组装,以产生可扩展的相控阵瓦片。瓦片通过菊花链式本振 (LO) 同步信号彼此相位对齐。本文介绍了 LO 错位对波束方向图的影响的统计分析。16 个瓦片组合到载体 PCB 上,形成一个 384 元件 (256TX/128RX) 相控阵系统。在 256 个发射元件的视轴处测量到的最大饱和有效全向辐射功率 (EIRP) 为 60 dBm (1 kW)。在 90.7 GHz 下运行的无线链路使用 16-QAM 星座,在降低的 EIRP 为 52 dBm 的情况下,产生的数据速率超过 10 Gb/s,等效链路距离超过 250 m。

具有 110 fs 抖动的 56 GHz 小数 N PLL

I. 引言随着通信系统追求更高的性能,低抖动时钟生成问题变得更具挑战性。例如,以 112 Gb/s 或 224 Gb/s 运行的 PAM4 发射器可以结合 56 GHz 锁相环 (PLL) 进行多路复用。这样的应用对设计提出了三个条件。首先,对于 224 Gb/s 的数据速率,PLL 抖动必须远低于符号周期,例如约 100 fs。其次,PLL 最好实现为小数 N 环路,以便以不同的晶体频率运行并可能纠正晶体误差。第三,多通道系统使得每通道使用低功耗、紧凑的 PLL 设计成为可取的,而不是在通道和长互连上分配 56 GHz 时钟。在此频率范围内,先前的小数 N 分频设计已实现 200 至 500 fs 的均方根抖动,同时功耗为 31 至 46 mW,所需芯片面积为 0.38 至 0.55 mm2 [1], [2], [3]。本文提出了一种小数 N 分频 PLL 架构和多种电路技术,可实现 110 fs 的均方根抖动和 23 mW 的功耗。实验原型采用 28 纳米 CMOS 技术制造,占用有效面积为 0.1 mm2。第二部分介绍了这项工作的背景。第三部分介绍了所提出的有限脉冲响应 (FIR) 滤波器和

NREL Flatirons 园区的光伏电站和电池储能系统集成

缩略词列表 AGC 自动发电控制 ARIES 综合能源系统高级研究 BESS 电池储能系统 BMS 电池管理系统 CAISO 加州独立系统运营商 CGI 可控电网接口 DAS 数据采集系统 DOE 美国能源部 EMS 能源管理系统 ERCOT 德克萨斯州电力可靠性委员会 FFR 快速频率响应 GHI 全球水平辐照度 GPS 全球定位系统 IBR 基于逆变器的资源 IEEE 电气电子工程师协会 IESS 大规模综合能源系统 IR 红外线 Li-ion 锂离子 MPP 最大功率点 MPPE 最大功率点估计 MPPT 最大功率点跟踪 NERC 北美电力可靠性公司 NREL 国家可再生能源实验室 NWTC 国家风能技术中心 PCC 公共耦合点 PCC 公共耦合点 PFR 一次频率响应 PHIL 功率硬件在环 PLL 锁相环 PMU 相量测量单元 POD 功率振荡阻尼 POI 互连点 PPC 发电厂控制器 PREPA 波多黎各电力局 PSS 电力系统稳定器 PV光伏 ROCOF 频率变化率 RPS 可再生能源组合标准 RTAC 实时自动化控制器 RTDS 实时数字模拟器 SCADA 监控和数据采集 SDS 安全数据表 SETO 太阳能技术办公室 SF 同步框架 SOC 充电状态

对同相听觉的实时算法进行基准测试...

摘要 — 在非快速眼动 (NREM) 睡眠期间对脑电图慢波 (SW) 进行听觉刺激,当其在 SW 的上行阶段进行时,已被证明可以改善认知功能。对于 SW 幅度较低的受试者,如老年人或患有帕金森病 (PD) 等神经退行性疾病的患者,SW 增强尤其可取。然而,现有的估计上行阶段的算法在低脑电图幅度和 SW 频率不恒定时存在相位精度较差的问题。我们介绍了两种用于在自主可穿戴设备上实时估计脑电图相位的新算法。这些算法基于锁相环 (PLL) 和首次基于相位声码器 (PV)。我们将这些相位跟踪算法与简单的幅度阈值方法进行了比较。优化后的算法在相位精度、估计 SW 幅度在 20 到 60 µV 之间以及 SW 频率高于 1 Hz 的相位的能力方面进行了基准测试,这些记录来自健康的老年人和 PD 患者。此外,这些算法在可穿戴设备上实现,并在模拟睡眠脑电图以及对 PD 患者的前瞻性记录过程中评估了计算效率和性能。所有三种算法都在 SW 上行阶段提供了 70% 以上的刺激触发。PV 在瞄准低幅度 SW 和频率高于 1 Hz 的 SW 时表现出最高能力。实时硬件测试表明,PV 和 PLL 对微控制器负载的影响都很小,而 PV 的效率比 PLL 低 4%。主动听觉刺激不会影响相位跟踪。这项工作表明,在低幅度 SW 人群中,也可以在家庭睡眠干预期间使用可穿戴设备提供相位精确的听觉刺激。

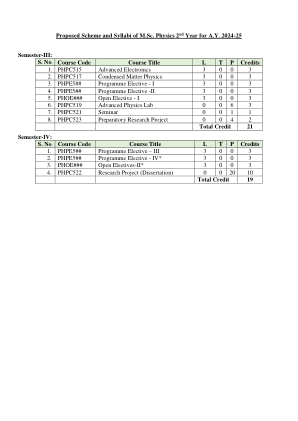

理学硕士物理学第二年拟议的方案和教学大纲...

高级电子学学分 3-0-0:3 课程教育目标: COE1 让学生熟悉先进的电子设备及其应用。 COE2 培养对数字电路设计和使用微控制器连接简单系统的理解。 COE3 培养对通信系统的理解。 UNIT-1 9 L 半导体器件:载流子的漂移和扩散、电荷的产生和复合、直接和间接半导体。PN 结、二极管方程、PN 结的势垒宽度和电容、变容二极管、开关二极管、作为开关和放大器的 FET、光电器件:LED、二极管激光器、光电探测器和太阳能电池。 UNIT-2 9 L 先进电子设备:金属氧化物场效应晶体管 (MOSFET)、MOSFET 中的短沟道效应、鳍式场效应晶体管 (FinFET)、铁电场效应器件和 2D 纳米片器件;新兴存储设备:DRAM、ReRAM、FeRAM 和相变存储器 (PCM) 以及通用存储设备。UNIT-3 10 L 模拟系统:锁相环及其应用频率倍增;模拟乘法器及其应用;对数和反对数放大器;仪表放大器;传感器:温度、磁场、位移、光强度和力传感器组合电路设计:编程逻辑器件和门阵列、7 段和 LCD 显示系统、数字增益控制、模拟多路复用器、基于 PC 的测量系统;序贯电路设计:不同类型的 A/D 和 D/A 转换技术、TTL、ECL、MOS 和 CMOS 操作和规格。 UNIT-4 9 L 通信系统:通信系统的概念、电磁频谱的作用、通信系统术语的基本概念、调制的必要性、幅度、频率、脉冲幅度、脉冲位置、脉冲编码调制、通信系统中的信息、编码、脉冲调制的类型、脉冲宽度调制 (PWM)、脉冲位置调制 (PPM)、脉冲编码调制 (PCM) 的原理;数字通信简介。参考书:

不同二进制计数器的性能调查...

I. 引言 在许多 VLSI 系统中,二进制计数器是基本构建块。𝑛 位二进制计数器由一系列 𝑛 触发器组成,其计数值可以是 0 到(2 n −1)[1]。在为各种应用设计高速、低功耗数字系统时,低功耗快速二进制计数器设计是关注的基本点。调度中进程分配的计数时间可用作时钟分频器(用于片上处理器,因为有时处理器的工作频率低于处理器的实际频率)。二进制计数器广泛用于单斜率或双斜率模数转换器 (ADC)。在这种情况下,在每个时钟脉冲上递增的同步计数器对应于上升和下降斜坡发生器采样的模拟信号,其值进一步输入数模转换器 (DAC) 以创建其模拟值 [2-5]。在数字锁相环 (DPLL) 中,时间数字转换器 (TDC) 用作相位检测器,其中 TDC 由加减计数器组成。它用于捕获分数压控振荡器 (VCO) 的信息,以提高频率检测的准确性 [6-13]。计数器模块用于设计电子产品代码 (EPC) Gen-2 标准中 LFSR 的变量,用于各种安全问题中的超高频或射频识别 [14]。高速二进制计数器用于计数光子计数相机中的光子数 [15]。在现代自动化技术中,某些事件非常快,无法在程序周期中检测到。为了检测这种高速事件,引入了一个新的技术术语,即高速计数器 (HSC)。在每转只有一个或几个脉冲的情况下,HSC 在确定旋转运动速度时非常有用。这种 HSC 的一部分适用于自动化、过程控制、

模拟和混合信号 VLSI 的 SAF 分析...

1 助理教授,Nirma 大学理工学院,艾哈迈达巴德 2 IEEE 高级会员,教授,Nirma 大学理工学院,艾哈迈达巴德 摘要 数模转换器是广泛使用的混合信号电路。由于电路范围广泛且没有合适的故障模型,模拟和混合信号的测试面临许多挑战。本文使用晶体管级的 SAF(stuck_at_Fault)、Stuck_open 和 stuck_short 故障模型。此外,这些故障模型用于分析对 3 位 R-2R DAC 特性参数的影响。 关键词 Stuck_open,Stuck_short,测试,DAC,故障。 1. 引言 如今,片上系统(SoC)包含模拟和混合信号(AMS)电路。有各种各样的 AMS 电路可供选择。在过去的几十年里,数字 IC 的测试得到了充分的探索。由模拟和混合信号组成的 SoC 给测试带来了很多挑战 [1]。 AMS 测试很大程度上依赖于电路。有限的可控性和可观察性增加了这些 AMS 电路的测试工作量。这些 AMS 电路的测试可能成为增加制造成本的限制因素 [2]。此外,由于对制造工艺步骤中的微小缺陷的敏感性以及高集成密度,AMS 电路的可靠性和性能可能会降低。模数转换器 (ADC)、数模转换器 (DAC) 和锁相环 (PLL) 是 AMS 电路的例子。DAC 是最广泛使用的混合信号集成电路之一,用作数字处理系统之间的接口。ADC 和 DAC 等数据转换器的测试是 AMS 电路测试中最具挑战性的问题。在传统的 DAC 测试中,需要比被测设备 (DUT) 更高精度的测量设备来表征 DUT 的性能。这使得测试仪的设计和制造真正具有挑战性,并带来了高昂的测试成本 [3]。

GR THz 004-V1.1.1

5 收发器构建模块建模 ................................................................................................................................ 20 5.1 信号路径组件 .............................................................................................................................................. 20 5.1.1 接收器噪声系数和非线性 ...................................................................................................................... 20 5.1.1.1 高级建模 ...................................................................................................................................... 20 5.1.1.2 THz 频段接收器非线性模型 ...................................................................................................... 21 5.1.1.3 三阶截点 IIP3dBm 和 SNDR ............................................................................................. 22 5.1.2 发射器输出功率 ................................................................................................................................ 22 5.1.2.1 输出功率的作用 ................................................................................................................................ 22 5.1.2.2 功率放大器输出功率和效率 ............................................................................................................. 23 5.1.3 功率放大器非线性建模................................................................................................... 24 5.2 时钟组件 ...................................................................................................................................... 25 5.2.1 锁相环和倍频器的相位噪声分布 ................................................................................................ 25 5.2.2 时间域相位噪声样本的生成 ............................................................................................................. 28 5.2.2.1 离散时间相位噪声模型 ............................................................................................................. 28 5.2.2.2 相位噪声功率谱密度采样 ............................................................................................................. 29 5.2.2.3 离散 PSD 缩放 ............................................................................................................................. 30 5.2.2.4 相位噪声样本生成 ............................................................................................................................. 30 5.2.2.4.1 随机性包含 ............................................................................................................................. 30 5.2.2.4.2 相位样本生成 ............................................................................................................................. 30 5.2.2.4.3 相位噪声样本生成................................................................................................................ 30 5.2.2.5 单次长生成................................................................................................................................................ 30 5.2.2.6 建议............................................................................................................................................... 31 5.3 数据转换器和基带滤波器........................................................................................................................ 31 5.3.0 简介....................................................................................................................................................... 31 5.3.1 数据转换器....................................................................................................................................... 31 5.3.1.0 简介................................................................................................................................................. 31 5.3.1.1 数据转换器性能指标.................................................................................................................... 32 5.3.1.2 性能趋势.................................................................................................................................... 42 5.4 光束斜视.................................................................................................................................................... 43 5.4.1 THz 波段的光束斜视效应............................................................................................................. 43 5.4.2 光束斜视的理论分析................................................................................................... 44 5.4.3 波束斜视处理 ................................................................................................................................ 48 5.5 射频损伤对 THz 链路的影响 ................................................................................................................ 5031 5.3.1.1 数据转换器性能指标 ...................................................................................................................... 32 5.3.1.2 性能趋势 ...................................................................................................................................... 42 5.4 光束斜视 ......................................................................................................................................................... 43 5.4.1 THz 频段的光束斜视效应 ......................................................................................................................... 43 5.4.2 光束斜视的理论分析 ............................................................................................................................. 44 5.4.3 光束斜视处理 ...................................................................................................................................... 48 5.5 RF 损伤对 THz 链路的影响 ............................................................................................................................. 5031 5.3.1.1 数据转换器性能指标 ...................................................................................................................... 32 5.3.1.2 性能趋势 ...................................................................................................................................... 42 5.4 光束斜视 ......................................................................................................................................................... 43 5.4.1 THz 频段的光束斜视效应 ......................................................................................................................... 43 5.4.2 光束斜视的理论分析 ............................................................................................................................. 44 5.4.3 光束斜视处理 ...................................................................................................................................... 48 5.5 RF 损伤对 THz 链路的影响 ............................................................................................................................. 50

4Gb/s CMOS 全差分模拟双延迟器

4Gb/s CMOS 全差分模拟双延迟锁定环时钟/数据恢复电路 Zhiwei Mao 和 Ted H. Szymanski 光网络研究组,ECE 系麦克马斯特大学,安大略省汉密尔顿,加拿大 L8S 4K1 摘要 提出了一种 4Gb/s 功率和面积高效的时钟/数据恢复 (CDR) 电路。采用全差分设计来抑制任何共模噪声并显著降低电源/地弹。模拟双延迟锁定环 (DLL) 架构将时钟采样边沿持续对齐到输入数据眼图张开的中心。自校正功能可避免传统 DLL 的相位捕获范围限制。原型电路采用 0.18um CMOS 技术实现。 CDR 采用 0.18µm CMOS 技术,占用 200 x 320 2 um 的小面积,在 2V 电源下功耗仅为 27mW。1. 简介随着 VLSI 系统的速度性能迅速提高,近年来小型低功耗高速 I/O 接口得到了广泛的研究。延迟锁定环 (DLL) 和锁相环 (PLL) 均可用于 CDR 电路以消除时钟/数据偏差并改善整体系统时序。在有参考时钟的情况下,通常使用 DLL,因为与 PLL 相比,DLL 不会累积相位误差。此外,DLL 通常具有更简单的设计并且本质上很稳定。传统 DLL 的缺点是其有限的相位捕获范围和输入时钟抖动传播。此外,数字 DLL [1] 不可避免地存在量化误差,并且通常需要更大的面积和功耗,而模拟 DLL 设计 [2] 被指责对噪声更敏感。本文提出了一种新型 CMOS CDR 电路,该电路采用全差分结构来降低对共模噪声的敏感性,并应用模拟双 DLL 来实现连续相位对齐和稳健的数据恢复。CDR 核心电路在 4Gb/s 的数据速率下消耗面积小、功耗低。本文安排如下:第 2 节介绍 CDR 架构,第 3 节讨论在 0.18um CMOS 技术中原型实现该架构的电路设计问题,第 4 节展示原型芯片实现和仿真结果,第 5 节总结本文。

新闻稿

新产品为空间射频工程和设计界提供了非密封的现成的整数 N 合成器,适用于具有挑战性的高可靠性空间应用。加利福尼亚州米尔皮塔斯 – 2023 年 5 月 4 日 – 领先的高可靠性半导体解决方案提供商 Teledyne e2v HiRel 自豪地宣布推出一种新的空间 COTS(商用现货)锁相环 (PLL),旨在在空间应用中提供卓越的性能和可靠性。TDPL97240 采用小型 7x7 毫米非密封环氧密封陶瓷四方无引线 (QFN) 扁平封装,与标准航天级陶瓷部件相比,电路板尺寸缩小了 75%。它可耐受 100 krad (Si) 总电离剂量 (TID) 的辐射,并基于蓝宝石上硅 (SOS) 技术构建。这使得 PLL 具有天然的抗辐射能力,并且不受单粒子闩锁 (SEL) 效应的影响。它还具有 50 MHz-5 GHz 的锁定频率范围、双模预分频器 (5/6 和 10/11),可提供更大的频率灵活性以及串行接口或直接引脚编程能力。Teledyne e2v HiRel 营销和产品管理副总裁 Mont Taylor 表示:“我们很高兴为客户提供经济高效的解决方案,该解决方案可提供太空应用所需的高可靠性和高性能。我们的新型太空 COTS PLL 是同样需要抗辐射性能的 LEO 应用的理想解决方案。”该设备符合 NASA EEE-INST-002 规范,并经过严格的测试和验证,以确保满足必要的太空要求。太空 COTS 解决方案的经济高效性为以前可能无法负担更昂贵的传统合格解决方案的客户带来了新的机会。有关 Teledyne e2v HiRel 所有太空产品的更多信息,请在 Teledyne Defense Electronics 网站上查看我们的半导体、转换器和处理器产品组合以及相关服务。设备可从 Teledyne e2v HiRel 或授权分销商处订购和发货。它们从我们位于加利福尼亚州米尔皮塔斯的国防部信任工厂发货。