机构名称:

¥ 1.0

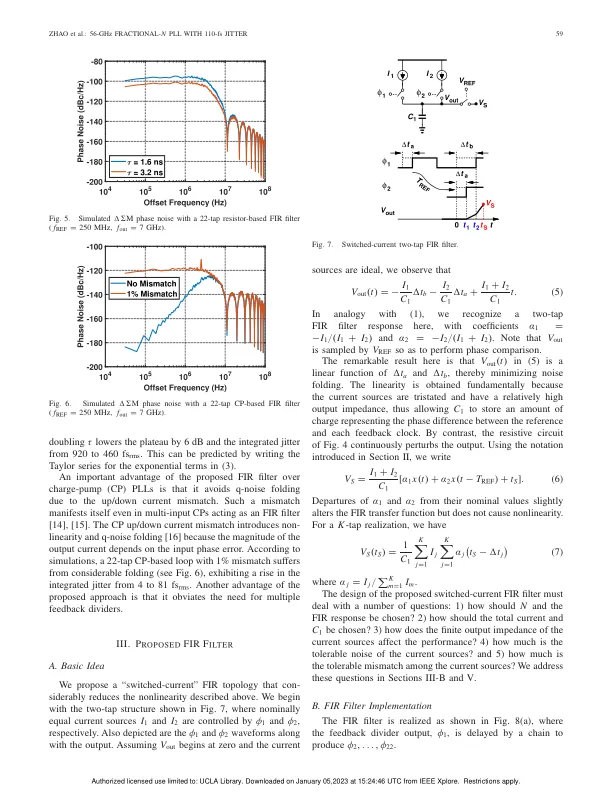

I. 引言随着通信系统追求更高的性能,低抖动时钟生成问题变得更具挑战性。例如,以 112 Gb/s 或 224 Gb/s 运行的 PAM4 发射器可以结合 56 GHz 锁相环 (PLL) 进行多路复用。这样的应用对设计提出了三个条件。首先,对于 224 Gb/s 的数据速率,PLL 抖动必须远低于符号周期,例如约 100 fs。其次,PLL 最好实现为小数 N 环路,以便以不同的晶体频率运行并可能纠正晶体误差。第三,多通道系统使得每通道使用低功耗、紧凑的 PLL 设计成为可取的,而不是在通道和长互连上分配 56 GHz 时钟。在此频率范围内,先前的小数 N 分频设计已实现 200 至 500 fs 的均方根抖动,同时功耗为 31 至 46 mW,所需芯片面积为 0.38 至 0.55 mm2 [1], [2], [3]。本文提出了一种小数 N 分频 PLL 架构和多种电路技术,可实现 110 fs 的均方根抖动和 23 mW 的功耗。实验原型采用 28 纳米 CMOS 技术制造,占用有效面积为 0.1 mm2。第二部分介绍了这项工作的背景。第三部分介绍了所提出的有限脉冲响应 (FIR) 滤波器和

具有 110 fs 抖动的 56 GHz 小数 N PLL

主要关键词