机构名称:

¥ 1.0

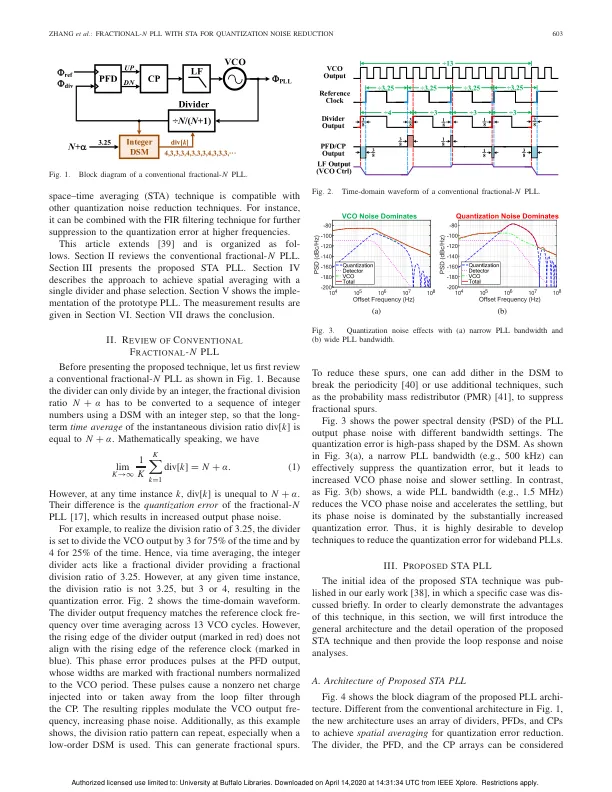

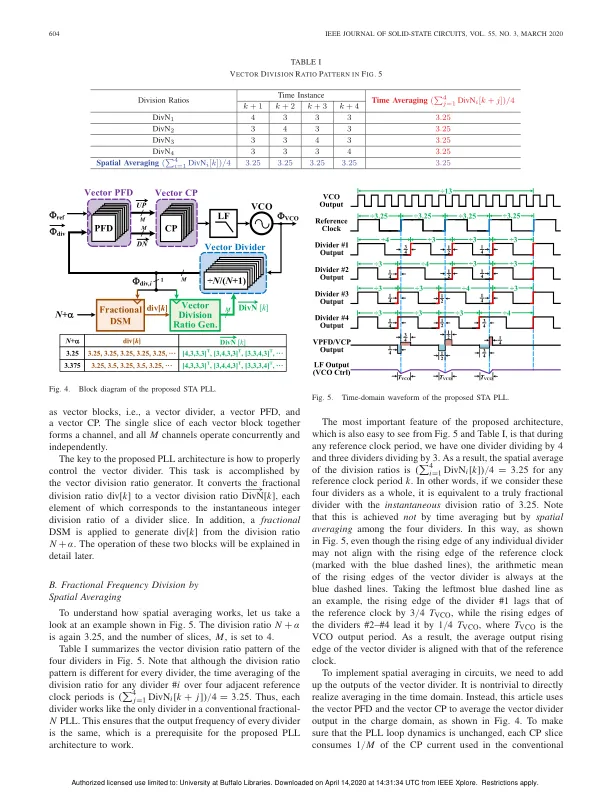

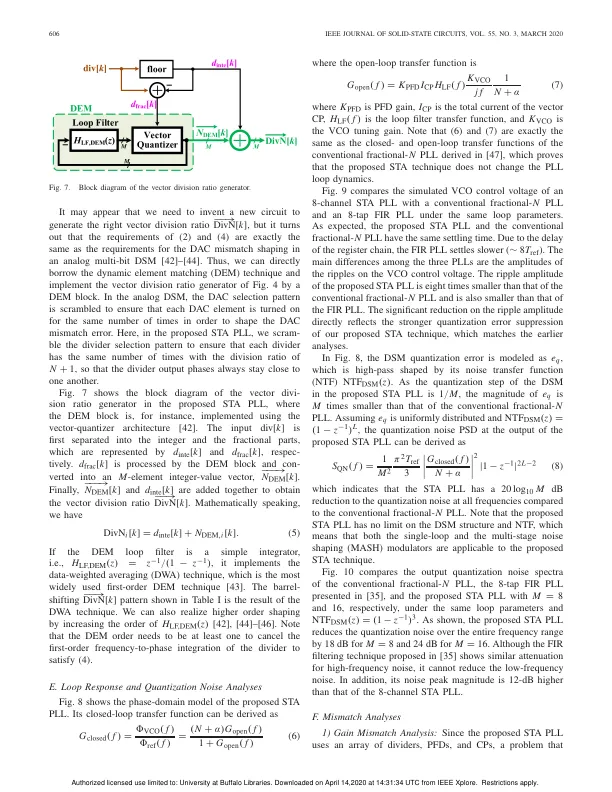

摘要 — 本文介绍了一种空间时间平均技术,该技术可实现瞬时小数分频,从而显著降低小数 N 锁相环 (PLL) 中的量化误差。空间平均可通过使用并行运行的分频器阵列来实现。它们的不同分频比由小数调制器 (DSM) 和动态元件匹配 (DEM) 块产生。为了降低分频器功率,本文还提出了一种仅使用一个分频器和相位选择来实现空间平均的方法。原型 2.4 GHz 小数 N PLL 采用 40 nm CMOS 工艺实现。测量结果表明,所提出的技术分别在 1 MHz 和 10 MHz 偏移处将相位噪声降低了 10 dB 和 21 dB,从而使积分均方根抖动从 9.55 ps 降低至 2.26 ps。索引术语——调制器(DSM)、数据加权平均(DWA)、动态元件匹配(DEM)、小数N分频PLL、频率合成器、相位噪声、锁相环(PLL)、量化噪声降低。

具有空间时间平均功能的分数 N PLL,用于...

主要关键词