机构名称:

¥ 1.0

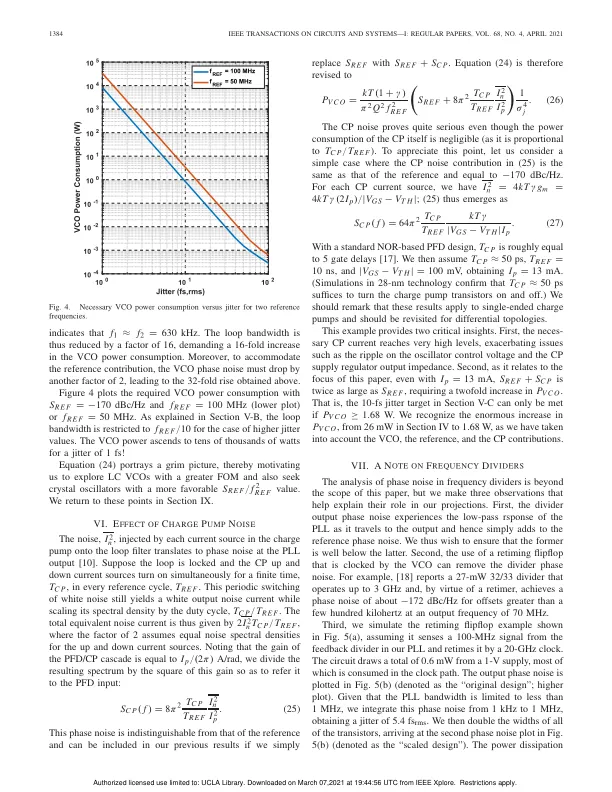

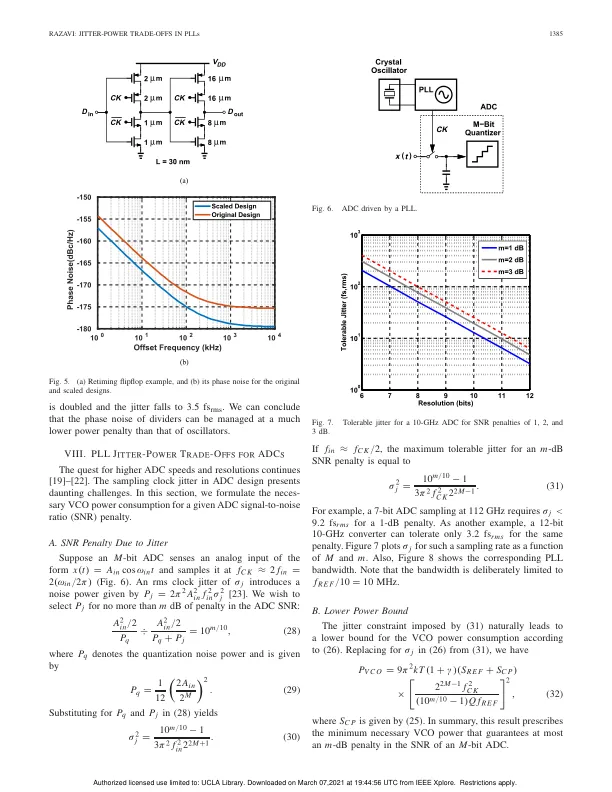

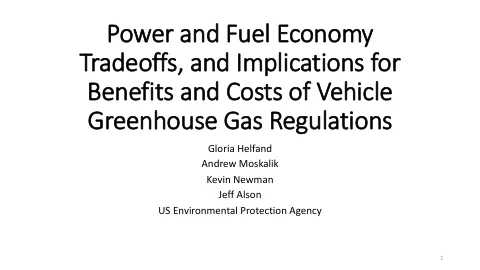

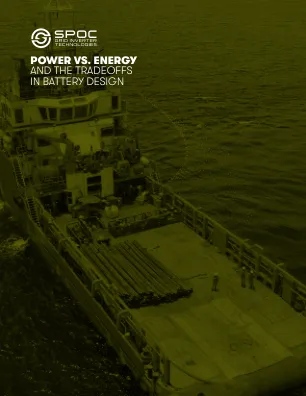

I. 引言 锁相环 (PLL) 抖动问题表现在各种系统中,特别是在通信和数据转换器中。近年来,有几种趋势导致了对低抖动的需求。首先,更高的数据速率使得链路中大多数阶段的时序预算收紧。其次,有线和无线媒体中可用的带宽有限,需要采用频谱高效的调制方案,这进一步限制了时钟和本地振荡器 (LO) 生成中可容忍的抖动。第三,随着模数转换器 (ADC) 以更高的速度和分辨率为目标,其采样时钟抖动必须相应下降。最先进的 PLL 设计已经在 5.5 GHz 至 16 GHz 频率下实现了 50 至 75 fs rms 范围内的抖动值 [1]–[6]。先前的研究 [7]–[10] 已经研究了 PLL 中的抖动现象。本文的目的是制定 PLL 抖动和功耗之间的权衡,并预测前者降低到 10 fs 以下时的设计问题。通过扩展 [11] 中的工作,我们得出了表明未来面临巨大挑战的趋势。第二节概述了当今理想的抖动值,第三节介绍了我们的分析框架。第四节讨论了振荡器相位噪声的影响,第五节还考虑了参考贡献。第六节涉及电荷泵 (CP) 噪声。第七节和第八节分别分析了抖动对 ADC 的影响以及可以减轻抖动功率权衡的因素。

PLL 中的抖动功率权衡

主要关键词