XiaoMi-AI文件搜索系统

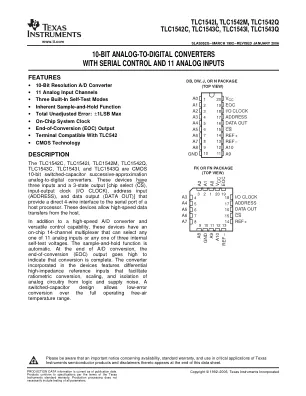

World File Search Systemtlc1543.pdf - 德州仪器

当芯片选择 (CS) 处于非活动状态(高电平)时,ADDRESS 和 I/O CLOCK 输入最初被禁用,DATA OUT 处于高阻抗状态。当串行接口将 CS 置于活动状态(低电平)时,转换序列从启用 I/O CLOCK 和 ADDRESS 以及将 DATA OUT 从高阻抗状态移除开始。然后,串行接口向 ADDRESS 提供 4 位通道地址,向 I/O CLOCK 提供 I/O CLOCK 序列。在此传输过程中,串行接口还从 DATA OUT 接收先前的转换结果。I/O CLOCK 从主机串行接口接收长度在 10 到 16 个时钟之间的输入序列。前四个 I/O 时钟将 4 位地址加载到地址寄存器的 ADDRESS 上,选择所需的模拟通道,接下来的六个时钟提供对模拟输入进行采样的控制时序。

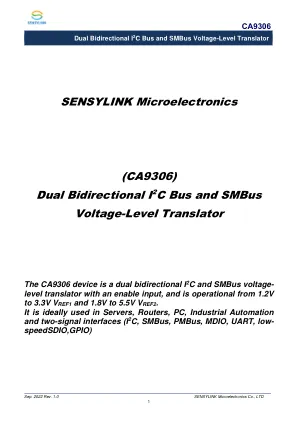

CA9306 双双向 I2C 总线和 SMBus 电压...

CA9306 器件是带有使能输入的双双向 I 2 C 和 SMBus 电压电平转换器,可在 1.2V 至 3.3VV REF1 和 1.8V 至 5.5VV REF2 的范围内工作。CA9306 器件允许在无需方向引脚的情况下在 1.2V 和 5V 之间进行双向电压转换。开关的低导通电阻 (RON) 允许以最小的传播延迟进行连接。当 EN 为高电平时,转换器开关处于导通状态,SCL1 和 SDA1 I/O 分别连接到 SCL2 和 SDA2 I/O,从而允许端口之间的双向数据流。当 EN 为低电平时,转换器开关处于关闭状态,端口之间存在高阻抗状态。CA9306 器件可用于将 400kHz 总线与 100kHz 总线隔离,方法是控制 EN 引脚在快速模式通信期间断开较慢的总线,并进行电压转换。可用封装:MSOP-8、DFN3x4-8、DFN2x3-8 封装。

LP-MSPM0L1117 Launchpad 开发套件

• 移除 J22 隔离块中的 3V3 跳线,并将电流表连接到此跳线上。 • 考虑反向通道 UART 和连接到 MSPM0L1117 的任何电路对电流消耗的影响。考虑在隔离跳线块处断开这些电路,或者至少考虑最终测量中的电流吸收和供应能力。 • 确保 MSPM0L1117 上没有浮动输入/输出 (I/O)。这会导致不必要的额外电流消耗。每个 I/O 都被驱动,或者如果 I/O 是输入,则被拉到或驱动到高电平或低电平。 • 开始目标执行。 • 为了获得最准确的电流测量结果,请将设备置于自由运行模式,并断开 MSPM0L1117 和电路板调试部分(接头 J22)之间的编程信号。 • 测量电流。请记住,如果电流水平波动,则很难获得稳定的测量结果。测量静态状态更容易。

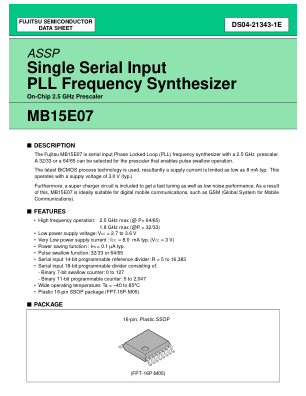

单串行输入 PLL 频率合成器 - SM0VPO

将 PS 引脚设置为低电平,IC 进入省电模式,因此电流消耗可限制为 10 µ A(最大值)。将 PS 引脚设置为高电平,则释放省电模式,IC 正常工作。此外,还包含间歇操作控制电路,有助于从省电模式平稳启动。一般来说,可以通过间歇操作(关闭或唤醒合成器)来节省功耗。在这种情况下,如果 PLL 不受控制地通电,则由于参考频率(fr)和比较频率(fp)之间未定义的相位关系,产生的相位比较器输出信号是不可预测的,并且在最坏的情况下可能需要更长的时间来锁定环路。为了防止这种情况,间歇操作控制电路在通电期间强制相位检测器输出有限的误差信号,从而保持环路锁定。在省电模式下,除省电功能必不可少的电路外,相应部分停止工作,然后电流消耗降至 10 µ A(最大值)。此时,Do 和 LD 变为与环路锁定时相同的状态。即,Do 变为高阻抗。VCO 控制电压自然保持在由 LPF 的时间常数定义的锁定电压。因此,VCO 的频率保持在锁定频率。

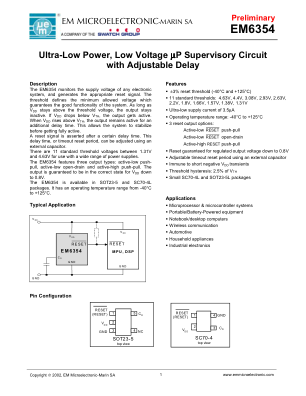

EM6354

描述 EM6354 监控任何电子系统的电源电压,并生成适当的复位信号。阈值定义了允许的最小电压,可保证系统正常运行。只要 V DD 保持在阈值电压以上,输出就保持非活动状态。如果 V DD 降至 V TH 以下,输出将变为活动状态。当 V DD 升至 V TH 以上时,输出将在一段额外的延迟时间内保持活动状态。这可使系统在完全活动之前稳定下来。在一定延迟时间后发出复位信号。可以使用外部电容器调整此延迟时间或超时复位时间。有 11 个标准阈值电压介于 1.31V 和 4.63V 之间,可与各种电源一起使用。EM6354 具有三种输出类型:低电平有效推挽、低电平有效开漏和高电平有效推挽。当 V DD 低至 0.8V 时,输出保证处于正确状态。 EM6354 采用 SOT23-5 和 SC70-4L 封装。其工作温度范围为 -40°C 至 +125°C。

TB321:HIP4080 和 HIP4081 高频 H 桥驱动器

HIP4080 没有像 HIP4081 那样的输入协议,除了通过 DIS 引脚外,该协议还可以使两个低功率 MOSFET 保持关闭状态。IN+ 和 IN- 是比较器的输入,比较器控制桥接,使得一次只有一个低功率器件处于打开状态(假设 DIS 为低)。但是,通过在芯片启用时控制下部开启延迟引脚 LDEL,可以保持两个下部 MOSFET 处于关闭状态,如图 2 所示。将 LDEL 拉至 V DD 将通过输入比较器无限期地延迟下部开启延迟,并使下部 MOSFET 保持关闭状态。在下部 MOSFET 关闭且芯片启用的情况下,即 DIS = 低,IN+ 或 IN- 可以在整个周期内切换,从而正确设置上部驱动器输出。完成此操作后,LDEL 将释放到其正常工作点。至关重要的是,当 LDEL 保持高电平时,IN+/IN- 必须切换一个完整的周期,以避免击穿。此启动过程可以通过图 2 中的电路的电源电压和/或芯片启用命令来启动。

ACPL-M43T-500E - Ciiva

注释:1. 百分比电流传输比定义为输出集电极电流 IO 与正向 LED 输入电流 IF 之比乘以 100。2. 器件被视为双端器件:引脚 1 和 3 短接在一起,引脚 4、5 和 6 短接在一起。3. 按照 UL 1577,每个光电耦合器都通过施加 4800 V RMS 的绝缘测试电压 1 秒进行验证测试。4. 逻辑高电平下的公共瞬态抗扰度是共模脉冲 V CM 上升沿上的最大可容忍(正)dV CM /dt,以确保输出将保持在逻辑高状态(即 VO > 2.0 V)。逻辑低电平下的共模瞬变抗扰度是共模脉冲信号 V CM 下降沿可容忍的最大(负)dV CM /dt,以确保输出保持在逻辑低状态(即 VO < 0.8 V)。5. 1.9 k 负载代表 1.6 mA 的 1 TTL 单位负载和 5.6 k 上拉电阻。6. 交流输出电压比其中频值低 3 dB 的频率。7. 建议使用连接引脚 4 和 6 之间的 0.1 μF 旁路电容。8. 对于任何给定设备,脉冲宽度失真 (PWD) 定义为 |t PHL - t PLH |。9. 在相同测试条件下,任何两个部件之间的 t PLH 和 t PHL 之间的差值。

ADN4650/ADN4651/ADN4652 (Rev. E) - ADI 公司

1 这些规格由设计和特性保证。2 占空比或脉冲偏差是器件任何通道的 t PLH 和 t PHL 之间最大差值的幅度,即 |t PHLx – t PHLx |。3 通道间或输出偏差是器件内 t PLHx 最大值与最小值之间的差值,或器件内 t PHLx 最大值与最小值之间的差值,以两者中较大者为准。4 部件间输出偏差是多个器件间 t PLHx 最大值与最小值之间的差值,或多个器件间 t PHLx 最大值与最小值之间的差值,以两者中较大者为准。5 抖动参数由设计和特性保证。值不包括刺激抖动。V ID = 400 mV p-p,t R = t F = 0.3 ns(20% 至 80%)。6 此规格是在约 7,000,000 个边缘上测量的。7 峰峰值抖动规格包括由于脉冲偏移 (t SK(D) ) 引起的抖动。8 此规格是在约 3,000,000 个边缘上测量的。9 使用公式 t TJ(PP) = 14 × t RJ(RMS) + t DJ(PP)。10 减去 250 fs rms 的输入相位抖动。11 减去 100 fs rms 的输入相位抖动。12 故障安全延迟是在 D OUTx± 切换为高电平以将空闲输入反映到 D INx± 之前的延迟(|V ID | < 100 mV,开路或短路/终止输入条件)。

ACPL-M43T-500E - Ciiva

注释:1.电流传输比(百分比)定义为输出集电极电流 I O 与正向 LED 输入电流 I F 之比乘以 100。2.设备被视为双端设备:引脚 1 和 3 短接在一起,引脚 4、5 和 6 短接在一起。3.根据 UL 1577,每个光耦合器都通过施加绝缘测试电压 4800 V RMS 持续 1 秒进行验证测试。4.逻辑高电平下的共模瞬态抗扰度是共模脉冲 V CM 上升沿上的最大可容忍(正)dV CM /dt,以确保输出将保持在逻辑高状态(即,V O > 2.0 V)。逻辑低电平下的共模瞬态抗扰度是共模脉冲信号 V CM 下降沿上的最大可容忍(负)dV CM /dt,以确保输出将保持在逻辑低状态(即,V O < 0.8 V)。5.1.9 k 负载代表 1.6 mA 的 1 TTL 单位负载和 5.6 k 上拉电阻。6.交流输出电压比其中频值低 3 dB 的频率。7.建议使用连接在引脚 4 和 6 之间的 0.1 μF 旁路电容。8.对于任何给定设备,脉冲宽度失真 (PWD) 定义为 |t PHL - t PLH |。9.相同测试条件下任意两个部件之间的 t PLH 和 t PHL 之间的差异。

CA9555 低压 16 位 I2C 和 SMBus I/O 扩展器...

该芯片是一个16位I/O扩展器。它通过I 2 C或SMBus接口为大多数MCU系列提供远程GPIO扩展。CA9555有两个8位输入端口寄存器、输出端口寄存器、配置寄存器(设置为输入或输出)和极性反转寄存器(高电平有效或低电平有效)。上电后,16个I/O引脚配置为输入,并带有至V CC 的内部弱上拉电阻。然而,主机可以通过设置配置寄存器位单独将I/O引脚启用为输入或输出。如果没有外部信号施加到CA9555的I/O引脚,由于内部上拉电阻,电压电平为高。每个输入或输出的数据都存储在相应的输入或输出端口寄存器中。输入端口寄存器的极性可以通过极性反转寄存器反转。主机可以使用上电复位功能复位芯片,复位可能是由于超时或其他不当操作引起的,该功能将所有寄存器复位为默认状态并初始化 I 2 C/SMBus 状态机。该芯片具有输出锁存功能,可在使用高电流能力直接驱动 LED 时保护芯片。当任何输入状态与其对应的输入端口寄存器状态不同时,CA9555 开漏中断输出将被激活,并用于向系统主机指示输入状态已发生变化。可用封装:TSSOP-24、QFN4x4-24 封装。