XiaoMi-AI文件搜索系统

World File Search System微电子与纳电子学系

在过去的几十年中,数字和模拟集成电路的集成密度和性能经历了一场惊人的革命。虽然创新的电路和系统设计可以解释这些性能提升的部分原因,但技术一直是主要驱动力。本课程将研究促成集成电路革命的基本微制造工艺技术,并研究新技术。目标是首先传授构建微型和纳米器件的方法和工艺的实际知识,然后教授将这些方法组合成可产生任意器件的工艺序列的方法。虽然本课程的重点是晶体管器件,但许多要教授的方法也适用于 MEMS 和其他微型器件。本课程专为对硅 VLSI 芯片制造的物理基础和实用方法或技术对器件和电路设计的影响感兴趣的学生而设计。30260133 电子学基础 3 学分 48 学时

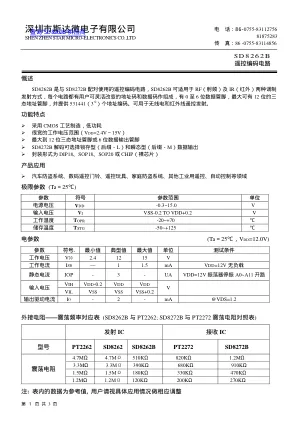

深圳市斯达微电子有限公司

¾ 采用 CMOS 工艺制造,低功耗 ¾ 很宽的工作电压范围( V DD =2.4V ~ 15V ) ¾ 最大到 12 位三态地址管脚或 6 位数据输出管脚 ¾ SD827 2B 解码可选择锁存型(后缀- L )和瞬态型(后缀- M )数据输出 ¾ 封装形式为 DIP18 、 SOP18 、 SOP20 或 CHIP (裸芯片)

博士纳嘎斯瓦鲁帕 HP

卡纳塔克邦迈索尔市卡纳塔克邦开放大学内部质量保证中心 (CIQA) 成员(2023 - 2025 年)。卡纳塔克邦民俗大学 NEP 实施委员会成员,卡纳塔克邦戈塔古迪。2022 - 2023 年度化学研究生考试委员会成员,芒格洛尔大学,2021 - 2022 年,维贾亚纳加拉斯里克里斯赫纳德瓦拉亚大学,巴拉里,2020-2021 年,拉尼·查南玛大学,贝尔高姆。达万格雷大学 2022 - 2023 年、2020-2021 年和 2019 - 2020 年化学研究生考试委员会成员。达万格雷大学 (Davangere University) 2021-2022 年度、2020-2021 年度本科和研究生化学考官委员会成员。达万格雷大学 (Davangere University) 2019-2020 年度研究生和化学研究系系委员会成员。贝尔高姆维斯维斯瓦拉亚科技大学 (VTU) 2019-2020 年度、2016-2017 年度和 2013-2014 年度考官委员会 (化学综合委员会) 成员。曾于 2015 年至 2016 年偶数学期担任 Dayananda Sagar 工程学院的 BOE 成员,于 2014 年奇数学期担任该学院的 BOE 成员,于 2011 年至 2012 年奇数学期担任 Ambedkar 理工学院的 BOE 成员,于 2011 年至 2012 年奇数学期担任 Nitte Meenakshi 理工学院的 BOE 成员,该学院是 VTU(贝尔高姆)的附属自治机构。

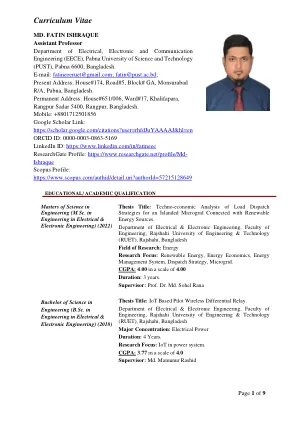

简历 - 帕布纳

MD. FATIN ISHRAQUE 助理教授,孟加拉国帕布纳科技大学(PUST)电气、电子与通信工程(EECE)系,帕布纳 6600。邮箱:fatineeeruet@gmail.com;fatin@pust.ac.bd;现住址:孟加拉国帕布纳 Monsurabad R/A,GA 区,5 号路,174 号楼。永久地址:孟加拉国朗布尔,5400,朗布尔萨达尔,Khalifapara,17 号病房,651/006 号楼。手机:+8801712501856 Google Scholar 链接:https://scholar.google.com/citations?user=rhfdJuYAAAAJ&hl=en ORCID ID:0000-0003-0863-5169 LinkedIn ID:https://www.linkedin.com/in/fatineee ResearchGate 个人资料:https://www.researchgate.net/profile/Md- Ishraque Scopus 个人资料:https://www.scopus.com/authid/detail.uri?authorId=57215128649