XiaoMi-AI文件搜索系统

World File Search System环境辅助的玻色量量子通信

量子假设检验的最终目标是在所有可能的经典策略中实现量子优势。在量子读取方案中,这是从光学内存中获取信息的,其通用单元在两个可能的有损通道中存储了一些信息。我们在理论上和实验上表明,通过实用的光子计数测量结果与模拟最大样本决策相结合,可以获得量子优势。特别是,我们表明该接收器与纠缠的两种模式挤压真空源相结合,能够以相同的平均输入光子数量相干状态的统计混合物胜过任何策略。我们的实验发现表明,量子和简单的光学器件能够增强数字数据的读数,为量子读数的真实应用铺平了道路,并使用基于波斯克尼克损失的二元歧视的任何其他模型进行了潜在应用。

09,13薄锌薄膜的光谱与铜 div>

透明导电金属氧化物已成为研究的主题,这要归功于它们的独特物理特性以及潜在的微观和纳米电子设备和显示单元的应用。这些材料的基本实际应用是基于明显的特异性抗性和高可见的透射率。透明的金属氧化物尤其包括诸如碳锡氧化物,氧化锌,氧化镉等化合物。氧化锌半导体作为压电和光纤材料具有实用的应用潜力,可作为功能性气体传感器组件,表面声设备,透明电极和太阳能电池[1-4]。高光带隙值(〜3。3 eV在室温下)和激子结合能(约60 meV)允许将ZnO作为创建下一代紫外线光电设备和彩色显示单元的磷光器的材料。对于上面提到的许多应用,例如,通过合金来控制ZnO薄膜结构的物理参数的不稳定性是必不可少的。在这种情况下,铜合金添加剂更有效,因为铜是半导体中迅速扩散的杂质,它会导致结晶结构和物理性能的修改,例如,表面状态能量参数以及光学特性[5-7]。后者提供了有关光学主动故障的能量结构的其他信息,这具有很高的实际兴趣。这项研究的目的是研究未扎的ZnO铜掺杂(ZnO:Cu)薄膜的光光谱的行为。

关于给定色数图中奇数圈的加强

我们遵循 [9, 13] 中的符号。设 G 为图。对于 V(G) 的非平凡划分 (A,B),1如果路径 P 的一端在 A 中而另一端在 B 中,则我们称路径 P 为 A - B 路径。设 P 为图 G 中的一条路径。设 | P | 为 P 中的边数。如果 | P | 为偶数(分别为奇数),则我们称 P 为偶数(分别为奇数)。设 C 为按循环顺序具有顶点 v 0 ,v 1 ,...,vt − 1 的环。设 C i,j 表示 C 的子路径 vivi +1...vj,其中索引取自加法群 Z t 。设 H 为 G 的子图。如果顶点 v ∈ V ( G ) − V ( H ) 在 G 中与 V ( H ) 中的某个顶点相邻,则我们称 H 和顶点 v ∈ V ( G ) − V ( H ) 在 G 中相邻。设 NG ( H ) = S v ∈ V ( H ) NG ( v ) − V ( H ) 且 NG [ H ] = NG ( H ) ∪ V ( H )。对于 S ⊆ V ( G ),如果 V ( G ′ ) = ( V ( G ) − S ) ∪{ s } 且 E ( G ′ ) = E ( G − S ) ∪{ vs : v ∈ V ( G ) − S 与 G 中的 S 相邻 } ,我们称图 G ′ 是通过将 S 收缩为顶点 s 而从 G 得到的。如果 G − v 包含至少两个分支,则连通图 G 的顶点 v 是 G 的割顶点。 G 中的块 B 是 G 的最大连通子图,使得不存在 B 的割顶点。注意块是孤立顶点、边或2连通图。G 中的端块是 G 中最多包含一个 G 的割顶点的块。如果 G 是图并且 x, y 是 G 的两个不同顶点,我们称 ( G, x, y ) 为有根图。有根图 ( G, x, y ) 的最小度为 min { d G ( v ) : v ∈ V ( G ) −{ x, y }} 。如果 G + xy 是2连通的,我们还称有根图 ( G, x, y ) 是2连通的。我们称 k 条路径或 k 条循环 P 1 , P 2 , . . . , P k 为

玻色-量子中的自旋动量纠缠

造成量子非局域性和违反贝尔不等式的原因。3纠缠一直是量子信息技术和工艺发展的重要资源。4–13 利用纠缠进行量子信息处理依赖于操纵量子系统的能力,无论是在气相还是固相中。在我们之前的工作中,我们研究了纠缠以及在光学捕获的极性和/或顺磁性分子阵列中进行量子计算的前景,这些分子的斯塔克能级或塞曼能级作为量子比特。13,14 在这里,我们考虑被限制在光阱中的 87 个 Rb 原子的玻色-爱因斯坦凝聚态 (BEC) 15,并研究其自旋和动量自由度之间的纠缠。原子的超精细塞曼能级及其量化动量可以作为量子比特,甚至是更高维的量子比特,即具有 d 维的量子比特。我们注意到,在气态系统中实现玻色-爱因斯坦凝聚态,随后又演示了自旋轨道耦合的玻色-爱因斯坦凝聚态 16,为量子控制开辟了新途径。在反应动力学的背景下,自旋轨道耦合

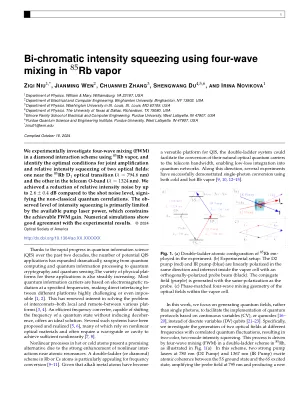

利用四波混频实现双色强度压缩

得益于过去 20 年量子信息科学 (QIS) 的快速发展,潜在的 QIS 应用数量急剧增加,包括量子计算和量子信息处理、量子密码和量子传感。这些应用的物理平台种类也在稳步增加。大多数量子信息载体基于特定频率的电磁辐射,因此不同平台之间的直接接口极具挑战性,甚至不可能实现 [1,2]。这重新引起了人们对解决不同平台之间本地和远程互连问题的兴趣 [3,4]。高效的频率转换器能够改变量子态的频率而不会引起退相干,因此提供了一种理想的解决方案。已经提出并实现了几个这样的系统 [5,6],其中许多依赖于非线性光学材料,并且通常需要波导或腔体来实现足够的非线性 [7,8]。热原子或冷原子中的非线性过程是一种很有前途的替代方案,因为原子共振附近的非线性相互作用得到了强烈的增强。Rb 或 Cs 原子中的双梯形(或菱形)方案对于频率转换特别有吸引力 [9-11]。鉴于碱金属原子已成为

多模捕获的干涉仪与非互操作玻色...

我们在实验上证明了一个多模干涉仪,其中包含一个被困在谐波电势中的39 K原子的玻色子凝结物,在该原子间相互作用中可以取消利用Feshbach的共振。kapitza-dirac从光学晶格中的衍射将BEC一致地分配在多个动量成分中,同样间隔,形成了不同的干涉路径,而轨迹被捕获的har-nonig势封闭。我们研究了两种不同的干涉方案,其中重组脉冲是在确定电位的全部或一半振荡后应用的。我们发现,干涉仪输出处动量成分的相对幅度通过诱导的谐波电位相对于光学晶格的诱导位移对外力敏感。我们展示了如何校准干涉仪,充分表征其输出并讨论透视改进。

柔性基板上薄硅片的倒装芯片组装

减薄硅芯片在柔性基板上的倒装芯片组装 Tan Zhang、Zhenwei Hou 和 R. Wayne Johnson 奥本大学 阿拉巴马州奥本 Alina Moussessian 和 Linda Del Castillo 喷气推进实验室 加利福尼亚州帕萨迪纳 Charles Banda 物理科学实验室 摘要 将减薄硅芯片(25-100 µ m)组装到柔性基板上为从智能卡到太空雷达等各种应用提供了超薄柔性电子产品的选择。对于高密度应用,可以通过堆叠和层压预组装和测试的柔性层然后处理垂直互连来制造 3-D 模块。本文介绍了将减薄芯片倒装芯片组装到聚酰亚胺和液晶聚合物 (LCP) 柔性基板上的工艺。已经开发出两种用于聚酰亚胺和 LCP 柔性基板的组装方法。在第一种方法中,将焊料凸块芯片回流焊接到图案化柔性基板上。需要使用夹具在回流期间保持柔性基板平整。回流之后是底部填充分配和固化。底部填充分配工艺对于避免底部填充流到薄硅片顶部至关重要,我们将在下文中讨论这一工艺。在第二种方法中,通孔通过聚酰亚胺或 LCP 蚀刻,露出接触垫的底面。将焊膏挤入通孔,回流并清洗,在通孔中形成焊料“凸块”。对浸焊产生的具有低轮廓焊料凸块的芯片进行焊剂处理、放置和回流。然后对芯片进行底部填充。这种方法可降低总组装厚度。简介为了满足单芯片和堆叠芯片封装中不断降低的轮廓要求,正在开发薄芯片的组装工艺。1-4 柔性基板(25-50 µ m)提供了一种进一步减小封装厚度的方法。减薄的 Si-on-flex 结构也有利于太空应用。减薄的 Si 虽然易碎,但也很灵活。减薄的 Si-on-flex 可以卷成管状进行发射,并在太空中展开,从而形成带有集成电子设备的大面积天线。组装减薄的 Si-on-flex 必须解决的问题包括:基板设计和制造、减薄后的凸块、芯片处理、回流期间的基板平整度和底部填充分配。这些将在以下章节中讨论。基板本工作中使用了两种柔性基板材料:聚酰亚胺和液晶聚合物 (LCP)。LCP 特性包括 100GHz 下的良好介电性能、低吸湿性和极低的透湿性。5-13 LCP 的热膨胀系数 (CTE) 可以在 LCP 薄膜的双轴挤出过程中控制。市售薄膜的 CTE 为 8 和 17ppm/o C。在本工作中使用 8ppm/o C LCP 薄膜。在用于倒装芯片组装的传统柔性基板设计中,铜芯片连接点的图案化位置与芯片组装位置在柔性薄膜的同一侧(图 1)。阻焊层用于定义可焊焊盘区域(顶面设计)。另一种方法是蚀刻聚酰亚胺或 LCP 通孔,露出铜焊盘的底面(背面设计)。通孔通过激光钻孔或反应离子蚀刻 (RIE) 制成。倒装芯片从铜图案的对面组装(图 2),从而无需阻焊层并减小了总厚度。这种方法的另一个优点(低轮廓凸块)将在后面介绍。顶面聚酰亚胺基板由约翰霍普金斯大学应用物理实验室制造,而激光钻孔背面 LCP 设计由 STS ATL 公司制造。背面 (RIE) LCP 和聚酰亚胺基板由奥本大学制造。只需一层金属即可布线菊花链芯片互连图案。

HF/H2O中硅片减薄的刻蚀特性...

R. Ariff a,b , CK Sheng a,* a 马来西亚登嘉楼大学科学与海洋环境学院,21030 Kuala Nerus,登嘉楼,马来西亚。b 马来西亚登嘉楼大学海洋工程技术与信息学学院,21030 Kuala Nerus,登嘉楼,马来西亚。使用酸性或氟化物溶液对硅表面进行湿法蚀刻具有技术和基础意义,这对于生产用于微电子封装所需厚度的可靠硅芯片至关重要。在这项工作中,我们研究了湿法蚀刻对浸入 48% HF/水溶液中的硅晶片的厚度耗散、重量损失、蚀刻速率、表面形貌和晶体性质的影响。蚀刻速率是通过蚀刻重量损失和深度随时间的变化确定的。结果表明,随着蚀刻时间的增加,硅的厚度减少和重量损失增加。在高分辨率光学显微镜下可以在蚀刻后的硅晶片表面观察到粗糙的表面。从 XRD 分析可以看出,蚀刻后硅的结晶峰强度变弱,这意味着硅衬底上形成的非晶结构表面的光散射减少。毕竟,这一发现可以作为生产可靠的硅薄晶片的参考,这对于更薄的微电子器件制造和纳米封装至关重要,从而减少环境污染和能源消耗,实现未来的可持续发展。(2021 年 3 月 27 日收到;2021 年 7 月 7 日接受)关键词:湿法蚀刻、Si、蚀刻速率、HF、H 2 O

薄列列聚合物网络的山脊能量

抽象将平滑等距沉浸式列表聚合物网络的薄板的弹性自由能最小化是主流理论所声称的策略。在本文中,我们拓宽了可允许的自发变形类别:我们考虑脊层浸入式浸入,这可能会导致浸入浸入的表面尖锐的山脊。我们提出了一个模型,以计算沿此类山脊分布的额外能量。这种能量来自弯曲;在什么情况下,它显示出与薄板的厚度四相缩放,落在拉伸和弯曲能量之间。,我们通过研究磁盘的自发变形,将径向刺猬的自发变形置于测试中。我们预测了外部试剂(例如热量和照明)在材料中诱导的材料诱导的顺序程度而发展的褶皱数量。

薄金属基材上的多层磁场发射器 div>

这项工作的目的是确定从材料接触中创建多层阴极的可能性,其在薄金属基板上的不同输出的不同输出,以及在微型流中,在电子流的交叉部分中形成密集的胶带和环的实际使用,但高电量设备。方法。gafnii层(𝑒3〜3。5 eV)和铂(𝑒3〜5。3 eV)分别使用相当简单且操作的Magnetron喷涂方法顺序将10 nm和2 nm依次应用于金属箔底物的侧面。阴极由箔制成,并用多层涂层在电子束的横截面中形成胶带和环。在三极管电子光学系统中产生了多层阴极发行特性及其形成的光束的实验测量,其中包括控制电极(阳极)和选举收集器的阴极以Pharanda圆柱体的形式进行。测量是在技术真空10-7的条件下进行的。。。10-8 Torr。 结果。 实验定义了由三极管电子光系统形成的电子流的横截面的特征和环在薄铝基板(9微米)和坦塔鲁斯(10微米)上形成的电子流的横截面。 测量了从阴极的电流对Cato室和控制电极之间电压(Volt-Ampere特性)之间的电压的依赖性,以及所形成的束的电子光系统中电流的变化。 结论。 。 。10-8 Torr。结果。实验定义了由三极管电子光系统形成的电子流的横截面的特征和环在薄铝基板(9微米)和坦塔鲁斯(10微米)上形成的电子流的横截面。测量了从阴极的电流对Cato室和控制电极之间电压(Volt-Ampere特性)之间的电压的依赖性,以及所形成的束的电子光系统中电流的变化。结论。。。在本文中,在电子流的薄金属基板上使用多层天主管在电子流的薄金属基板上进行了形成,并在高达300的田间发射场的横截面中,电流的横截面最大为几米,平均水平极大。400 A/cm 2。在选择技术真空中选择大型田间发射时,研究的阴极稳定运行的可能性。