XiaoMi-AI文件搜索系统

World File Search System用于量子计算系统的基于 FPGA 的可重构信道化,使用多相滤波器组

摘要。最近提出的量子系统使用频率复用量子比特技术来读取电子器件,而不是模拟电路,以提高系统的成本效益。为了恢复单个通道以供进一步处理,这些系统需要一种解复用或通道化方法,该方法可以低延迟处理高数据速率,并且使用很少的硬件资源。本文介绍了一种使用多相滤波器组 (PFB) 信号处理算法的低延迟、适应性强的基于 FPGA 的通道器。由于只需设计一个原型低通滤波器来处理所有通道,因此 PFB 可以轻松适应不同的要求,并进一步简化滤波器设计。由于每个通道都重复使用相同的滤波器,与传统的数字下变频方法相比,它们还降低了硬件资源利用率。实现的系统架构具有广泛的通用性,允许用户从不同数量的通道、采样位宽度和吞吐量规格中进行选择。对于使用 28 系数转置滤波器和 4 个输出通道的测试设置,所提出的架构可产生 12.8 Gb/s 的吞吐量和 7 个时钟周期的延迟。

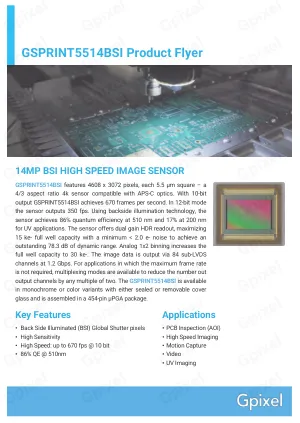

GSPRINT5514BSI 产品传单

GSPRINT5514BSI 具有 4608 x 3072 像素,每个像素为 5.5 µm 见方 - 4/3 宽高比 4k 传感器,与 APS-C 光学元件兼容。GSPRINT5514BSI 具有 10 位输出,可实现每秒 670 帧。在 12 位模式下,传感器输出 350 fps。使用背面照明技术,对于 UV 应用,传感器在 510 nm 处实现 86% 的量子效率,在 200 nm 处实现 17% 的量子效率。该传感器提供双增益 HDR 读出,最大限度提高 15 ke- 满阱容量,最小 < 2.0 e- 噪声,实现出色的 78.3 dB 动态范围。模拟 1x2 合并将满阱容量增加到 30 ke-。图像数据通过 84 个 sub-LVDS 通道以 1.2 Gbps 的速度输出。对于不需要最大帧速率的应用,可以使用多路复用模式将输出通道数减少 2 的任意倍数。GSPRINT5514BSI 有单色或彩色版本,配有密封或可拆卸盖玻片,并采用 454 针 µPGA 封装。

深圳Lianxinke Micro-Electronics Co.,Ltd.地址

lianxinke智能自动编码系列采用了专利的技术,具有智能的多用量误差识别编码线,该技术稳定而可靠地实现了全日制自动编码。它还支持0个场功能原型IC应用程序,并且在交付灯后不需要编码。工程安装和售后维护非常方便,并且可以将智能自动编码系列中不同的IC系列混合在灯中以进行自动编码。ucs512h系列使用DMX512差分并行协议LED驱动器芯片,并支持1/2/2/3/4局部高精确常数恒定电流输出和65536灰度级别。UCS512H系列采用第二代自适应微频转换技术开发的灰度平滑函数,以最大程度地发挥低灰色和无抖动的效果。最多32K端口的刷新速率可改善射击效果,地址线检测模式可以迅速通过地址线失败定位灯。芯片提供4个高精度恒定电流输出通道为120mA。电流的输出大小可以由外部电阻器设置,并且每个通道的电流可以通过软件独立调整64个级别。

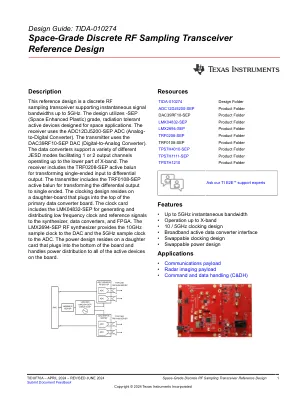

太空级离散RF采样收发器参考设计(Rev. A)

此参考设计是一个离散的RF采样收发器,支持瞬时信号带宽高达5GHz。设计利用-sep(空间增强的塑料)等级,辐射耐受的活性设备,设计用于空间应用。接收器使用ADC12DJ5200-SEP ADC(模数转换器)。发射器使用DAC39RF10-SEP DAC(数字到Analog转换器)。数据转换器支持各种不同的JESD模式,这些模式促进了1或2个输出通道,直至X波段的下部。接收器包括TRF0208-SEP活动Balun,用于将单端输入转换为差分输出。发射器包括TRF0108-SEP活动balun,用于将差分输出转换为单端。时钟设计位于插入主要数据转换器板顶部的子板上。时钟卡包括用于生成和分发低频时钟和参考信号向合成器,数据转换器和FPGA的LMK04832-SEP。LMX2694-SEP RF合成器将10GHz样品时钟和5GHz样品时钟提供给ADC。电源设计位于插入板底部的女儿卡上,并将电源分配处理到板上的所有活动设备上。

CS6008 - 人机交互

第一单元 HCI 基础 人类:输入/输出通道 – 内存 – 推理和解决问题;计算机:设备 – 内存 – 处理和网络;交互:模型 – 框架 – 人体工程学 – 风格 – 元素 – 交互性 – 范例。第二单元 设计与软件过程 交互设计基础 – 过程 – 场景 – 导航 – 屏幕设计 – 迭代和原型设计。软件过程中的 HCI – 软件生命周期 – 可用性工程 – 实践中的原型设计 – 设计原理。设计规则 – 原则、标准、指南、规则。评估技术 – 通用设计。第三单元 模型与理论 认知模型 – 社会组织问题和利益相关者要求 – 通信与协作模型 – 超文本、多媒体和 WWW。单元 IV 移动 HCI 移动生态系统:平台、应用框架 - 移动应用类型:小部件、应用、游戏 - 移动信息架构、移动 2.0、移动设计:移动设计元素、工具。单元 V 网页界面设计 设计网页界面 - 拖放、直接选择、上下文工具、覆盖、嵌入和虚拟页面、流程。案例研究。总计:45 节课 教材: 1.Alan Dix、Janet Finlay、Gregory Abowd、Russell Beale,“人机交互”,第 3 版,Pearson Education,2004 年(UNIT I、II 和 III) 2.Brian Fling,“移动设计与开发”,第一版,O'Reilly Media Inc.,2009 年(UNIT –IV) 3.Bill Scott 和 Theresa Neil,“设计 Web 界面”,第一版,O'Reilly,2009 年。(UNIT

CS6008 - 人机交互

第一单元 人机交互基础 人类:输入/输出通道 – 内存 – 推理和解决问题;计算机:设备 – 内存 – 处理和网络;交互:模型 – 框架 – 人机工程学 – 风格 – 元素 – 交互性 – 范例。 第二单元 设计与软件过程 交互设计基础 – 过程 – 场景 – 导航 – 屏幕设计 – 迭代和原型设计。软件过程中的人机交互 – 软件生命周期 – 可用性工程 – 实践中的原型设计 – 设计原理。设计规则 – 原则、标准、指南、规则。评估技术 – 通用设计。 第三单元 模型与理论 认知模型 – 社会组织问题和利益相关者要求 – 通信与协作模型 – 超文本、多媒体和万维网。第四单元 移动 HCI 移动生态系统:平台、应用框架 - 移动应用类型:小部件、应用、游戏 - 移动信息架构、移动 2.0、移动设计:移动设计元素、工具。 第五单元 网页界面设计 设计网页界面 - 拖放、直接选择、上下文工具、覆盖、嵌入和虚拟页面、流程流。案例研究。 总计:45 节课 教科书: 1. Alan Dix、Janet Finlay、Gregory Abowd、Russell Beale,《人机交互》,第三版,Pearson Education,2004 年(第一单元、第二单元和第三单元) 2. Brian Fling,《移动设计和开发》,第一版,O'Reilly Media Inc.,2009 年(第四单元) 3. Bill Scott 和 Theresa Neil,《设计网页界面

通过...

摘要 - 基于CPU的推理可以作为外芯片加速器的拟合作用。在这种情况下,由于其高效率,新兴的矢量体系结构是一个有前途的选择。然而,卷积算法和硬件实现的庞大设计空间使设计选项的选择具有挑战性。在本文中,我们介绍了针对基于CPU的卷积神经网络(CNN)推断的共同设计的未来矢量体系结构的持续研究,重点是IM2Col+Gemm和Winograd内核。使用GEM5模拟器,我们探讨了几个硬件微体系特征的影响,包括(i)向量泳道,(ii)向量长度,(iii)缓存尺寸和(iv)将向量单元集成到CPU管道中的选项。In the context of im2col+GEMM, we study the impact of several BLIS-like algorithmic optimizations such as (1) utilization of vector registers, (2) loop unrolling, (3) loop reorder, (4) manual vectorization, (5) prefetching, and (6) packing of matrices, on the RISC-V Vector Extension and ARM-SVE ISAs.我们使用Yolov3和VGG16网络模型进行评估。我们的共同设计研究表明,BLIS样的优化对所有类型的矢量微体系结构都不是有益的。我们还证明,与我们优化的CNN内核相比,较长的矢量长度(至少为8192位)和较大的缓存(256MB)可以提高5倍的性能,而512位和1MB的载体长度则可以提高性能。我们的共同设计研究还表明,与IM2Col+GEMM相比,Winograd需要较小的缓存尺寸(高达64MB)。在Winograd的背景下,我们通过使用每个通道的8×8图块来介绍跨输入/输出通道之间的新颖的瓷砖并行方法,以对向量长度不可知(VLA)体系结构进行载体化算法。我们的方法利用了较长的向量长度并提供了高内存重复使用,与我们在Fujitsu A64FX处理器上优化的IM2Col+Gemm方法相比,对于具有3×3内核大小的非弯曲卷积层的性能提高了2.4倍。索引术语 - CNN,GEMM,Winograd,长量架构,向量长度不可知论ISA,共同设计,优化

TESIRAFORTÉ® 和 AI 固定 I/O DSP 数据表

固定 I/O DSP 应专门设计用于 Tesira® 系统。固定 I/O DSP 应支持 Dante™ 数字音频网络,最多可支持 32 x 32 个通道。Dante 网络连接应在 RJ-45 连接器上实现。固定 I/O DSP 应根据 AES67 标准实现互操作。固定 I/O DSP 应支持以太网连接,用于在 RJ-45 连接器上进行编程和控制。固定 I/O DSP 应具有内部 DSP 处理功能。固定 I/O DSP 应包括 4 个通用输入和输出连接 (GPIO) 通道,用于发送或接收逻辑信号。GPIO 端口的编程应为软件可配置的。固定 I/O DSP 应包括 RS-232 连接,用于控制数据传输到固定 I/O DSP 或从固定 I/O DSP 传输数据,并且此类操作应为软件可编程的。固定 I/O DSP 应包括标准 USB-B 型连接器上的通用串行总线 (USB) 连接。固定 I/O DSP 应可由软件配置,以便将最多 8 个通道的数字 USB Class 1 音频传输流式传输到固定 I/O DSP 或从固定 I/O DSP 传输出去,或同时输入和输出。固定 I/O DSP 应支持通过 IEEE 802.1X 进行端口身份验证。固定 I/O DSP 应提供 12 个平衡输入连接,用于接收旋入式可拆卸连接器上的麦克风或线路电平模拟音频信号。固定 I/O DSP 应提供 8 个平衡输出通道,用于传输旋入式可拆卸连接器上的麦克风或线路电平模拟音频信号。每个单独的通道都应有自己的专用连接。固定 I/O DSP 应在前面板 OLED 上提供设备电源、状态、警报和活动以及系统范围警报的标识。固定 I/O DSP 应为机架安装式 (1RU),并具有软件可配置的信号处理功能,包括但不限于:信号路由和混合、均衡、滤波、动态和延迟,以及控制、监控和诊断工具。固定 I/O DSP 应带有 CE 标志、UL 认证,并应符合 RoHS 指令。保修期为五年。固定 I/O DSP 应为 TesiraFORTÉ® DAN AI。

DNx-AI-256

一般描述 DNx-AI-256 是高性能双通道同步器/解析器输入和输出板,与 UEI 强大的 Cube、RACKtangle 和 FLATRACK I/O 机箱兼容。256 系列板在功能上与 DNx-AI-255 类似,但为需要它的应用提供了更多的输出驱动。DNx-AI-256 系列也是 LVDT/RVDT 的理想解决方案。该板可以配置为两个输入、两个输出或一个输入和一个输出。该板提供 2 个输入通道,可监控 3 线同步器或 4 线解析器。该板的高精度电路与每个通道独立的 16 位 A/D 转换器相结合,可实现高达 ± 2.6 弧分的测量精度。输入的读取速率最高可达激励频率(最大 10 kHz)。每个通道均提供自己的可编程参考,输出可独立编程,最高可达 19.8 Vrms,频率范围为 50 至 10 kHz,最高可达 2.4 VA。使用外部参考时,DNR-AI-256 可在一个参考周期内自动调整模拟输出,以获得可变幅度和频率参考。DNx-AI-256 还提供两个同步器/解析器/RVDT/LVDT 接口通道,非常适合用于姿态指示器等设备,或作为各种同步器或解析器输入设备的测试源。每个输出均接受独立的参考信号,并提供 16 位输出分辨率。无需外部缓冲,每个通道将以 3.0 VA 驱动高达 19.8 Vrms(总板输出必须小于或等于 5 VA)。可以监控每个输出通道消耗的电流,以确认接线正确,同步器/解析器或 RVDT/LVDT 的线圈符合预期。该板在通道之间以及 I/O 连接和底盘之间提供 350 Vrms 隔离。与所有 PowerDNA/UEILogger I/O 板一样,DNx-AI-256 可在恶劣环境下运行,并已通过 3g 振动、50g 冲击、-40 至 +70 °C 温度和高达 70,000 英尺的高度测试。包含软件,提供全面且易于使用的 API,支持所有流行操作系统,包括 Windows、Linux 和大多数实时操作系统(如 QNX、Intime、VXworks 等)。此外,UEIDAQ 框架(更高级别的 Windows 驱动程序)为使用多种流行 Windows 编程语言创建应用程序的用户以及 LabVIEW 和 MATLAB/Simulink 等数据采集软件包提供全面支持。由于 DNR-AI-256 具有高功率输出,因此应在其旁边的插槽中放置一个风扇装置以防止过热。风扇装置 DNR-FAN-925 包含在 DNR-AI-256 中。