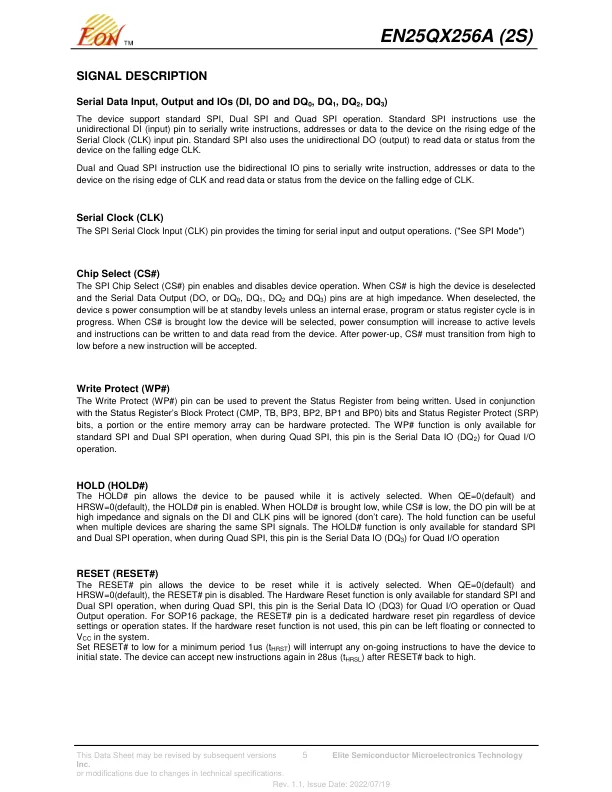

写保护 (WP#) 写保护 (WP#) 引脚可用于防止写入状态寄存器。与状态寄存器的块保护 (CMP、TB、BP3、BP2、BP1 和 BP0) 位以及状态寄存器保护 (SRP) 位一起使用,可以对部分或整个内存阵列进行硬件保护。WP# 功能仅适用于标准 SPI 和双 SPI 操作,在四路 SPI 期间,此引脚为四路 I/O 操作的串行数据 IO (DQ 2)。保持 (HOLD#) HOLD# 引脚允许在设备被主动选择时暂停设备。当 QE=0(默认)和 HRSW=0(默认)时,HOLD# 引脚启用。当 HOLD# 被拉低时,CS# 为低,DO 引脚将处于高阻抗状态,DI 和 CLK 引脚上的信号将被忽略(无关)。当多个设备共享相同的 SPI 信号时,保持功能非常有用。 HOLD# 功能仅适用于标准 SPI 和 Dual SPI 操作,在 Quad SPI 期间,此引脚为 Quad I/O 操作的串行数据 IO(DQ 3)。 RESET(RESET#) RESET# 引脚允许在设备被主动选择时对其进行复位。当 QE=0(默认)和 HRSW=0(默认)时,RESET# 引脚被禁用。 硬件复位功能仅适用于标准 SPI 和 Dual SPI 操作,在 Quad SPI 期间,此引脚为 Quad I/O 操作或 Quad Output 操作的串行数据 IO(DQ3)。对于 SOP16 封装,RESET# 引脚是专用的硬件复位引脚,与设备设置或操作状态无关。如果不使用硬件复位功能,此引脚可以悬空或连接到系统中的 V CC 。将 RESET# 设置为低电平最短 1us(t HRST )将中断任何正在进行的指令,使设备处于初始状态。 RESET# 恢复高电平后,设备可以在 28us(t HRSL )内再次接受新指令。

EN25QX256A (2S)

主要关键词