XiaoMi-AI文件搜索系统

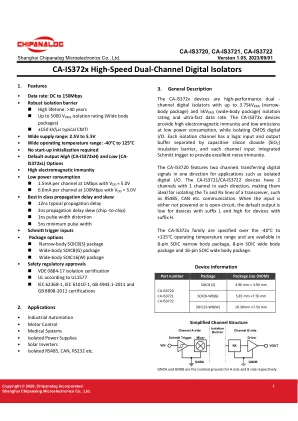

World File Search SystemCA-IS372x 高速双通道数字隔离器

• 数据速率:DC 至 150Mbps • 坚固的隔离屏障 长使用寿命:>40 年 高达 5000 V RMS 隔离额定值(宽体封装) ±150 kV/μs 典型 CMTI • 宽电源范围:2.5V 至 5.5V • 宽工作温度范围:-40°C 至 125°C • 无需启动初始化 • 默认输出高 (CA-IS372xH) 和低 (CA-IS372xL) 选项 • 高电磁抗扰度 • 低功耗 1Mbps 时每通道 1.5mA,V DD = 5.0V 100Mbps 时每通道 6.6mA,V DD = 5.0V • 最佳传播延迟和偏斜 12ns 典型传播延迟 2ns 传播延迟偏斜(芯片到芯片) 1ns 脉冲宽度失真 5ns 最小脉冲宽度• 施密特触发器输入 • 封装选项 窄体 SOIC8(S) 封装 宽体 SOIC8(G) 封装 宽体 SOIC16(W) 封装 • 安全法规认证 VDE 0884-17 隔离认证 UL 符合 UL1577 要求 IEC 62368-1、IEC 61010-1、GB 4943.1-2011 和 GB 8898-2011 认证

呈现传播光的新颖观点

摘要。我们提出了一种成像和神经渲染技术,该技术旨在综合通过小说,移动的相机观点从场景中传播光的视频。我们的方法依赖于新的超快成像设置来捕获具有Picsecond级的时间分辨率的首个,多视频视频数据集。与此数据集结合使用,我们基于瞬态字段引入了一个有效的神经音量渲染框架。该字段定义为从3D点和2D方向到高维离散时间信号的映射,该信号代表Ultrafast PlideScales的时间变化。使用瞬态字段渲染自然会由于光速有限而产生影响,包括摄像机传播延迟引起的观点依赖的外观变化。我们产生一系列复杂的效果,包括散射,镜面反射,折射和衍射。此外,我们还使用时间扭曲过程,相对论效应的渲染以及光传输的直接和全局组件的视频综合来证明取消依赖观点的传播延迟。

统计策略来捕捉纳米 CMOS 逆变器中过冲效应和传播延迟时间之间的相关性

引言近年来,统计变异性 (SV) 对纳米 CMOS 电路时序的影响引起了广泛关注[1]–[8]。SV 使数字电路在关键路径延迟甚至功耗方面表现出非确定性性能,而不是确定性行为。SV 的主要来源包括随机掺杂波动 (RDF)、线边缘粗糙度 (LER) 和金属颗粒粒度 (MGG) [9]–[11]。这些来源影响器件电气性能指标,如阈值电压 (V th)、关态电流和亚阈值斜率 (SS),进而对电路行为产生重大影响。特别是,文献 [12]–[20] 广泛研究了工艺和随机变异性对传播延迟时间的影响。在一项开创性的工作中,作者提出了一个半解析模型来预测由 V th 变化引起的逻辑电路延迟分布 [12]。不同技术节点下由 RDF 引起的传播延迟变化是综合的

Petri 网:应用 - CIn UFPE

X GSPN 在局域计算机网络建模和评估中的应用 Masahiro Tsunoyama* 和 Hiroei Imai ** * 新潟工业大学信息与电子工程系 1719 Fujihashi, Kashiwazaki 945-1195, JAPAN 电子邮件:mtuno@iee.niit.ac.jp ** 新潟大学大学评估中心,8050 Ikarashi-2, Niigata-shi, Niigata 950-2181, JAPAN 电子邮件:himai@adm.niigata-u.ac.jp 1.简介 通过计算机网络连接的多媒体系统广泛应用于电信、远程教育和视频点播等应用领域(Nerjes 等,1997;Kornkevn & Lilleberg,2002;Shahraray 等, 2005)。由于多媒体数据具有实时属性,必须在给定的期限内进行处理和交付,因此对此类系统的需求正在增加(Althun 等,2003;Gibson & David,2007)。为了保持所需的质量,已经提出了几种使用 QoS 技术的系统(Furguson & Huston,1998;Park,2006;Villalon 等,2005)。IEEE802.11e(IEEE 标准,2003)就是其中一种技术。它为 QoS 支持提供了两种功能:增强分布式信道访问 (EDCA) 和混合协调功能控制信道访问 (HCCA)。HCCA 使用集中控制并保证所需的传播延迟。另一方面,EDCA采用分布式控制,具有良好的可扩展性,并且所需的开销比HCCA要小,但无法保证所需的传播延迟。为了评估使用QoS的多媒体系统的可靠性,例如支持EDCA的IEEE802.11e,必须定量评估传播延迟及其标准偏差(抖动)(Claypool & Tanner,1999;Fan et al.,2006;Gibson & David,2007;Park,2006)。已经提出了几种评估方法,例如排队网络(Ahmad 等,2007;Cheng & Wu,2005)、随机过程模型(German,2000;Nerjes 等,1997)和模拟模型(Adachi 等,1998;Bin 等,2007;Grinnemo & Brunstrom,2002)。但是,这些方法存在几个问题。排队网络和随机过程模型是分析模型,不需要很长时间进行计算。但是,很难对给定的系统进行建模,因为模型中的状态数量会随着系统规模的增加而呈指数增长,尤其是当系统庞大而复杂时。虽然仿真模型用于评估系统,但它们需要很长时间才能获得有关标准偏差(抖动)的统计数据。本章提出了一种使用广义随机 Petri 网和标记任务方法评估系统的方法

TPS2000B系列数字存储示波器用户手册

应用示例 ................................................................................................................ 37 进行简单测量 .............................................................................................................. 38 使用自动量程检查一系列测试点 .............................................................................. 43 使用隔离通道分析差分通信信号 .............................................................................. 44 查看数学瞬时功率波形 ............................................................................................. 45 进行光标测量 ............................................................................................................. 46 分析信号细节 ............................................................................................................. 50 捕获单次信号 ............................................................................................................. 51 测量传播延迟 ............................................................................................................. 53 特定脉冲宽度触发 ............................................................................................................. 54 视频信号触发 ............................................................................................................. 55 查看网络中的阻抗变化 ............................................................................................. 59 数学 FFT ............................................................................................................. 61 设置时域波形 .............................................................................................

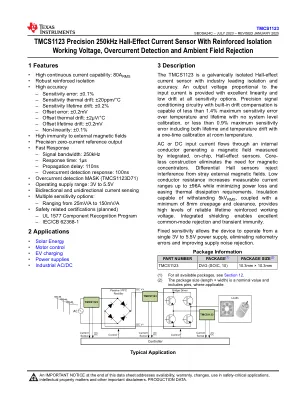

TMCS1123 精密 250kHz 霍尔效应电流传感器,具有增强隔离工作电压、过流检测和环境场抑制功能 数据表 (Rev. C)

• 高连续电流能力:80A RMS • 坚固的增强隔离 • 高精度 – 灵敏度误差:±0.1% – 灵敏度热漂移:±20ppm/°C – 灵敏度寿命漂移:±0.2% – 失调误差:±0.2mV – 失调热漂移:±2μV/°C – 失调寿命漂移:±0.2mV – 非线性:±0.1% • 高外部磁场免疫力 • 精密零电流参考输出 • 快速响应 – 信号带宽:250kHz – 响应时间:1µs – 传播延迟:110ns – 过流检测响应:100ns • 过流检测 MASK (TMCS1123D71) • 工作电源范围:3V 至 5.5V • 双向和单向电流感应 • 多种灵敏度选项: – 范围从 25mV/A 到 150mV/A • 安全相关认证(计划中) – UL 1577 元件识别程序 – IEC/CB 62368-1

具有最小时钟周期的性能增强计数器

摘要。同步二进制计数器是 VLSI 设计中常用的基本组件。同步二进制计数器速度快,可用于许多应用,因为它支持宽位宽。由于扇出量大和进位链长,许多以前的计数器在计数器尺寸较大时计数率较低。提出了一种新的同步二进制计数器快速结构,计数器尺寸从 8 位到 128 位,延迟非常低。为了降低硬件的复杂性,使用了 1 位约翰逊计数器,然后复制它以最大限度地减少大扇出引起的传播延迟。建议的设计是用少量的触发器实现的,使用一个后进位传播计数器和一个基于状态前瞻逻辑的计数器,从而降低了功耗和延迟。

如果引用本文,请使用 DSD 参考文献:Leandro Lanzieri、Lukasz Butkowski、Jiri Kral、Goerschwin Fey、Holger Schlarb 和 Thomas C. Sch

摘要 — 越来越多的未加固的商用现货嵌入式设备部署在恶劣的操作条件下和高度可靠的系统中。由于影响这些设备的硬件退化的机制,老化检测和监控对于防止严重故障至关重要。在本文中,我们通过实证研究了部署在欧洲 XFEL 粒子加速器中的 298 个自然老化的 FPGA 设备的传播延迟。根据现场测量,我们发现运行设备的开关频率明显慢于未使用的芯片,并且伽马和中子辐射剂量的增加与硬件退化的增加相关。此外,我们证明了开发机器学习模型的可行性,该模型基于历史和环境数据估计设备的开关频率。索引术语 — 嵌入式硬件、硬件退化、FPGA

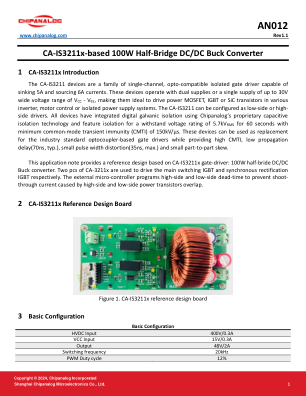

基于 CA-IS3211x 的 100W 半桥 DC/DC 降压转换器

CA-IS3211 器件是一系列单通道、光电兼容隔离栅极驱动器,能够吸收 5A 电流并提供 6A 电流。这些器件采用双电源或高达 30V 的单电源供电,电压范围为 V CC - V EE ,非常适合驱动各种逆变器、电机控制或隔离电源系统中的功率 MOSFET、IGBT 或 SiC 晶体管。CA-IS3211 可配置为低侧或高侧驱动器。所有器件都采用 Chipanalog 专有的电容隔离技术,集成数字电流隔离,隔离耐压额定值为 5.7kV RMS,持续 60 秒,最小共模瞬变抗扰度 (CMTI) 为 150kV/μs。这些设备可以用于替代行业标准的基于光耦合器的栅极驱动器,同时提供高 CMTI、低传播延迟(典型值 70ns)、小脉冲宽度失真(最大值 35ns)和小部件间偏差。

IRS211(0,3)、IR211(0,3) 和 2ED2110S06M 比较

相比之下,2ED2110S06M 驱动器代表了一项重大进步,采用了使其与众不同的现代设计功能。这款新一代栅极驱动器可在更高的电压下工作,最高支持 650V,并包含一个集成自举二极管。这种集成减少了元件数量,简化了设计,并提高了空间和稳健性至关重要的应用中的可靠性。2ED2110S06M 还采用了英飞凌的薄膜绝缘硅 (SOI) 技术,该技术具有出色的抗噪性和闩锁保护功能,使其在嘈杂的环境中具有极强的弹性。更快的传播延迟(开启时缩短至 90 纳秒,关机时缩短至 100 纳秒)使该驱动器成为高速开关应用的理想选择,例如高级电机驱动器、高频逆变器和工业电源。