XiaoMi-AI文件搜索系统

World File Search System移动循环DNA调节CNS神经元中的内存和通信

刺激神经元引起的刺激会引起直接与早期基因的转录,这一过程需要在几分钟内通过托泊异构体IIB产生的染色体DNA局部位点形成双链断裂(DSB),然后在几个小时内修复。清醒,探索新的环境以及上下文恐惧条件也引起了需要DSB和修复的突触基因的转折。已有报道(在非神经元细胞中),在修复位点时,在DSB上会形成外粒体圆形DNA。i提出,激活的神经元可能在DSB部位修复过程中会产生外圆形圆形DNA,从而产生该活性模式的持久“标记”,这些模式包含来自其原产地点的序列并调节长期基因表达。尽管外染色体外DNA的种群是多种多样的,并且总体上与病理学相关,该病理是一个小圆形DNA的子类(“ microdnas”,长约100-400个碱基),很大程度上源自独特的基因组序列,并且具有吸引人的吸引力,并且具有吸引人的特征,可作为稳定,移动圆形DNA,以调节基本表达序列中的序列化型(序列)。圆形DNA可以是RNA转录的模板,尤其是抑制性的siRNA,圆形RNA和其他与microRNA相互作用的非编码RNA。这些可能调节与突触可塑性,学习和记忆有关的其他基因的翻译和转录。移动DNA的另一个可能的命运是在响应随后的激活事件而生成新的DSB站点后,将稳定地插入染色体中。因此,将移动DNA插入活性引起的基因可能倾向于使它们失活并有助于稳态调节以避免过度激发,并为神经元的激活史提供了“计数器”。此外,激活的神经元释放分泌外泌体,可以转移到受体细胞中以调节其基因表达。可移动DNA可以包装到外泌体中,以活动依赖性方式释放,并转移到受体细胞中,在那里它们可能是调节性RNA的模板,并可能掺入染色体中。最后,衰老和神经退行性疾病(包括阿尔茨海默氏病)也与神经元中DSB的增加有关。将来要评估病理学与活动引起的移动DNA以及后者是否有可能有助于发病机理的病理学与活动有关。

b'\ xcb \ x98引导erom + 2 mbytes eRam w/ecc \ xcb \ x98内存接口(挥发性)\ xcb \ x98 ddr2/ddr3/ddr3/ddr4 \ xcb \ xcb \ x98存储器接口(非挥发性)内存传输'

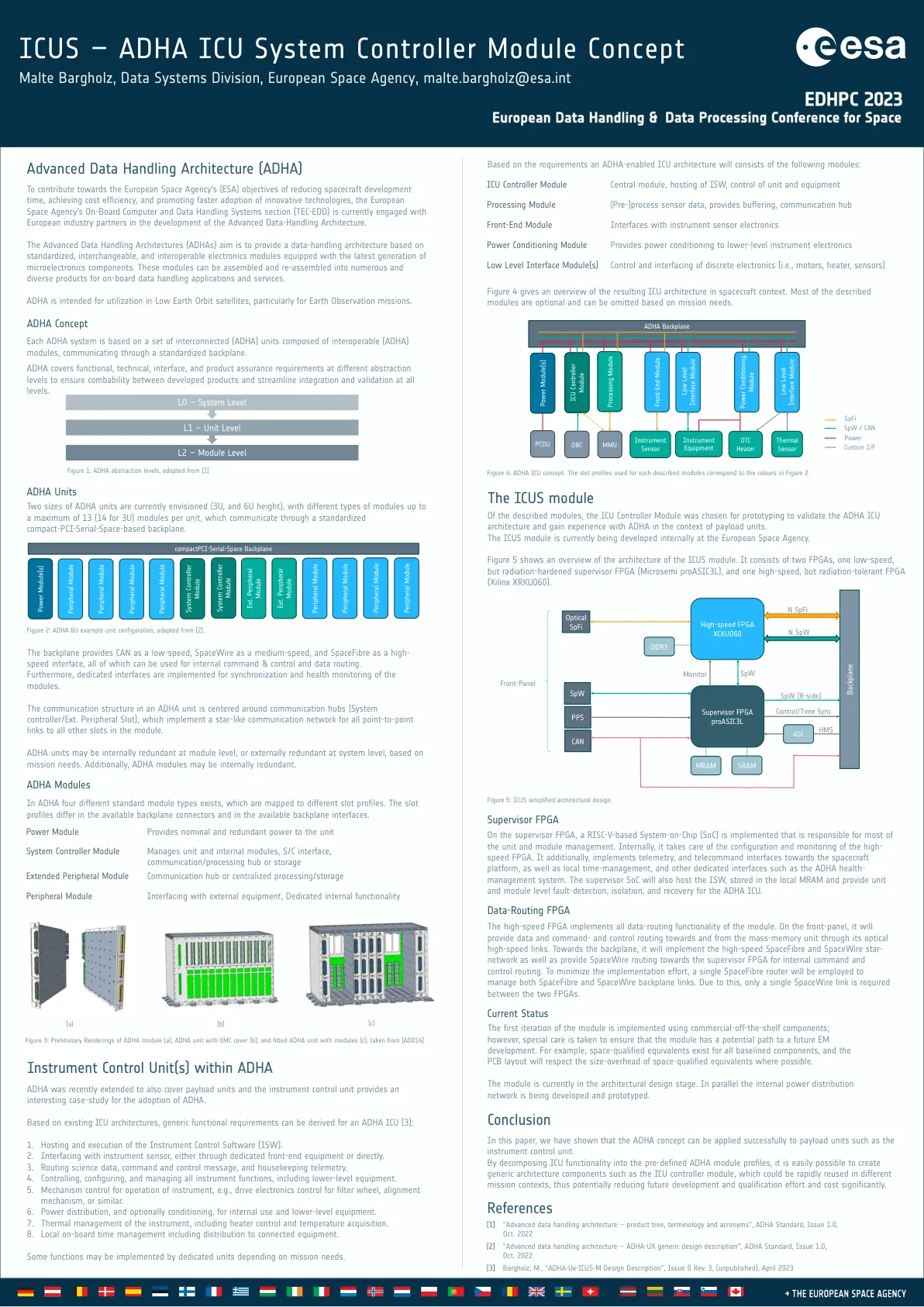

高速FPGA实现了模块的所有数据路由功能。在前面板上,它将通过其光学高速链接向大众内存单元提供数据以及命令和控制路由。朝向背板,它将实现高速太空固定和SpaceWire Star-Network,并为Supervisor FPGA提供空间线路路由,以进行内部命令和控制路由。为了最大程度地减少实施工作,将采用单个太空路由器来管理太空空间和太空线路背板链接。因此,两个FPGA之间只需要一个空格线链接。

使用量子随机存储内存和...

简介。作为物理和计算机科学领域的前沿主题,量子信息科学通常是一个迅速发展且价值高度的研究领域,在计算中广泛应用[1-4],数据科学和机器学习[5,6],通信[7-13]和Sensing [14 - 16]。在不久的将来,量子组合可能会给某些特定算法带来重要的优势。量子通信将严格构成数据安全性和隐私性,根据物理定律提高传输效率;量子传感可能会显着提高测量精度。量子数据的产生,处理和应用以及这些数据的处理以及其经典同行目前正在挑战量子科学中的口头和实验性问题。在本文中,我们提出了所谓的量子数据中心(QDC)的概念,这是一个统一的概念,指的是某些特定的量子硬件,可以有效地处理量子数据,并将提供经典数据和量子处理器之间的效率界面。提出的QDC的关键组件是量子随机存储器(QRAM)[17-25],该设备允许用户从数据库中访问叠加中的多个不同元素(可以是经典或量子)。至少,QDC由QRAM组成,该QRAM耦合到量子网络。我们构建了与原始应用相关的QDC理论。我们提出了示例的明确构造,包括:QDC作为易于故障的量子计算中数据查找的实现; QDC作为所谓的多方私人Quantum沟通的介体(下面定义),该通信结合了量子私人查询(QPQ)[26]和量子

MAD:加速全同态加密的内存感知设计技术

云计算使个人和公司更容易获得大型计算和内存资源。然而,它也引发了人们对用户与远程云服务器共享的数据的隐私担忧。全同态加密 (FHE) 通过对加密数据进行计算为该问题提供了解决方案。不幸的是,所有已知的 FHE 构造都需要一个噪声项来确保安全,而且这种噪声在计算过程中会增加。要对加密数据执行无限制计算,我们需要执行一个称为引导的定期降噪步骤。此引导操作受内存限制,因为它需要几 GB 的数据。与未加密数据相比,这导致操作加密数据所需的时间增加了几个数量级。在这项工作中,我们首先对 CKKS FHE 方案中的引导操作进行了深入分析。与其他现有工作类似,我们观察到 CKKS 引导表现出较低的算术强度(<1 Op/byte)。然后,我们提出了内存感知设计 (MAD) 技术来加速 CKKS FHE 方案的引导操作。我们提出的 MAD 技术与底层计算平台无关,可以同样应用于 GPU、CPU、FPGA 和 ASIC。我们的 MAD 技术利用了几种缓存优化,可以实现最大限度的数据重用并执行操作的重新排序,以减少需要传输到/从主存储器的数据量。此外,我们的 MAD 技术包括几种算法优化,可减少数据访问模式切换的次数和昂贵的 NTT 操作。将我们的 MAD 优化应用于 FHE 可将引导算法强度提高 3 × 。对于逻辑回归 (LR) 训练,通过利用我们的 MAD 优化,现有的 GPU 设计可以在相同的片上内存大小下获得高达 3.5 × 的性能提升。类似地,现有的 ASIC 设计在 LR 训练和 ResNet-20 推理方面分别可获得高达 27 倍和 57 倍的性能提升,

对内存系统实际处理的机器学习培训的实验评估

摘要 - 大约三分之一的2型糖尿病患者(T2D)升级为基础胰岛素注射。基底胰岛素剂量被滴定以实现一个不高血糖风险的严重血糖靶标。在护理标准(SOC)中,滴定基于间歇性禁食血糖(FBG)的调查。缺乏依从性和FBG测量中的日常变异性是现有胰岛素滴定程序的限制因素。我们提出了一种自适应退化的地平线控制策略,其中识别出葡萄糖 - 胰岛素空腹模型并用于预测最佳的基础胰岛素剂量。使用新的UVA虚拟实验室(UVLAB)评估了该算法在Silico实验中评估,并与一组与临床数据相匹配的T2D头像(NCT01336023)。与SOC相比,我们表明,这种控制策略可以更快地实现相同的葡萄糖靶标(在第8周时)和更安全(低血糖保护和对缺失FBG测量的鲁棒性)。Specifically, when insulin is titrated daily, a time-in-range (TIR, 70–180 mg/dL) of 71.4 ± 20.0% can be achieved at week 8 and maintained at week 52 (72.6 ± 19.6%) without an increased hypoglycemia risk as measured by time under 70 mg/dL (TBR, week 8: 1.3 ± 1.9% and week 52: 1.2与SOC相比(第8:59.3±28.0%和周的TIR相比,±1.9%)。这种方法可以潜在地减少治疗惯量和处方复杂性,从而改善使用基底胰岛素注射的T2D血糖结果。

内存受限量子路径上的启发式远程纠缠分布算法

摘要 —远程纠缠分布在大规模量子网络中起着至关重要的作用,而实现纠缠分布的关键因素是能够延长纠缠传输距离的量子路由器(或中继器)。但量子路由器的性能还远未完善,其中量子路由器中有限的量子存储器极大地影响了纠缠分布的速率和效率。为了克服这一挑战,本文提出了一种在存储器受限路径上最大化纠缠分布速率(EDR)的新模型,然后将其转化为纠缠生成和交换子问题。我们提出了一种用于短距离纠缠生成的贪婪算法,以便高效利用量子存储器。对于纠缠交换子问题,我们使用纠缠图(EG)对其进行建模,其解被发现至少是 NP 完全的。在此基础上,我们提出了一种启发式算法,将原始EG划分为多个子问题,每个子问题都可以在多项式时间内使用动态规划(DP)进行求解。通过进行模拟,结果表明我们提出的方案可以实现较高的EDR,并且所开发的算法具有多项式时间上界和合理的平均运行时间复杂度。

基于具有高内存能力的串联耦合微孔谐振器

摘要:已经提出了片上微区谐振器(MRR)来构建时间延迟的储层计算(RC),该计算提供了有希望的配置,可用于具有高扩展性,高密度计算和易于制造的计算。但是,单个MRR不足以为具有多种内存要求的计算任务提供足够的内存。MRR通过光学反馈波导满足了巨大的记忆需求,但以其较大的足迹为代价。在结构中,超长的光学反馈波导实质上限制了可扩展的光子RC集成设计。在本文中,提出了一个时间删除的RC,该RC是通过利用基于硅的非线性MRR与一系列线性MRRS结合使用的。这些线性MRR具有高质量的因素,为整个系统提供了足够的存储能力。我们在具有多种内存要求的三个经典任务上进行定量分析和评估拟议的RC结构的性能,即Narma 10,Mackey-Glass和Santa Fe Chaiotial Chaotion Chaoticerseries的预测任务。在处理NARMA 10任务时,提出的系统具有超长的基于波导的系统,具有与MRR相当的性能,这需要大量的内存能力。尽管如此,与具有基于光反馈波导的系统的MRR中超长的反馈波导相比,这些线性MRR的总长度明显小于三个数量级。这种结构的紧凑性对光子RC的可伸缩性和无缝整合具有重要意义。

HZO-LNOI集成的铁电气调节器和内存的首次演示以启用可重新配置的光子系统Zefeng Zefeng Xu 1,2,6†

†同等贡献;电子邮件:aaron.thean@nus.edu.sg摘要 - 我们首次成功证明了创新的后端(beol)兼容的电磁调节器和内存(Eomm)基于niobate基于绝缘体(LNOI)的niobate(lnoi)Micro-Ring Rings Resonator(MRR)的5 ZRRING 0. ZRRICTRRICRICRICRICRICRICRICTRRICRICTRICTRICTRICRICRICTRRICRICTRICRICRICTRICTRICTRICTRICTRICRICRONE (HZO)非挥发性模拟记忆。高的非易失性记忆和调制性能都在单个紧凑型装置中实现,高灭绝比为13.3 dB,出色的效率为66 pm/v,稳定的九态开关,创纪录的耐力超过10 9个循环。这是通过利用LNOI中的Pockels效应来实现的,这是由残留的HZO铁电偏振的电场效应引起的。我们研究了由Eomm和Hybrid热光调制的Eomm启用的可重新配置的Chiplet-interposer光子互连的系统实现。我们的模型显示出与常规电气插座互连相比,潜在的70%能效提高。我们还测试了Eomm与Poet Technologies的400G TX/RX光学插入器芯片的集成,并研究了Eomm设备的有限规模演示。

用于边缘 AI 加速的无溢出计算内存

图3.逐层 CNN 量化策略概述。虽然可以进行进一步的优化操作 (a),但选择对 MAC 周期数减少影响最大的操作并将其应用于模型 (b)。然后,再训练阶段将补偿由于 IMO 或 BO 的位宽减少而导致的准确度下降 (c)。如果违反了准确度约束 (d),则恢复先前的配置 (e),并从候选优化列表中删除当前操作 (f)。