XiaoMi-AI文件搜索系统

World File Search System具有改进的新型晶圆级粘合剂键合...

我们报告了一种通用方法,用于提高软烤 BCB 键合堆栈中键合后晶圆对准精度和 BCB 厚度均匀性。该方法基于新型 BCB 微柱,在键合过程中充当锚点。锚点结构成为键合界面的自然组成部分,因此对键合堆栈的光学、电气和机械性能的干扰最小。我们研究了固定锚点密度和各种锚点高度与粘合剂 BCB 厚度的关系,这些性能也不同。我们证明了对准精度可以提高大约一个数量级,并且该工具可以接近基本的键合前对准精度。我们还证明了该技术对 2 – 16 μ m 的大范围 BCB 厚度都有效。此外,我们观察到,对于 8 – 16 μ m 范围内的 BCB 厚度,厚度不均匀性降低了 2 – 3 倍。

以金属有机骨架为填充物的逆向混合键合

图 29 (a) 每个 I/O 电阻测量的开尔文结构;(b) 键合铜柱的 SEM 横截面 ......................................................................................................... 44 图 30 带 Ru 封盖的 Cu-Cu 键合测试台 ............................................................................. 45 图 31 铜上钌的沉积过程 ............................................................................................. 45 图 32 30 分钟 FGA(合成气体退火)退火后表面 Cu 和 Ru 的百分比 [98] ............................................................................................................. 46 图 33 450°C FGA 退火后,带有针孔的 Ru 表面上的扩散 Cu ............................................................................. 47 图 34 用于研究填充的测试台制造流程 ......................................................................................... 49 (b) 使用 Keyence 7000 显微镜对集成结构进行的顶视图,描绘了顶部芯片上的通孔密度 ............................................................................................................................. 50 图 36 (a) 200 次循环氧化铝 ALD 后扫描 EDX 映射区域的 SEM 图像;(b) 集成结构的顶视图,突出显示了填充覆盖研究区域;(c) EDX 映射结果描绘了铝和氧 pe 的区域 ............................................................................................................................. 51 图 37 200 次循环氧化铝 ALD 后脱粘底部芯片的 FIB 横截面描绘 ............................................................................................................................. 52 图 38 (a) 200 次循环真空清除 ALD 后 EDX 研究的不同区域 - 底部芯片正下方通孔区域(区域 A)、距最近通孔 300 µm 的区域(区域 B)、靠近边缘的区域(区域 C); (b) 三个 r 中的 Al/Si 比率 ...................................................................................................................................... 52 图 39 (a) 集成结构的对角线切割;(b) 描绘平滑填充区域和无填充的受损区域后集成结构横截面的近视图;(c) 描绘填充高达 300 µm 的横截面的未放大图像 ............................................................................................. 54 图 40 (a) ZIF-8 MOF 化学和结构;(b) 示意图表示 ALD ZnO 和转化为气相沉积 MOF,体积膨胀和间隙填充约为 10-15 倍。 ........................................................................................................................................... 56 图 41 在完全填充芯片到基板间隙后,距离最近通孔 300 µm 的集成结构横截面的 EDX 映射.............................................................................57 图 42 横截面的 SEM 图像显示抛光模具未渗透到通孔和芯片与基板的间隙中,从而使上述结果可信 ............................................................................................. 58 图 43 (a) 测试台示意图,顶部芯片具有通孔 Cu-Cu 键合到底部基板;(b) Cu-Cu 键合测试结构的 SEM 横截面(面 A);(c) 键合前顶部芯片表面的铜垫/柱(面 B);(d) 键合前底部芯片表面的带有金属走线的铜柱(面 C) ............................................................................................................................. 59 图 44 20 nm ZnO ALD 后脱键合的底部芯片概览;(b) 通孔下方未沉积填充的区域 ............................................................................................................. 60 图 45 顶部芯片靠近通孔的区域,显示扩散半径为 (a) 572 µm,通孔直径为 240 µm; (b) 75 µm 直径通孔的 364 µm .............................................................. 61 图 46 20 nm ZnO ALD 后的脱粘底部芯片概览,a) 脉冲时间 250 ms 和温度 150°C;(b) 脉冲时间 1 秒和温度 150°C ................................................................................ 62 图 47 反向混合键合的工艺顺序 ............................................................................................. 63 图 48 (a) 1 个 MOF 循环后脱粘底部芯片的概览;(b) 在底部芯片中间观察到的 MOF 晶粒表明已完全渗透............................................................................................................. 64 图 49 靠近底部基板中心的 FIB 横截面,如预期的那样,显示了 500 nm MOF ............................................................................................................................................. 65 图 50 (a) 5 个 MOF 填充循环后脱粘底部芯片的概览;(b)62 图 47 反向混合键合的工艺顺序 .......................................................................................... 63 图 48 (a) 经过 1 个 MOF 循环后,脱键合底部芯片的概览;(b) 在底部芯片中间观察到的 MOF 晶粒表示完全渗透............................................................................. 64 图 49 靠近底部基板中心的 FIB 横截面,如预期的那样显示了 500 nm MOF ............................................................................................................................. 65 图 50 (a) 经过 5 个 MOF 填充循环后,脱键合底部芯片的概览;(b)62 图 47 反向混合键合的工艺顺序 .......................................................................................... 63 图 48 (a) 经过 1 个 MOF 循环后,脱键合底部芯片的概览;(b) 在底部芯片中间观察到的 MOF 晶粒表示完全渗透............................................................................. 64 图 49 靠近底部基板中心的 FIB 横截面,如预期的那样显示了 500 nm MOF ............................................................................................................................. 65 图 50 (a) 经过 5 个 MOF 填充循环后,脱键合底部芯片的概览;(b)

混合晶圆键合中的 CMP 挑战回顾...

ST Microelectronics 和 LETI:S. Lhostis、A. Farcy、E. Deloffre、F. Lorut 等人在拉斯维加斯电子元件和技术会议 ECTC 上发表演讲(2016 年)。

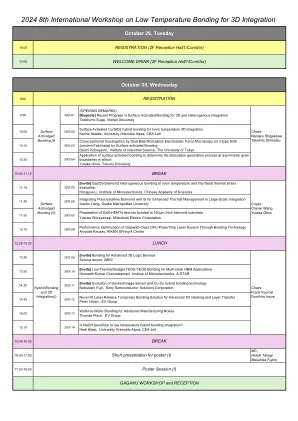

2024 第八届三维集成低温键合国际研讨会

基于晶圆键合与智能切割技术的功能化GaN异质集成衬底 丁家欣,中国科学院上海微系统与信息技术研究所集成电路材料国家重点实验室

半导体晶圆键合:科学、技术与应用 17

T. Wernicke、B. Rebhan、V. Vuorinen、M. Paulasto-Krockel、V. Dubey、K. Diex、D. Wünsch、M. Baum、M. Wiemer、S. Tanaka、J. Froemel、KE Aasmundtveit、HV Nguyen、V. Dragoi

键和与与之相关的键 - ...

GST的结论标志着巴黎野心周期中的关键点。作为当事方采取国内缓解措施的义务的一部分,其目的是实现其NDC,23每五年进行一次NDC 24(在COP30 25之前的下一个9-12个月)进行NDC进行交流,并确保每个连续的NDC“反映其最高的野心”,26党也必须提供重要信息。正如Katowice在Katowice的COP中规定的那样,当事方应提供特定的信息,以实现“清晰,透过的和理解和理解” 27和“有关如何通过[GST]的结果告知其[NDCS]的准备信息。” 28商品及服务税的结果,包括其关键政策信号,必须通过其NDC来告知当事方的实施工作。要求各国在2025年第一季度提交的新NDC必须包括有关当事方对这些信号采取行动的信息。到2025年,COP28对气候行动的影响的程度将成为重点。

用于热粘合应用应用的优化的模具键合设置

热键合(TSB)是一种模具到die的键合方法,它在粘结过程中将新型的热压缩键合与超声波(美国)焊接结合在一起,因此,在微电子粘结应用中使用了每种质量的最佳质量。最初,TSB主要用于电线键合技术[1]。我们引入的引入通过降低在半导体制造中非常有吸引力的施加的粘结压力和温度来增强键合过程。Flip-Chip键合是针对区域阵列连接的一种无焊的模具到die键合技术(图1)。该方法用于将ICS底部的一系列金色凸起(图2)连接到基板上的镀金垫上。通常使用热压缩键合法[2],这是一个简单,干净且干燥的组装过程。纯热压缩键合通常需要> 300°C的界面温度[2,3]。此温度会损坏包装材料,层压板和一些敏感的微芯片[4]。这种下一个级别的键合解决方案在翻转芯片键合中非常有利,因为界面温度和粘结力通常可以低得多。分别在100至160°C和20和50g/ bump之间[2]。

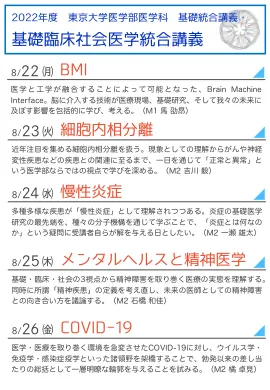

基础临床社会医学统合讲义

09:00-09:50 Tadaki(国家传染病研究所)感染性病理学对Covid-19的贡献10:00-10:00-10:50 Yamazaki Akira(大阪大学)(大阪大学)细胞介导的免疫反应对SARS-COV2 11:00-11:00-11:00-11:00-11:50 ARASE NAO(OSAKA NAO)介绍了OSAKA NAO(OSAKA NAO),以下简13:00-13:50 Nishiura Hiroshi(京都大学)Covid -19的传染病流行病学194:00-14:50 Sato Yoshi(Tokyo)新颖的Coronavirus大学的演变15:00-15:00-15:50-15:50

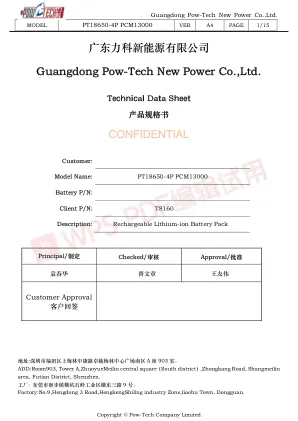

广东力科新能源有限公司Guangdong Pow-Tech New Power ...

Constant current 0.2C charge to FC Voltage, then constant voltage FC Voltage charge to current declines to 0.02C, rest for 10min, constant current 0.2C discharge to 2.8V, rest for 10min. Repeat above steps till continuously discharge capacity higher than 80% of the initial capacity of the battery. 电池以0.2C 充饱,静置10 分钟,然后以0.2C 放空, 静置10 分钟。重复以上充放电循环直至放电容量低于初 始容量的80%。

明确的键/安全键/受保护的键启动techDocid

摘要:从Z10 Microcode的最新更新开始,以及ICSF,FMID HCR7770,IBM加密硬件的新支持,支持三种键。本文介绍了清晰键,安全键和受保护的键之间的基本差异,并且是对硬件如何为安全键提供额外保护的介绍。了解这三个区域之间的差异将有助于设计正确的加密解决方案并确定加密工作的硬件要求。加密是为了保护数据的过程。使用加密算法(一系列步骤)将数据拼写,该算法由密钥控制。键是输入算法的二进制数字序列。加密的安全性依赖于保持密钥的价值为秘密。在密码学中,必须确保所有对称密钥和公共/私钥对的私钥以保护数据。对于对称键,需要保护钥匙值,以便只有两个交换加密数据的双方才能知道键的值。DES,TDE和AES算法已发布,因此键提供了安全性,而不是算法。如果第三方可以访问密钥,则可以像预期的接收者一样轻松地恢复数据。对于非对称键,必须保护私钥,以便只有公共/私钥对的所有者才能访问该私钥。公共密钥可以并且将与将向键盘所有者发送加密数据的合作伙伴共享。安全的密钥硬件要求加载主密钥。在系统z加密环境中定义键为安全键时,该密钥将由另一个称为主键的密钥保护。IBM安全密钥硬件提供篡改感应和篡改响应环境,在攻击时,将对硬件进行归零并防止钥匙值受到损害。该主密钥存储在安全硬件中,用于保护操作密钥。硬件内(通过随机数生成器函数)生成安全密钥的清晰值,并在主密钥下进行加密。当安全密钥必须离开安全的硬件边界(要存储在数据集中)时,将密钥在主密钥下进行加密。因此,加密值存储,而不是密钥的清晰值。一段时间后,当需要恢复数据(解密)时,安全的键值将加载到安全的硬件中,在该硬件中将从主密钥中解密。然后将在安全硬件内使用原始键值,以解密数据。如果安全密钥存储在CKD中,并且主密钥更改,ICSF提供了重新启动安全键的能力;那就是将其从原始的主密钥中解密,然后在新的主密钥下重新加密它,所有这些都在安全硬件中,然后将其存储回新的CKD,现在与新的主密钥值相关联。当需要与合作伙伴共享时,也可以在密钥加密密钥或运输密钥下加密安全密钥。在这种情况下,当它留下硬件的安全边界时,它将在传输密钥(而不是主密钥)下进行加密。