XiaoMi-AI文件搜索系统

World File Search System各种低功耗 VLSI 设计的实现......

摘要 :在当今的电子工业中,低功耗已成为一个主要问题。对于 VLSI 芯片的设计,功耗与性能和面积同等重要。由于技术的复杂性和规模的缩小,最小化功耗和片上的整体电源管理是 100nm 以下的主要难点。由于需要降低封装成本并延长电池寿命,因此电源优化对许多系统至关重要。在低功耗 VLSI 设计中,漏电流对电源管理也有显著影响。漏电流在集成电路总功耗中的比例越来越大。本文讨论了低功耗电路和系统的各种电源管理方法、方法和策略。同时还提到了设计低功耗、高性能电路的潜在障碍。

低功耗静态随机存取存储器的回顾(...

摘要 — 物联网 (IoT) 设备对低功耗静态随机存取存储器 (SRAM) 单元的需求不断增长,这导致了各种 SRAM 单元拓扑的开发,这些拓扑可在保持性能和稳定性的同时最大限度地降低功耗。在本文中,我们基于不同的参数(例如功耗、延迟、面积、能量和稳定性)分析了各种 SRAM 设计。据观察,由六个晶体管组成的 6T SRAM 单元由于其简单性和低面积要求而成为使用最广泛的拓扑。然而,已经开发出更大的单元,例如 8T、9T 和 10T,以提高稳定性并降低功耗,尽管它们需要更多的面积。据观察,8T 在读取延迟方面效果更好,而 9T 在 9 方面效果更好。将 SRAM 单元缩小到更小的特征尺寸在保持稳定性和可靠性的同时最大限度地降低功耗方面提出了挑战。

技术文档:低功耗蓝牙 5.0

5.0 版低功耗蓝牙是蓝牙规范的一个子集。当前版本是 BLE 5.3,但本文档将考虑 BLE 5.0,因为自 5.0 版以来,在 SECUR 用例方面没有引入任何重大改进。5.0 版发布于 2016 年 12 月。最近的版本包括一些对安全应用有用但不是强制性的功能。例如: - 测向(修订版 5.1),即到达角和出发角 - 任意通道索引(5.1),使广告商能够选择要宣传的渠道和顺序。例如,广告商可以使用随机通道序列来减少发生碰撞的机会。 - 将次要广告渠道归类为不良渠道(5.1)。在 5.1 中,分类是集中完成的。在 5.3 中,外围设备也可以参与。 - LE 功率控制(5.1)。发射器可以调整发射功率。接收器可以请求发射器调整发射功率。 - 增强属性协议(5.2)。属性协议的升级,支持 BLE 应用程序和 BLE 主机之间的并发事务。 - 等时通道 (5.2)。适用于时间敏感传输(例如高质量音频),以及多个接收器上的同步传输。 - 冗余数据包 (5.3)。允许接收器的控制器识别和丢弃冗余数据包。本文档重点介绍低功耗蓝牙 (BLE) 版本 5.1、5.2 和 5.3 的广告模式,这些版本的发布日期分别为 2019 年 1 月、2019 年 12 月和 2021 年 1 月。

超低功耗电子器件:TFET 和 NEM 器件

学士:首尔国立大学电子工程学士 (1996 - 2000) 硕士:首尔国立大学电子工程学士 (2000 - 2002) 博士:首尔国立大学电子工程学士 (2002 - 2006) 工作经历

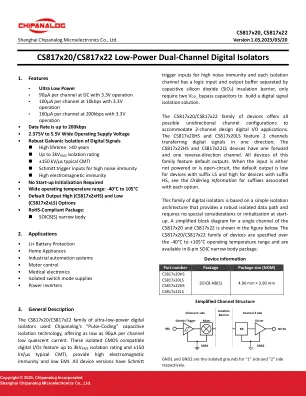

CS817x20/CS817x22 低功耗双通道数字隔离器

触发输入可实现高抗噪性,并且每个隔离通道都有一个由电容性二氧化硅 (SiO 2 ) 绝缘屏障隔开的逻辑输入和输出缓冲器,因此只需要两个 V DD_ 旁路电容即可构建数字信号隔离解决方案。CS817x20/CS817x22 系列器件提供所有可能的单向通道配置,以适应 2 通道设计数字 I/O 应用。CS817x20HS 和 CS817x20LS 具有 2 个通道,可在一个方向上传输数字信号;CS817x22HS 和 CS817x22LS 器件具有一个正向通道和一个反向通道。该系列的所有器件均具有默认输出。当输入未通电或开路时,后缀为 LS 的器件的默认输出为低,后缀为 HS 的器件的默认输出为高,有关每个选项相关后缀的信息,请参阅订购信息。该系列数字隔离器基于简单的隔离架构,可提供可靠的隔离数据路径,启动时无需特殊考虑或初始化。下图显示了 CS817x20 和 CS817x22 单通道的简化框图。CS817x20/CS817x22 系列器件的额定工作温度范围为 -40°C 至 +105°C,采用 8 引脚 SOIC 窄体封装。

TMP117 高精度、低功耗、数字温度传感器,带 SMBus™ 和 I2C 兼容接口数据表 (Rev. D)

6.1 绝对最大额定值 ...................................................... 5 6.2 ESD 额定值 .............................................................. 5 6.3 建议工作条件 .............................................................. 5 6.4 热信息 ...................................................................... 5 6.5 电气特性 ...................................................................... 6 6.6 开关特性 ...................................................................... 7 6.7 双线接口时序 ............................................................. 7 6.8 时序图 ...................................................................... 8 6.9 典型特性 ...................................................................... 8

研究论文 新型超低功耗镜像折叠级联跨阻放大器

背景和目标:本文首次设计并介绍了一种基于电流镜和折叠级联拓扑组合的新型折叠镜 (FM) 跨阻放大器 (TIA) 结构。跨阻放大器级是接收器系统中最关键的构建块。这种新型拓扑基于电流镜拓扑和折叠级联拓扑的组合,采用有源元件设计。其理念是在输入节点使用电流镜拓扑。在所提出的电路中,与许多其他已报道的设计不同,信号电流(而不是电压)被放大直到到达输出节点。由于使用二极管连接的晶体管作为电流镜拓扑的一部分,所提出的 TIA 具有低输入电阻的优势,这有助于隔离主要输入电容。因此,以相当低的功耗实现了 5Gbps 的数据速率。此外,设计的电路仅使用了六个有源元件,占用的芯片面积很小,同时提供 40.6dBΩ 的跨阻抗增益、3.55GHz 频率带宽和 664nArms 输入参考噪声,并且仅消耗 315µW 功率和 1V 电源。结果证明了所提出的电路结构作为低功耗 TIA 级的正确性能。方法:所提出的拓扑基于电流镜拓扑和折叠级联拓扑的组合。使用 Hspice 软件中的 90nm CMOS 技术参数模拟了所提出的折叠镜 TIA 的电路性能。此外,对晶体管的宽度和长度尺寸进行了 200 次蒙特卡罗分析,以分析制造工艺。结果:所提出的 FM TIA 电路提供 40.6dBΩ 跨阻增益和 3.55GHz 频率带宽,同时使用 1V 电源仅消耗 315µW 功率。此外,由于分析通信应用中接收器电路中输出信号的质量至关重要,所提出的 FM TIA 对于 50µA 输入信号的眼图打开约 5mV,而对于 100µA 输入信号,眼图垂直打开约 10mV。因此,可以清楚地显示眼图的垂直和水平开口。此外,跨阻增益的蒙特卡罗分析呈现正态分布,平均值为 40.6dBΩ,标准差为 0.4dBΩ。此外,FM TIA 的输入电阻值在低频时等于 84.4Ω,在 -3dB 频率时达到 75Ω。通过对反馈网络对输入电阻的影响的分析,得出了在没有反馈网络的情况下,输入电阻可达1.4MΩ,由此可见反馈网络的存在对于实现宽带系统的重要性。结论:本文本文介绍了一种基于电流镜拓扑和折叠级联拓扑组合的跨阻放大器,该放大器可放大电流信号并将其转换为输出节点的电压。由于输入节点存在二极管连接的晶体管,因此 TIA 的输入电阻相对较小。此外,六个晶体管中有四个是 PMOS 晶体管,与 NMOS 晶体管相比,它们的热噪声较小。此外,由于前馈网络中未使用无源元件,因此所提出的折叠镜拓扑占用的片上面积相对较小。使用 90nm CMOS 技术参数的结果显示,跨阻增益为 40.6dBΩ,频率带宽为 3.55GHz,输入参考噪声为 664nArms,使用 1 伏电源时功耗仅为 315µW,这表明所提出的电路作为低功耗构建块的性能良好。

CMOS 电路的功耗

在本章中,我们将解释互补金属氧化物半导体 (CMOS) 电路中的两种功耗类型。一般而言,CMOS 电路在任何时候都会耗散功率 — 无论是活动状态还是非活动状态。电路在执行计算任务时消耗的功率称为动态功率。相反,在电路处于休眠状态期间由于漏电而损失的功率称为静态功率。通过精心设计电路,可以将漏电抑制到最低限度。因此,动态功耗通常明显高于静态功耗。可以采用的一些节省动态功耗的技术包括降低电源电压、时钟频率、时钟功率和动态有效电容。通过探究设计模块的活动因素,可以将这些技术应用于高功耗模块。

– 定义可再生和可持续的太阳能光伏和存储解决方案,以确保持续供电,同时降低设施功耗

爱德华七世国王高中 (KES) 和爱德华七世国王预科学校 (KEPS) 在此邀请合格的供应商/安装商提交对能源存储和能源消耗减少技术的设计、供应、安装和维护的兴趣表达,包括但不限于:• 单个较小的混合逆变器或较大的集中式逆变器存储(电池)备用系统,用于关键

低功耗机电除冰系统设计

提供有效的保护,但需要大量的电力或维护。此外,在更多电动飞机的背景下,依赖热力发动机的系统可能会过时,从而为新的电气系统开辟道路。机电除霜系统最近已被证明在能源消耗和车载质量方面具有相关性,这解释了本文继续开发该系统的工作。本论文重点研究基于新型执行器结构或架构的谐振机电除霜系统的设计。所研究的谐振机电除霜系统基于压电执行器。由交流电供电,压电陶瓷通过以给定频率激励结构来振动。当它对应于结构的固有频率之一时,由于共振现象,振动幅度会增加,产生高电平