XiaoMi-AI文件搜索系统

World File Search System30 ~ 40V 系列N-沟道JSFET 具业界领先水平的RON,sp

30V 器件的低 R DS(ON) 和 Qg 可在各种最终产品中的典型 DC/DC 降压和/或升压转换中实现高功率效率。它们是:PC 和图形主板、计算机外围设备、工业计算、电池供电的电动工具、家庭自动化、消费者生活方式的个人电器、无人驾驶飞行器、电池管理系统 (BMS) 等。低 V GS(th)_Typ @ 1.7V 与典型的基于 MCU 的嵌入式控制器兼容。图 1 和图 2 说明了降压转换和直流电机驱动的典型应用电路。图 3 所示的双 N 配置使 40V 器件(例如 JMSL0406AGD)特别适用于流行的快速充电器中的 V BUS 切换,该充电器具有两个输出端子:一个是 USB Type-C,另一个是 USB Type-A。

32款车规级40〜150V n-jsfet®

这40〜150V SGT MOSFET非常适合汽车内部的应用。根据AEC-Q101质量标准对其长期可靠性进行了测试。JMSL0406AGQ及其双DIE变体JMSL0406AGDQ在车身控制模块(BCM)中很受欢迎,例如低功率DC电动机驾驶。r ds(on)降至13m,JMSH041AGQ适合中/高功率直流电动机的功率效率要求。典型的应用是:多路电动座椅,电源后挡板,集中式门锁,ESC(电子稳定控制)。在V ds_max = 100V处,并在低调的PDFN5x5-8L软件包中组装,JMSL1018AGQ非常适合在信息娱乐/ADAS单元的平板显示器显示中LED背光。相比之下,JMSL1020AGDQ同时在较大面板中同时驱动两个高亮度LED。

基于沟道的FinFET温度特性...

本文介绍了 FinFET 的温度灵敏度以及基于晶体管 Fin 宽度将 FinFET 用作温度纳米传感器的可能性。使用多栅极场效应晶体管 (MuGFET) 仿真工具来检查温度对 FinFET 特性的影响。首先模拟了不同温度和通道 Fin 宽度 (WF = 5、10、20、40 和 80 nm) 下的电流-电压特性,本研究采用了二极管模式连接。在工作电压 V DD 为 0–5 V 时,在最大 ∆I 下,FinFET 具有最佳温度灵敏度。根据结果,温度灵敏度随通道 Fin 宽度 (5-80 nm) 的整个范围线性增加,此外,较低的栅极 Fin 宽度 (WF =5nm) 可以在较低的工作电压 (V DD =1.25 V) 下实现更高的灵敏度。

P 沟道增强型 MOSFET

常州银河世纪微电子有限公司(GME)保留对本文中任何产品信息(版权所有)进行更正、修改、改进或其他更改的权利,恕不另行通知。GME 不承担因应用或使用本文所述任何产品而产生的任何责任;也不转让其专利权或他人权利下的任何许可。

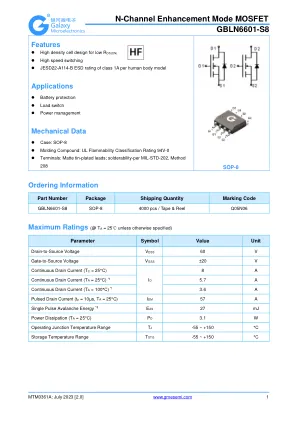

GBLN6601-S8 N 沟道增强型 MOSFET

常州银河世纪微电子有限公司(GME)保留对本文中任何产品信息(版权所有)进行更正、修改、改进或其他更改的权利,恕不另行通知。GME 不承担因本文所述任何产品的应用或使用而产生的任何责任;也不转让其专利权或他人权利下的任何许可。

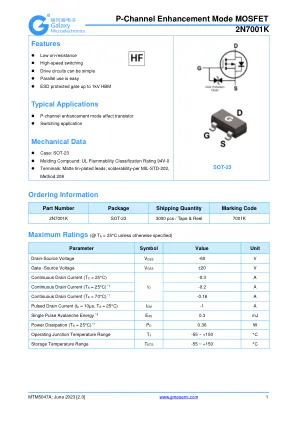

2N7001K P 沟道增强型 MOSFET

常州银河世纪微电子有限公司(GME)保留对本文中任何产品信息(版权所有)进行更正、修改、改进或其他更改的权利,恕不另行通知。GME 不承担因本文所述任何产品的应用或使用而产生的任何责任;也不转让其专利权或他人权利下的任何许可。

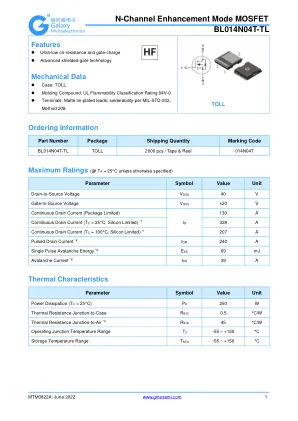

BL014N04T-TL N 沟道增强型 MOSFET

常州银河世纪微电子有限公司(GME)保留对本文中任何产品信息(版权所有)进行更正、修改、改进或其他更改的权利,恕不另行通知。GME 不承担因应用或使用本文所述任何产品而产生的任何责任;也不转让其专利权或他人权利下的任何许可。

BL8810-6L N 沟道增强型 MOSFET

常州银河世纪微电子有限公司(GME)保留对本文中任何产品信息(版权所有)进行更正、修改、改进或其他更改的权利,恕不另行通知。GME 不承担因应用或使用本文所述任何产品而产生的任何责任;也不转让其专利权或他人权利下的任何许可。

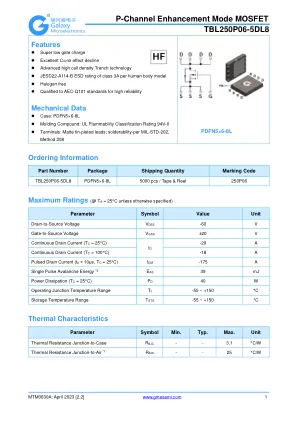

TBL250P06-5DL8 P 沟道增强型 MOSFET

常州银河世纪微电子有限公司(GME)保留对本文中任何产品信息(版权所有)进行更正、修改、改进或其他更改的权利,恕不另行通知。GME 不承担因本文所述任何产品的应用或使用而产生的任何责任;也不转让其专利权或他人权利下的任何许可。

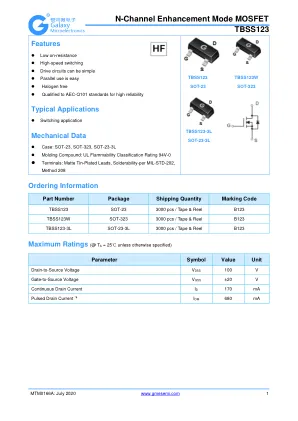

TBSS123 N 沟道增强型 MOSFET

常州银河世纪微电子有限公司(GME)保留对本文中任何产品信息(版权所有)进行更正、修改、改进或其他更改的权利,恕不另行通知。GME 不承担因应用或使用本文所述任何产品而产生的任何责任;也不转让其专利权或他人权利下的任何许可。