XiaoMi-AI文件搜索系统

World File Search System流水线式忆阻神经网络模数转换器

摘要——随着高速、高精度、低功耗混合信号系统的出现,对精确、快速、节能的模数转换器 (ADC) 和数模转换器 (DAC) 的需求日益增长。不幸的是,随着 CMOS 技术的缩小,现代 ADC 在速度、功率和精度之间进行权衡。最近,已经提出了四位 ADC/DAC 的忆阻神经形态架构。可以使用机器学习算法实时训练此类转换器,以突破速度-功率-精度权衡,同时优化不同应用的转换性能。然而,将此类架构扩展到四位以上具有挑战性。本文提出了一种基于四位转换器流水线的可扩展模块化神经网络 ADC 架构,保留了其在应用重新配置、失配自校准、噪声容忍和功率优化方面的固有优势,同时以延迟为代价接近更高的分辨率和吞吐量。 SPICE 评估表明,8 位流水线 ADC 可实现 0.18 LSB INL、0.20 LSB DNL、7.6 ENOB 和 0.97 fJ/conv FOM。这项工作朝着实现大规模神经形态数据转换器迈出了重要一步。

结合刺激与双模电荷平衡和时域流水线记录的 CMOS BD-BCI

基于皮层脑电图 (ECoG) 的双向脑机接口 (BD-BCI) 引起了越来越多的关注,因为:(1) 需要同时进行刺激和记录以恢复人类的感觉运动功能 [1] 和 (2) 良好的空间分辨率和信号保真度以及临床实用性。在刺激方面,这种 BD-BCI 可能需要 >10mA 的双相电流来引发人工感觉,以及 >20V 的电压顺应性以适应各种生物阻抗 [1]。两个刺激相之间的电荷不匹配会导致电压积累,从而造成电极腐蚀和组织损伤。现有的电荷平衡 (CB) 技术,例如电荷包注入 (CPI) [2] 和基于时间的电荷平衡 (TCB) [1],会在脉冲间隔内产生 CB 电流,导致不必要的二次感觉和过度的刺激伪影 (SA)。对于记录,低输入参考噪声 (IRN) 是获取小神经信号 (NS) 所必需的,而大动态范围 (DR) 则是容纳大 SA 所必需的。现有的记录系统采用 SAR [1] 或连续时间 delta-sigma (CT-ΔΣ) [3] ADC(图 4)。前者由于 DAC 不匹配而具有有限的 DR,而后者则受到环路延迟内大幅度尖锐 SA 引起的失真的影响。尽管在 [4] 中,ΔΣ-ADC 的采样频率会自适应地变化以适应 SA,但所需的稳定时间很长。为了解决上述问题,本文提出了一种基于 ECoG 的 BD-BCI,其中包括:(1) 具有双模基于时间的电荷平衡 (DTCB) 的高压 (HV) 刺激系统和 (2) 高动态范围 (HDR) 时域流水线神经采集 (TPNA) 系统。图 1 描绘了所提出的 BD-BCI。刺激系统包括 4 个刺激器,每个刺激器包括一个 8 位分段电流控制 DAC 和一个 HV 输出驱动器,用于生成刺激脉冲。为了执行 CB,每个刺激器都采用具有 2 种模式的 DTCB 环路,即无伪影 (AL) TCB 和脉冲间有界 (IB) TCB 模式。3 阶 II 型 PLL 为基于时间的量化创建所需的时钟。记录系统有 4 个通道,每个通道都采用低增益模拟前端 (LG-AFE)、HDR 电压时间转换器 (VTC)、两步流水线 (TSP) TDC 和一个数字核心,其中操作模式由状态机控制。受 [1] 的启发,所提出的 DTCB 的工作原理如图 2 所示。AL-TCB 监测电极电压 V ESn -V CM (1≤n≤N;此处,N=4)并调整后续刺激脉冲的幅度而不产生额外的 SA,而当 |V ESn -V CM | 过大而需要立即去除电荷时,IB-TCB 在下一个刺激脉冲之前完成 CB。在第一个 T CC 开始时,如果 |V ESn - V CM |≤V TH,AL (V TH,AL 是标志着需要立即去除电荷的过电位阈值),则 AL-TCB 导通,并且 V ESn - V CM 在第一个 T CC 周期内由 VTC 和 TDC 数字化。然后将数字数据 D TDCn 馈送到通道间干扰消除 (ICIC) 模块,该模块可补偿由于多极刺激导致的通道间干扰 (ICI) 引入的电压误差。接下来,数字直流增益增强器 (DDGB) 有助于提高 CB 精度,而不会降低 AL-TCB 环路稳定性。为了执行 CB,AL-TCB 的电流(例如,I AL-Cn )(其大小由 DDGB 输出 D ALn 控制)被添加到后续刺激电流中以调整其大小。相反,仅当 |V ESn -V CM |>V TH,AL 时,IB-TCB 才会开启并在一个 T IP 内的几个 T CC 中执行 CB,直到 |V ESn - V CM |

高级计算机架构

• 理解计算机体系结构的高级硬件和软件问题 • 理解多处理器体系结构和连接机制 • 理解多处理器内存管理 模块 I:(10 小时)微处理器和微控制器、RISC 和 CISC 体系结构、并行性、流水线基础、算术和指令流水线、流水线风险、超标量体系结构、超级流水线体系结构、VLIW 体系结构、SPARC 和 ARM 处理器。 模块 II:(10 小时)基本多处理器架构:Flynn 分类、UMA、NUMA、分布式内存架构、阵列处理器、矢量处理器。 模块 III:(10 小时)互连网络:静态网络、网络拓扑、动态网络、云计算。 模块 IV(10 小时)内存技术:缓存、缓存内存映射策略、缓存更新方案、虚拟内存、页面替换技术、I/O 子系统。 结果

m.tech.(全日制)计算机科学与工程...

4. 学习多线程和数据流架构。 第一单元 - 并行处理简介(12 小时) 基本概念 – 并行的类型和级别 - 并行架构的分类 – 基本并行技术 - 共享内存多处理器 – 分布式内存多计算机 – 并行随机存取机 – VLSI 复杂度模型。 第二单元 - 处理器和内存层次结构(12 小时) 先进的处理器技术 – 超标量和矢量处理器 – 内存层次结构技术、虚拟内存技术 – 高速缓存内存组织 – 共享 – 内存组织。第三单元 — 流水线和超标量技术(12 小时) 线性流水线处理器 — 非线性流水线处理器 — 指令流水线设计 — 算术流水线设计 — 超标量流水线设计 第四单元 — 并行和可扩展架构(12 小时) 缓存一致性和同步机制 — 一致性问题 — 监听总线和基于目录的协议 — 矢量处理原理 矢量指令类型 — 矢量访问内存方案 — SIMD 计算机组织 — 实施模型 — CM2 — 架构延迟隐藏技术

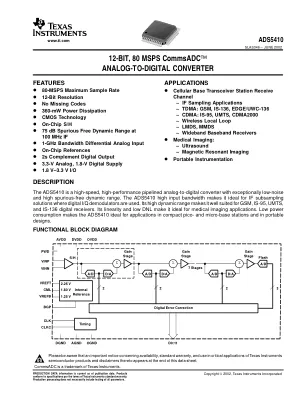

12 位、80 MSPS CommsADC? 模数转换器数据表

ADS5410 是一款 12 位 ADC。其低功耗(360 mW)和 80 Msps 的高采样率是通过使用基于先进低压 CMOS 工艺构建的先进开关电容流水线架构实现的。ADS5410 模拟核心主要采用 3.3 V 电源供电,消耗大部分电量。数字核心采用 1.8 V 电源供电。如果设计中没有 1.8 V 电源,则可以使用 TPS76318 从 3.3 V AVDD 电源获取 1.8 V。为了增加接口灵活性,数字输出电源 (OV DD ) 可以设置为 1.6 V 至 3.6 V。ADC 核心由 10 个流水线级和一个闪存 ADC 组成。每个级产生 1.5 位。上升时钟沿和下降时钟沿都用于每半个时钟将样本通过流水线传输一次,总共六个时钟周期。

加州大学伯克利分校

摘要 构建可用的量子计算机的关键在于构建可扩展、可延伸且提供实时响应的经典控制硬件流水线。该流水线的控制处理器部分提供在高级量子编程语言和使用任意波形发生器的低级脉冲生成之间进行映射的功能。在本文中,我们讨论了设计替代方案,重点是支持具有 O(10 2)量子比特的中型量子设备。我们介绍了一种评估量子 ISA 编码量子电路的有效性的方法。我们使用这种方法来评估几个设计点:类 RISC、向量和类 VLIW。我们提出了两种对广泛使用的开放 RISC-V ISA 的量子扩展。鉴于量子硬件流水线的变化速度很快,我们的开源实现为设计空间实验提供了一个良好的起点,同时我们的指标可以独立用于指导设计决策。

使用对比后 T1 加权图像结合基于云的 3D 卷积神经网络开发全自动胶质瘤分级流程

摘要:胶质瘤是最常见的脑肿瘤类型,其等级影响其治疗政策和预后。因此,人们已经研究了基于人工智能的肿瘤分级方法。然而,在大多数研究中,都进行了二维(2D)分析和手动肿瘤区域提取。此外,使用医学图像的深度学习研究在收集图像数据和准备硬件方面遇到困难,从而阻碍了其广泛使用。因此,我们开发了一个 3D 卷积神经网络 (3D CNN) 流水线,通过使用 NVIDIA 提供的预训练 Clara 分割模型和我们原始的分类模型,实现全自动胶质瘤分级系统。在该方法中,使用 Clara 分割模型提取脑肿瘤区域,并将使用该提取区域创建的感兴趣体积 (VOI) 分配给分级 3D CNN 并分类为 II、III 或 IV 级。通过使用 46 个区域进行评估,所有肿瘤的分级准确率为 91.3%,与使用多序列的方法相当。提出的流水线方案可以通过结合预训练的 3D CNN 和我们原来的 3D CNN 在单个序列中创建全自动胶质瘤分级流水线。

详细课程大纲两年制研究生学位课程(...

模块 I 制造系统- 组件和分类、制造系统中的自动化、原理和策略、数学模型、成本。单站制造单元。自动化流水线:工件运输转移方法、机械缓冲存储控制功能、设计和制造考虑。[10] 模块 II 自动化流水线分析:无缓冲存储和有缓冲存储的传输线的一般术语和分析、部分自动化、自动化流水线的实施。装配系统和生产线平衡:装配过程和系统装配线、生产线平衡方法、改善生产线平衡的方法、柔性装配线。[12] 模块 III 自动化物料处理:设备类型、功能、物料处理系统、输送系统、自动导引车系统的分析和设计。自动化存储系统、自动化存储和检索系统;在制品存储、处理和存储与制造的接口。[10] 模块 IV 成组技术- 零件分类和编码、计算机辅助工艺规划 (CAPP) - 检索和生成型工艺规划系统。 [08] 教科书:1.自动化、生产系统和计算机集成制造 - MP Groover,PHI。

适用于企业工作负载的实时 AI:IBM Telum 处理器

带有 SMT2 的 5+ GHz 无序流水线 重新设计的分支预测 – 集成的 1 级和 2 级 BTB – 动态 BTB 条目重新配置 – 最多 >270k 个分支目标表条目