XiaoMi-AI文件搜索系统

World File Search SystemEE 370A 数字电子学 2021-22-I

和稳健性、功率和能量、速度。隔离反相器:不同的反相器实现、MOSFET 作为开关、CMOS 反相器、CMOS 反相器的静态和动态行为、性能指标、设计视角:反相器链分析和缩放影响。组合电路:涉及静态 CMOS 设计、比率逻辑设计、传输晶体管设计和动态逻辑设计的设计指南和权衡。顺序电路设计:静态时序分析 (STA),双稳态电路:静态和动态锁存器和寄存器、流水线和非双稳态顺序电路。基于阵列的逻辑设计:现场可编程门阵列 (FPGA)。CMOS 存储器设计:存储器层次结构和组织、外围电路、静态随机存取存储器 (SRAM) 设计、动态 RAM (DRAM) 设计。向上移动层次结构:系统级设计、数据路径和寄存器传输操作。硬件描述语言 (HDL) 简介。寄存器传输级 (RTL) 到 GDSII 流程(行业专家讲座)。

前向前向算法:一些初步研究

本文旨在介绍一种新的神经网络学习程序,并证明它在一些小问题上效果很好,值得认真研究。前向-前向算法用两个前向传递取代了反向传播的前向和后向传递,一个使用正(即真实)数据,另一个使用网络本身可以生成的负数据。每一层都有自己的目标函数,即对正数据具有高优度,对负数据具有低优度。层中活动的平方和可以用作优度,但还有许多其他可能性,包括减去活动的平方和。如果正传递和负传递可以在时间上分开,那么负传递就可以离线完成,这使得正传递中的学习变得更加简单,并且允许视频通过网络进行流水线传输,而无需存储活动或停止传播导数。

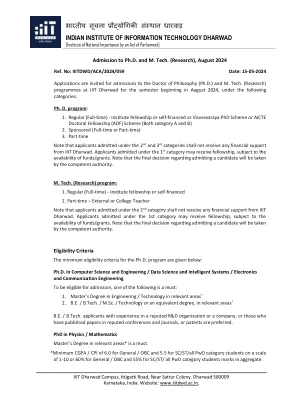

印度信息技术学院达尔瓦德印度信息技术学院...

电子与通信工程节点和网格分析、叠加、戴维南定理、诺顿定理、线性电路(RL、RC、RLC)的时间和频域分析连续时间信号:傅里叶级数和傅里叶变换、线性时不变系统:属性、因果关系、稳定性、卷积、频率响应二极管电路:削波、钳位、整流器、BJT 和 MOSFET 放大器:偏置、小信号分析、运算放大器电路:放大器、微分器、积分器、有源滤波器、振荡器、数字表示:二进制、整数、浮点数、组合电路:布尔代数、逻辑门、序贯电路:锁存器、触发器、计数器、数据转换器:采样和保持电路、ADC、DAC、机器指令和寻址模式、算术逻辑单元(ALU)、数据路径、控制单元、指令流水线、反馈原理、传递函数、框图表示、信号流图、数字调制方案:ASK、PSK、FSK、QAM、带宽和通信系统。

基于注意力的神经网络信息提取策略的比较研究

摘要。本文重点研究历史手写结婚记录中的信息提取。传统方法依赖于两个连续任务的顺序流水线:在命名实体识别之前应用手写识别。最近,人们研究了同时处理这两个任务的联合方法,并取得了最先进的成果。然而,由于这些方法已在不同的实验条件下使用,因此尚未对它们进行公平比较。在这项工作中,我们对基于相同基于注意的架构的顺序和联合方法进行了比较研究,以量化可归因于联合学习策略的收益。我们还研究了三种基于多任务或多尺度学习的新联合学习配置。我们的研究表明,依靠联合学习策略可以使完整识别分数提高 8%。我们还强调了多任务学习的兴趣,并展示了基于注意的网络对信息提取的好处。我们的工作在 Esposalles 数据库上的 ICDAR 2017 信息提取竞赛中以行级实现了最先进的性能,无需任何语言建模或后处理。

计算最坏情况执行时间... - AbsInt

以前,处理器的行为非常确定。指令的延迟是一个常数,即它不依赖于执行该指令之前发生的事情。内部指令(add、mul 或等)以及访问内存或 IO 等外部设备的指令都是如此。为了提高其平均计算能力,现代处理器配备了加速机制,导致指令的执行时间各不相同。因此,指令的持续时间取决于在它之前执行的内容。这种“历史影响”可能非常深远,并且与它影响的指令没有逻辑相关性。这种机制的一个例子是缓存。事实上,根据通向加载指令的执行路径,包含要加载的数据的内存行可能已经在数据缓存中(命中),也可能不在,要么尚未加载(未命中),要么已经删除(由于替换而未命中)。还有许多其他加速机制,如乱序执行、分支预测、推测访问、“超标量”、处理单元复制(例如两个整数单元)、存储缓冲区、地址流水线等。

基于算法的平台经济

过去十年,平台经济,又称“零工经济”或“共享经济”,在大多数发达国家和发展中国家迅速发展。平台是一种数字化基础设施,使客户、劳动者以及服务或产品的提供者能够互动,从而促进经济活动[1]。受工作类型和类别的限制,一些平台任务只能在本地交付,并依赖于劳动力的物理流动性,例如外卖配送;而一些平台任务可以远程分发,无论工人身在何处,包括各种数字化服务[2]。与流水线或建筑工地上繁重的制造工作相比,在平台上工作的劳动者在一定程度上享有更多的自主权和自由裁量权,因为他们不再时刻受到人类主管的管教[2]。然而,现有的各种文献表明,平台经济中的劳动者仅仅享有有限的自由,因为平台公司操纵的算法更隐蔽地控制着员工的行为和绩效。尽管平台经济的剥削性特征受到越来越多的审视,但现有学术界对算法控制和管理的批评仍占主导地位。因此,平台劳动者被视为被动的

RISC-V 工具链和基于敏捷开发的开放...

本文提出了一种低功耗神经形态处理器——文曲星 22A,它将通用 CPU 功能与 SNN 相结合,利用 RISC-V SNN 扩展指令对其进行高效计算。文曲星 22A 的主要思想是将 SNN 计算单元集成到通用 CPU 的流水线中,利用定制的 RISC-V SNN 指令 1.0(RV-SNN 1.0)、精简泄漏积分和发射 (LIF) 模型和二元随机脉冲时序相关塑性 (STDP) 实现低功耗计算。文曲星 22A 的源代码已在 Gitee 1 和 GitHub 1 上在线发布。我们将文曲星 22A 应用于 MNIST 数据集的识别,以与其他 SNN 系统进行比较。实验结果表明,文曲星22A相比加速器解决方案ODIN能耗降低了5.13倍,3位ODIN在线学习的分类准确率约为85.00%,1位文曲星22A的分类准确率约为91.91%。

65nm ASIC 中 SABER 的设计空间探索

本文介绍了 SABER 的设计空间探索,SABER 是 NIST 量子抗性公钥加密标准化工作中的最终入围者之一。我们的设计空间探索针对 65nm ASIC 平台,并已对 6 种不同的架构进行了评估。我们的探索从设置从 FPGA 移植的基线架构开始。为了提高时钟频率(我们探索的主要目标),我们采用了几种优化:(i)以“智能合成”方式使用编译内存,(ii)流水线,以及(iii)SABER 构建块之间的逻辑共享。最优化的架构利用了四个寄存器文件,实现了 1 的惊人时钟频率,而仅需要 0.314 平方英寸的面积。此外,还对该架构进行了物理综合,并提出了可用于流片的布局。高频架构的估计动态功耗约为 184mW(密钥生成)和 187mW(封装或解封装操作)。这些结果有力地表明,我们优化的加速器架构非常适合高速加密应用。

通过 FPGA 实现数字图像处理算法的开发

实时图像处理是实现 IR 4.0 的基本要素之一。数字图像处理技术的快速发展使得医疗保健、交通运输和制造业等领域的各种应用成为可能。人们正在寻求更高性能的图像处理,因为传统的图像处理已不再满足需求。基于 FPGA 的数字图像处理已成为公众的选择之一,因为它具有并行流水线功能,可以缩短处理时间并提高性能。该项目开发了几种数字图像处理算法,包括灰度变换、亮度控制、对比度调整、阈值和反转。它们是数字图像处理中最流行的算法。使用 Microsoft Paint 将彩色输入图像的格式转换为位图格式,然后使用 MATLAB 将其转换为十六进制文件,以便在 FPGA 中读取和写入。使用 ModelSim Altera 和 Intel Quartus II 等平台为数字图像处理算法编写 Verilog HDL。结果,从模拟中获得了五个十六进制文件。输出的十六进制文件在 MATLAB 中进一步处理以生成相应的图像。

通过电路特性了解量子控制处理器的能力和局限性

摘要 — 量子计算机的持续扩展取决于构建可扩展、可延伸且提供实时响应的经典控制硬件流水线。控制处理器的指令集架构 (ISA) 提供功能抽象,将量子编程语言的高级语义映射到硬件的低级脉冲生成。在本文中,我们提供了一种方法来定量评估 ISA 对具有 O(102) 量子比特的中型量子设备的量子电路编码的有效性。我们定义的表征模型反映了性能、满足时间约束影响的能力、未来量子芯片的可扩展性以及其他重要考虑因素,使它们成为未来设计的有用指南。使用我们的方法,我们提出了标量 (QUASAR) 和矢量 (qV) 量子 ISA 作为扩展,并将它们与其他 ISA 在电路编码效率、满足量子芯片实时门周期要求的能力以及扩展到更多量子比特的能力等指标上进行了比较。索引词——量子控制处理器、ISA 扩展、RISC-V、量子电路表征、专门架构。