机构名称:

¥ 1.0

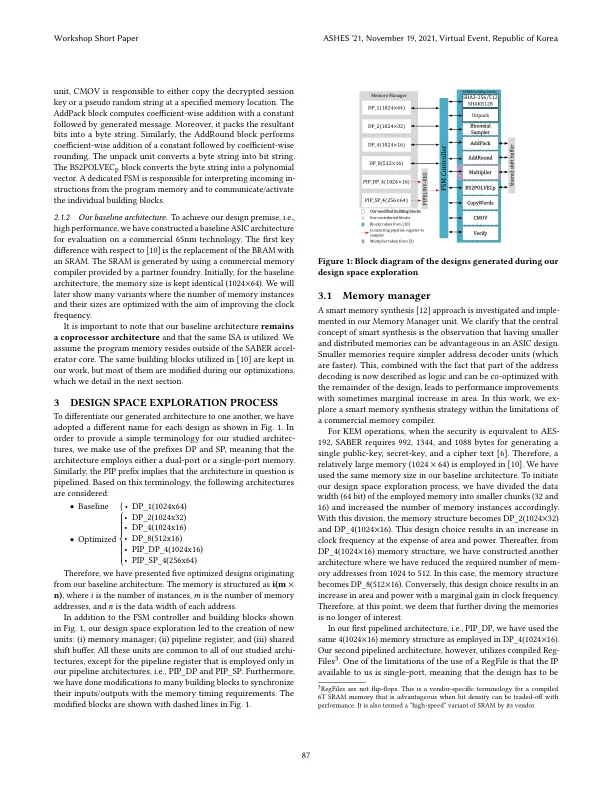

本文介绍了 SABER 的设计空间探索,SABER 是 NIST 量子抗性公钥加密标准化工作中的最终入围者之一。我们的设计空间探索针对 65nm ASIC 平台,并已对 6 种不同的架构进行了评估。我们的探索从设置从 FPGA 移植的基线架构开始。为了提高时钟频率(我们探索的主要目标),我们采用了几种优化:(i)以“智能合成”方式使用编译内存,(ii)流水线,以及(iii)SABER 构建块之间的逻辑共享。最优化的架构利用了四个寄存器文件,实现了 1 的惊人时钟频率,而仅需要 0.314 平方英寸的面积。此外,还对该架构进行了物理综合,并提出了可用于流片的布局。高频架构的估计动态功耗约为 184mW(密钥生成)和 187mW(封装或解封装操作)。这些结果有力地表明,我们优化的加速器架构非常适合高速加密应用。

65nm ASIC 中 SABER 的设计空间探索

主要关键词