机构名称:

¥ 1.0

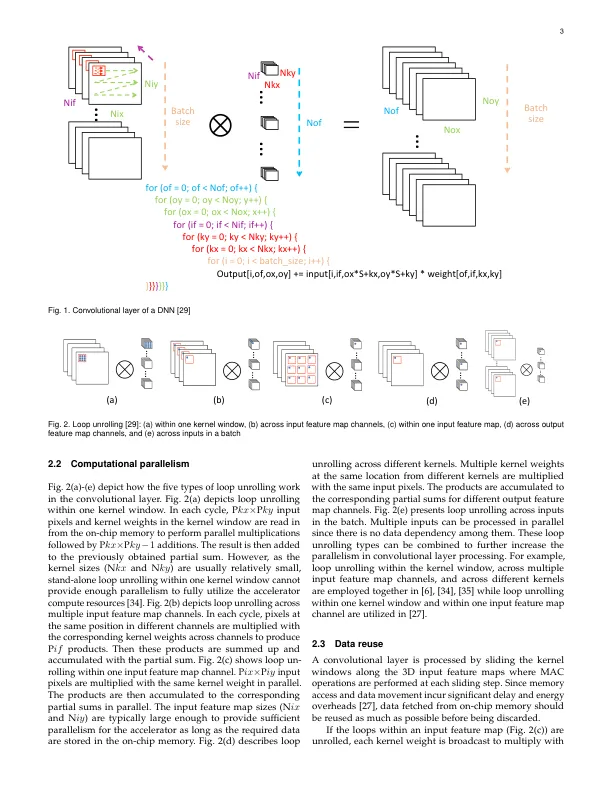

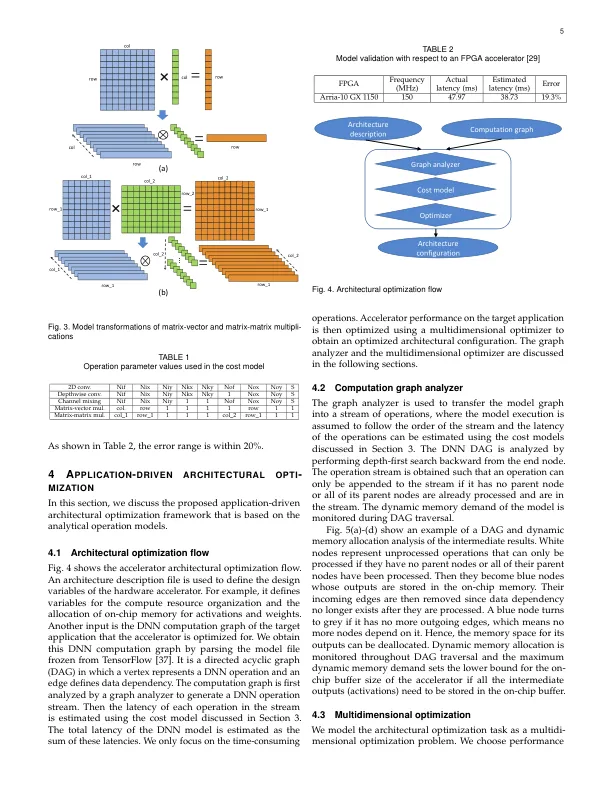

摘要 — 深度神经网络 (DNN) 已被证明在图像识别、物体检测、机器人技术和自然语言处理等广泛应用中均优于传统机器学习算法。然而,DNN 的高计算复杂度通常需要极其快速和高效的硬件。随着神经网络规模呈指数级增长,问题变得更加严重。因此,已经开发了定制的硬件加速器来加速 DNN 处理而不牺牲模型准确性。然而,以前的加速器设计研究没有充分考虑目标应用程序的特点,这可能导致架构设计次优。另一方面,已经开发了新的 DNN 模型以提高准确性,但它们与底层硬件加速器的兼容性往往被忽视。在本文中,我们提出了一个应用驱动的框架,用于探索 DNN 加速器的架构设计空间。该框架基于单个 DNN 操作的硬件分析模型。它将加速器设计任务建模为一个多维优化问题。我们证明它可以有效地用于应用驱动的加速器架构设计:我们使用该框架优化八个代表性 DNN 的加速器配置,并选择具有最高几何平均性能的配置。相对于仅针对每个 DNN 优化的架构配置,所选 DNN 配置的几何平均性能改进范围为 12.0% 至 117.9%。给定一个目标 DNN,该框架可以生成具有优化性能和面积的高效加速器设计解决方案。此外,我们探索了在同时使用多种 DNN 应用的情况下使用该框架进行加速器配置优化的机会。该框架还能够改进神经网络模型,以最适合底层硬件资源。我们证明它可用于分析目标 DNN 的操作与相应加速器配置之间的关系,在此基础上可以调整 DNN 以在给定加速器上获得更好的处理效率,而不会牺牲准确性。

软件定义设计空间探索,实现高效...

主要关键词