XiaoMi-AI文件搜索系统

World File Search System量子编译器中的操作计划

I。尽管量子计算设备技术中的快速进展已大大增加了量子位(或量子位)的相干时间,但当前可用的量子计算机仍在所谓的嘈杂的中间尺度量子量子制度中[1]。对于嘈杂的量子计算机,重要的是要在Qubits上安排操作尽可能短,因为这增加了在任何量子装置之前完成所有操作的概率,从而获得了具有较高有限性的计算结果。即使对于容忍故障的量子计算机,缩短编译时间表的持续时间也会增加吞吐量。量子计算机(或量子编译器)的编译器采用量子电路,该电路是一系列量子操作,作为输入程序,并生成可在目标硬件上可执行的相应控制指令的顺序。例如,在使用超导码位的量子计算机的情况下,将量子操作汇编为多个控件(例如,微波脉冲),可以在一定时间段内进行。通常,任何给定的量子操作都有其自身的处理时间,并且在该持续时间内作为计算资源占据其代理量子。出于这个原因,调度,通过该调度在没有任何重叠的情况下确定每个量子操作的执行启动时间,是量子编译器中必不可少的任务。我们称此任务量子操作计划。在本文中,我们的目标是最大程度地减少总体执行时间。在跨多个资源(Qubits,对于量子操作计划的情况下)的调度任务的上下文中,第一个任务开始与

使用图形编译器和容器优化 AI 训练部署

摘要 — 基于深度神经网络 (DNN) 或深度学习 (DL) 的人工智能 (AI) 应用因其在解决图像分析和语音识别等问题方面的成功而变得流行。训练 DNN 需要大量计算,而高性能计算 (HPC) 一直是 AI 发展的关键驱动力。虚拟化和容器技术促成了云和 HPC 基础设施的融合。这些具有不同硬件的基础设施增加了部署和优化 AI 训练工作负载的复杂性。可以使用特定于目标的库、图形编译器以及通过改进数据移动或 IO 来优化 HPC 或云中的 AI 训练部署。图形编译器旨在通过为目标硬件/后端生成优化代码来优化 DNN 图的执行。作为 SODALITE(Horizon 2020 项目)的一部分,MODAK 工具旨在优化软件定义基础设施中的应用程序部署。 MODAK 使用数据科学家的输入和性能建模,将最佳应用程序参数映射到目标基础架构并构建优化的容器。在本文中,我们介绍了 MODAK,并回顾了 AI 的容器技术和图形编译器。我们说明了使用图形编译器和 Singularity 容器优化 AI 训练部署。使用 MNIST-CNN 和 ResNet50 训练工作负载的评估表明,定制的优化容器优于 DockerHub 的官方映像。我们还发现图形编译器的性能取决于目标硬件和神经网络的复杂性。索引术语 —MODAK、SODALITE、HPC、云、性能优化、AI 训练、Singularity 容器、图形编译器

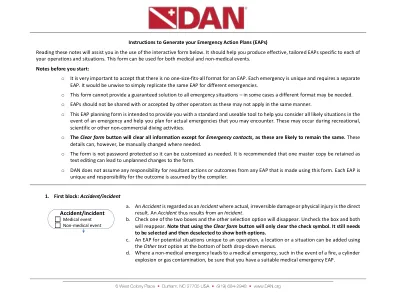

编译an-Exrengency-action-plan.pdf

a。事故被认为是实际,不可逆转的损害或身体伤害的事件。因此,事故是由于事件而造成的。b。检查两个框之一,另一个选择选项将消失。取消选中盒子,两个都将重新出现。请注意,使用“清除表单”按钮只会清除检查符号。仍然需要选择它,然后取消选择以显示这两个选项。c。可以使用两个下拉菜单底部的其他文本选项添加操作,位置或情况的潜在情况的EAP。d。如果非医学紧急情况导致医疗紧急情况,例如发生火灾,气缸爆炸或气体污染,请确保您拥有合适的医疗紧急EAP。

论文:一种用于量子程序的开源、工业强度优化编译器

嘈杂的中型量子 (NISQ) 计算机是一个活跃的研究领域。新的量子计算机架构有时是制造过程逐步改进的结果,有时是量子比特技术本身的范式转变。虽然每种新架构在计算意义上都是通用的,但它们设计的无常性挑战了人们为它们编写软件的能力。与传统计算机的情况一样,编译器的作用是减轻这一挑战。量子计算机的软件最好以对程序员来说最简单、最直接的方式编写,而不一定需要了解目标架构的细节。然后,编译器的工作就是生成该软件的有效且适当的表达,该表达考虑到目标架构的细节。在本文中,我们介绍了 Quilc,这是一个开源 4 软件应用程序,用于将用 Quil [ 3 , 24 ] 编写的量子程序编译为优化程序,该程序以目标量子计算机架构的本机操作表示。 Quilc 不需要(实际上也没有办法接受)用户关于细粒度编译策略的指令。相反,它使用 Quilc 必须为其编译用户程序的体系结构的简单描述。体系结构描述语言足够通用,可以处理迄今为止大多数制造的基于门的计算机体系结构,并且可以预测新的体系结构。出于这些原因,我们说 Quilc 是自动的和可重定向的。Quilc 不仅仅是一个桌面计算器(避免进行手动重复计算的便利),因为它充当了有关程序编译的知识库,并且能够综合这些信息来发现量子程序的非平凡表达式。我们在第 5 节中提供了这方面的示例。它也是生产级的,并且是 Rigetti Computing 软件堆栈的重要组成部分。本文的结构如下。首先,在第 2 节中,我们概述了 Quilc,包括与编译有关的量子架构的数学公式。第 3 节使用此形式来描述 Quilc 如何实现可重定向性,其高级概述见

更新的基于 LLVM 的量子研究编译器,具有进一步的 OpenQASM 支持

摘要 量子计算是一个快速发展的领域,有可能改变我们解决以前棘手问题的方式。新兴硬件的复杂性正在逼近,需要越来越复杂的编程和控制。Scaffold 是一种较旧的量子编程语言,最初设计用于未来大型量子机器的资源估算,而 ScaffCC 是相应的基于 LLVM 的编译器。我们首次对该语言本身、编译器及其传递结构进行了全面而完整的概述。尽管 Abhari 等人(2015 Parallel Comput. 45 2–17)、Abhari 等人(2012 Scaffold:量子编程语言 https://cs.princeton.edu/research/techreps/TR-934-12)的先前研究对该工具链的不同部分进行了零碎的描述,但我们在本文中提供了更全面、更完整的描述。我们还引入了 ScaffCC 的更新,包括旨在与现代量子汇编语言保持同步的条件测量和多维量子比特阵列,以及旨在保持噪声中型量子 (NISQ) 机器的正确性和低资源计数的替代工具链,以及与当前版本的 LLVM 和 Clang 的兼容性。我们的目标是为研究界提供一个功能齐全的 LLVM 框架,用于量子程序分析、优化和可执行代码的生成。

适用于 PIC32M MCU 的 MPLAB XC32 C/C++ 编译器用户指南

23.1. 概述................................................................................................................................................215 23.2. 翻译....................................................................................................................................215 23.3. 环境....................................................................................................................................215 23.4. 标识符....................................................................................................................................216 23.5. 字符....................................................................................................................................216 23.6. 整数.......................................................................................................................................217 23.7. 浮点数....................................................................................................................................217 23.8. 数组和指针....................................................................................................................................218 23.9. 提示....................................................................................................................................219 23.10. 结构、联合、枚举和位字段.............................................................................................219 23.11. 23.12. 限定符................................................................................................................................220 23.13. 声明符.................................................................................................................................220 23.14. 语句.................................................................................................................................220 23.14. 预处理指令.......................................................................................................................220 23.15. 库函数.................................................................................................................................221 23.16. 架构.................................................................................................................................225

量子电路的高效正确编译

摘要 — 量子算法的高级描述不考虑物理硬件的限制。因此,在量子计算机上实际执行量子电路形式的算法需要首先针对所需的目标架构对其进行编译。量子电路的编译依赖于有效的方法,才能适用于除琐碎实例之外的所有实例。为此,过去曾引入过不同的编译方法,但仍有改进的空间。此外,仅有高效的编译过程本身是不够的——生成的电路也必须正确。在这篇总结论文中,我们回顾了如何利用启发式搜索算法或精确推理引擎来优化现有的编译方法。此外,我们回顾了如何通过巧妙的数据结构(如决策图)来验证所获得结果的正确性。这说明了编译流程的核心步骤,该流程可以为许多实例生成最小或接近最小的结果,此外,还保证了整个过程的正确性。

图着色量子算法的编译规划

摘要。最近,编译通用量子算法以便在近期量子处理器上实现的问题已被引入人工智能社区。先前的研究表明,时间规划是此编译任务的一部分的一种有吸引力的方法,具体而言,是在量子处理器架构上应用于 MaxCut 问题的量子交替算子拟定 (QAOA) 的电路的路由。在本文中,我们将早期的工作扩展到实现图着色问题 QAOA 的电路的路由。着色的 QAOA 需要在芯片上执行更多、更复杂的操作,这使得路由成为一个更具挑战性的问题。我们在领先的量子计算公司最先进的硬件架构上评估了该方法。此外,我们还研究了将规划方法应用于量子位初始化和路由。我们的实证评估表明,时间规划与合理的分析上限 [20] 相比效果良好,并且使用经典规划器解决量子比特初始化通常有助于时间规划器找到用于图着色的 QAOA 的更短完成时间编译。这些进展表明,时间规划可以成为更复杂的量子计算算法和架构的有效方法。

GM—CSF与DNA疫苗研究进展·综述与编译·

[16]歌曲R,I,IU S,Adams rj,Et A1.Enhancing H1V GAG DNA疫苗通过GM的局部交付-CSF JN MU RJNE和MA-

用于多种目标的P4编译器

T4P4S - P4开关的翻译器开源(在GitHub上)P4-14语言支持(P4-16即将推出)支持多个目标(硬件独立核心 +网络硬件抽象图书馆)英特尔(DPDK)的Nethals(DPDK)(DPDK),Freescale(odp sdk),OpenWrt(odp sdk),本机,…<