机构名称:

¥ 1.0

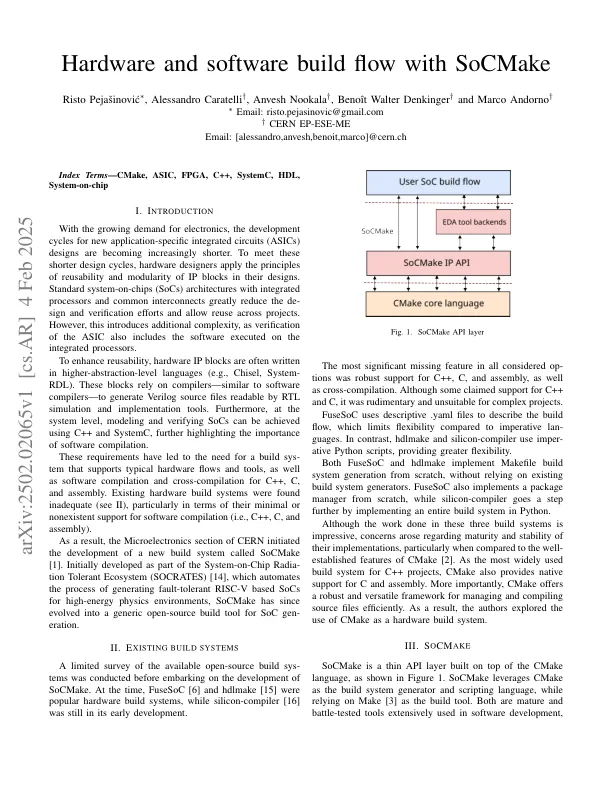

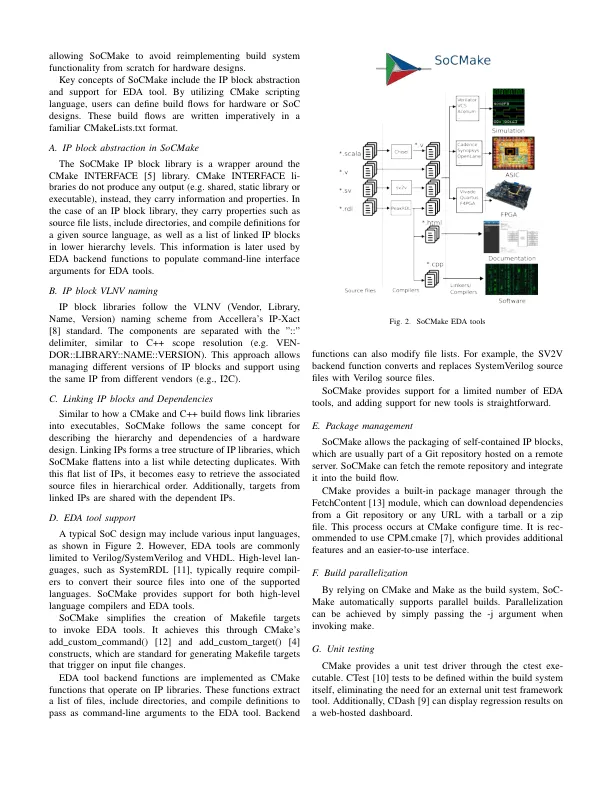

随着电子产品需求的不断增长,新型专用集成电路 (ASIC) 设计的开发周期也越来越短。为了满足这些较短的设计周期,硬件设计人员在设计中应用了 IP 模块的可重用性和模块化原则。带有集成处理器和通用互连的标准片上系统 (SoC) 架构大大减少了设计和验证工作量,并允许跨项目重复使用。然而,这带来了额外的复杂性,因为 ASIC 的验证还包括在集成处理器上执行的软件。为了提高可重用性,硬件 IP 模块通常用更高抽象级别的语言(例如 Chisel、System-RDL)编写。这些模块依靠编译器(类似于软件编译器)来生成 RTL 仿真和实现工具可读的 Verilog 源文件。此外,在系统级,可以使用 C++ 和 SystemC 对 SoC 进行建模和验证,这进一步凸显了软件编译的重要性。这些要求导致需要一个支持典型硬件流程和工具以及 C++、C 和汇编语言的软件编译和交叉编译的构建系统。现有的硬件构建系统被发现存在不足(见 II),特别是对软件编译(即 C++、C 和汇编语言)的支持极少甚至没有。因此,CERN 的微电子部门启动了一个名为 SoCMake [1] 的新构建系统的开发。SoCMake 最初是作为片上系统抗辐射生态系统 (SOCRATES) [14] 的一部分开发的,该系统可自动生成用于高能物理环境的基于 RISC-V 的容错 SoC,后来发展成为用于 SoC 生成的通用开源构建工具。

使用 SoCMake 的硬件和软件构建流程

主要关键词