XiaoMi-AI文件搜索系统

World File Search System正面、埋入和背面的比较研究......

摘要 — 由于器件尺寸不断缩小,标准单元变得越来越小,而电源线占据了可用空间的很大一部分。埋入式电源线 (BPR) 和背面电源 (BSP) 越来越受到关注,因为它们能够将标准单元高度从传统正面电源线 (FS-PR) 中的 6 轨分别降低到 5 轨和 4 轨。在本文中,我们从功率、性能和面积 (PPA) 的角度对器件、标准单元和全芯片设计级别的电源线拓扑进行了全面的比较。我们的实验表明,BPR 和 BSP 的纳米片宽度缩放分别使器件栅极电容降低了 26% 和 40%,从而在标准单元级分别将内部功率提高了 33% 和 40% 以上,在全芯片级分别将总功率下降了 24% 和 30% 以上。此外,与 FSPR 相比,BPR 可将布局缩小 7%,而 BSP 甚至可以再缩小 17%。这项研究还证明了 BPR 和 BSP 拓扑中背面供电网络 (BS-PDN) 在 IR 压降方面的优势。

用于500°C的SIC

以及用于在500°C下运行的硅碳化硅(SIC)传感器和电子设备的开发,长期高温测试以及这些传感器和电子设备的部署需要兼容的包装技术。96%Al 2 O 3陶瓷是一种良好的电绝缘材料,在宽温度和频率范围内可接受的介电常数和低介电损耗。本文为低功率集成电路提供了包装系统,包括基于96%AL 2 O 3陶瓷基板的8-i/o芯片级包装和印刷电路板(PCB)(PCB),以及用于500°C应用的AU厚金属化金属化。介绍了与包装和PCB的设计,包装材料以及特定包装步骤食谱有关的详细信息,包括电线 - 粘合和模具结合。审查了该原型包装方法的一些测试结果,该方法在500 O C时应用于SIC集成电路。关键词高温,包装,氧化铝,厚膜

与污染物相关的化学机械平坦化

化学机械平坦化 (CMP) 工艺已广泛用于平坦化硅基半导体器件中的各种材料,包括电介质、金属和半导体。它是实现纳米级晶圆和芯片级平坦度的最关键步骤之一。然而,在 CMP 工艺之后,晶圆表面上会观察到各种污染物,并且由于它们对器件性能和可靠性具有最直接的影响,因此它们成为许多代快速减小的特征尺寸中最关键的良率降低因素。本书章节提供了 (1) CMP 耗材引起的污染物,例如残留颗粒、表面残留物、有机残留物、焊盘碎片和金属杂质、焊盘污染、水印等,(2) CMP 后清洁过程中刷子引起的交叉污染,(3) 去除这些污染物的 CMP 后清洁。对各种类型的 CMP 污染物的形成及其特性的基本了解将极大地有利于下一代 CMP 浆料和 CMP 后清洁解决方案的开发。

用于集成光信号处理器的微型硅光子器件 /作者=Teng, Min;Safian, Reza;Alahmadi, Yousef;Zhuang, Leimeng;Kojima, Keisuke /创建日期=2020 年 1 月 21 日 /主题=通信、电子和光子器件、信号处理

摘要 集成光信号处理器与传统电信号处理器相结合,有望开辟新一代信号处理硬件平台的道路,从而显著提高处理带宽、延迟和功率效率。硅光子学以其众所周知的特性和潜力,被认为是设备实现的理想候选者,特别是对于高电路复杂度的设备,因此一直是研究的重点。从前面对此类处理器的讨论来看,我们正在考虑在硅光子平台中构建新的构建块,以进一步扩展处理器功能和增加实用功能,特别是微型设备,这些设备能够将复杂电路超密集地集成到此类处理器芯片中。作为启发性的例子,我们在此回顾了我们最近的贡献以及其他组的硅光子设备紧凑设计中的代表性作品,这些设计丰富了处理器构建块的功能,例如多路复用、偏振处理和光学 I/O。本综述中显示的结果反映了最先进的光子制造技术的意义和成熟度,并有助于实现芯片级的大容量、通用光信号处理功能。

内容

本文讨论了一种高度集成的多芯片模块 (MCM) 可布线(薄)微型引线框架 ® (rtMLF ® ) 封装,适用于多功能高性能应用。这种封装包括内部布线引线,用于在封装内连接芯片到芯片。这些布线引线让封装增强了小尺寸特性,作为参考,可以将其与具有两个单个四方扁平无引线 (QFN) 封装的结构进行比较,其中芯片通过电路板走线连接。使用传统的 QFN 工艺确认了 MCM rtMLF 封装的可行性,并且它通过了汽车电子委员会 Q006 (AEC-Q006) 可靠性测试。通过布线引线的芯片到芯片互连在电阻、电感和电容寄生以及插入损耗方面表现出比两个单个 QFN 封装的板载互连更好的电气性能。最后,通过热模拟测得的 MCM rtMLF 封装的热阻低于 MCM 双层芯片级封装 (CSP)。

硅光子学的自由空间应用:综述

摘要:硅光子学最近已将其应用扩展到提供自由空间发射以检测或操纵外部物体。最显著的例子是硅光学相控阵,它可以引导自由空间光束以实现芯片级固态激光雷达。其他例子包括自由空间光通信、量子光子学、成像系统和光遗传学探针。与由体光学元件组成的传统光学系统相比,硅光子学将光学系统小型化为具有许多功能波导元件的光子芯片。通过利用成熟的单片 CMOS 工艺,硅光子学实现了大批量生产、可扩展性、可重构性和并行性。在本文中,我们回顾了基于硅光子学的光束控制技术的最新进展,包括光学相控阵、焦平面阵列和色散光栅衍射。还讨论了用于产生准直、聚焦、贝塞尔和涡旋光束的各种光束整形技术。最后,我们展望了硅光子学在自由空间应用的前景和挑战。

集成 SiC 平台中的纠缠光子对生成

摘要:纠缠在量子信息处理中起着至关重要的作用。由于其独特的材料特性,碳化硅最近成为可扩展实现先进量子信息处理能力的有希望的候选者。然而,迄今为止,在碳化硅中仅报道了核自旋的纠缠,而纠缠光子源,无论是基于块体还是芯片级技术,仍然难以捉摸。在这里,我们首次报告了集成碳化硅平台中纠缠光子源的演示。具体而言,通过在4H绝缘体上碳化硅平台中的紧凑微环谐振器中实现自发四波混频,在电信C波段波长处有效地产生强相关的光子对。在泵浦功率为 0 时,最大巧合与意外比率超过 600。17 mW,对应的成对率为 ( 9 ± 1 ) × 10 3 对/秒。针对此类信号-闲置光子对创建并验证了能量-时间纠缠,双光子干涉条纹的可见度大于 99%。还测量了预期的单光子特性,预期的 𝑔 ( 2 ) ( 0 ) 约为 10 − 3 ,表明 SiC 平台有望成为量子应用的完全集成、CMOS 兼容的单光子源。

TB389:QFN 封装的 PCB 焊盘图案设计和表面贴装指南

瑞萨电子的四方扁平无引线 (QFN) 封装系列产品是一种相对较新的封装概念,目前正在快速发展。该封装系列包括通用版本 QFN,以及 TQFN、UTQFN 和 XQFN 等较薄版本。该系列的引线间距为 0.4 毫米及以上。四方扁平无引线的一个子集是双面类型(4 个侧面中只有 2 个有引线),其中包括 DFN、TDFN、UTDFN 和 XDFN 等版本。在本文档中,术语 QFN 代表所有系列选项。该系列具有多种优势,包括降低引线电感、小尺寸近芯片级封装、薄型和轻重量。它还使用周边 I/O 焊盘来简化 PCB 走线布线,而裸露的铜芯片焊盘技术可提供良好的热性能和电气性能。这些特性使 QFN 成为许多新应用的理想选择,这些应用对尺寸、重量以及热性能和电气性能都很重要。

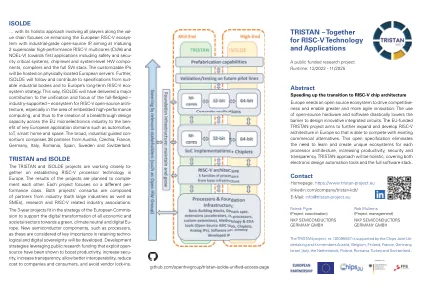

携手 RISC-V 技术与应用

... 采用涉及价值链上所有参与者的整体方法,专注于通过工业级开源 IP 增强欧洲 RISC-V 生态系统,旨在使 2 个超标量高性能 RISC-V 多核 (CVA6 和 NOEL-V) 成熟,面向首批应用,包括安全和安全关键系统、芯片级和系统级硬件组件、编译器和完整的软件堆栈。可定制的 IP 将托管在位于欧洲的物理服务器上。此外,ISOLDE 将遵循并促进合适工业机构的规范以及欧洲的长期 RISC-V 生态系统战略。通过这种方式,ISOLDE将为RISC-V开源架构的成熟(行业支持)生态系统的统一和集中做出重大贡献,特别是在嵌入式高性能计算领域,从而为整个欧盟微电子行业创造突破性的设计能力,造福欧洲关键应用领域,如汽车、物联网、智能家居和空间。这个广泛的、以行业为导向的联盟由来自奥地利、捷克、法国、德国、意大利、罗马尼亚、西班牙、瑞典和瑞士的38个合作伙伴组成。

晶圆级芯片封装中早期焊球偶尔脱离对后续微结构演变和焊点疲劳的影响

摘要 — 电子产品的不断小型化与工业和汽车电子产品的严格可靠性要求相结合,是新兴封装技术面临的一大挑战。一方面是增加对环境载荷下损坏的了解。因此,在温度循环测试之后,对组装在印刷电路板 (PCB) 上的晶圆级芯片级封装的焊点进行了分析。在所研究的封装中,有限数量的接头没有与 PCB 铜垫形成适当的机械连接。虽然这并非有意为之,但这些情况会导致这些接头在最初几个热循环内脱落。然而,这种状况提供了一个独特的机会来比较热机械载荷(连接接头)和纯热载荷(脱落接头)后的焊点微观结构,它们直接位于彼此相邻的位置。结果表明,微结构老化效应可以直接与接头中载荷增加的区域联系起来。对于分离的焊点来说尤其如此,它们几乎可以保留其初始微观结构,直到受到热分布高温部分的影响。通过有限元模拟,如果孤立的焊球从板上脱落,可以进一步量化相邻焊点增加的负载。在介绍的一个案例中,角焊点的寿命仅减少了 85%。