XiaoMi-AI文件搜索系统

World File Search System(010)β-Ga2O3 的低温同质外延 ...

摘要 — 在本文中,我们报告了高迁移率 β -Ga 2 O 3 同质外延薄膜的生长温度,该薄膜的生长温度远低于金属有机气相外延的传统生长温度窗口。在 Fe 掺杂的 (010) 块体衬底上以 600 ◦ C 生长的低温 β -Ga 2 O 3 薄膜表现出卓越的晶体质量,这从测量的非故意掺杂薄膜的室温霍尔迁移率 186 cm 2 /Vs 可以看出。使用 Si 作为掺杂剂实现 N 型掺杂,并研究了 2 × 10 16 - 2 × 10 19 cm −3 范围内的可控掺杂。通过比较二次离子质谱 (SIMS) 中的硅浓度和温度相关霍尔测量中的电子浓度,研究了 Si 的掺入和活化。即使在这种生长温度下,薄膜也表现出高纯度(低 C 和 H 浓度),且补偿受体浓度非常低(2 × 10 15 cm − 3)。此外,在较低温度下生长时,可以观察到突变掺杂分布,正向衰减速度为 ∼ 5nm/dec(与在 810 ◦ C 下生长的薄膜相比,提高了 10 倍)。

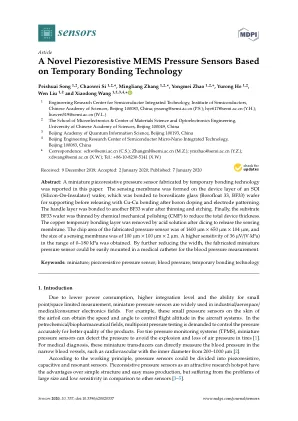

传感器

摘要:报道了一种采用临时键合技术制备的微型压阻式压力传感器。在SOI(Silicon-On-Insulator)晶片的器件层上形成传感膜,将传感膜与硼硅酸盐玻璃(Borofloat 33,BF33)晶片键合支撑,经硼掺杂和电极图形化后通过Cu-Cu键合剥离。将处理层减薄、刻蚀后键合到另一片BF33晶片上。最后采用化学机械抛光(CMP)减薄衬底BF33晶片,降低器件总厚度。切割后用酸溶液去除铜临时键合层,剥离传感膜。制备的压力传感器芯片面积为1600 µ m×650 µ m×104 µ m,传感膜尺寸为100 µ m×100 µ m×2 µ m。在0~180 kPa范围内获得了较高的灵敏度36 µ V / (V · kPa)。通过进一步减小宽度,所制备的微型压力传感器可以轻松安装在医疗导管中用于血压测量。

硅烯插层引起外延双层石墨烯中相当大的带隙

摘要:在双层石墨烯 (BLG) 中打开带隙对于石墨烯基电子和光子器件的潜在应用具有重要意义。本文,我们报告了通过在 BLG 和 Ru 衬底之间插入硅烯在 BLG 中产生相当大的带隙。我们首先在 Ru(0001) 上生长高质量的 Bernal 堆叠 BLG,然后将硅烯插入 BLG 和 Ru 之间的界面,这通过低能电子衍射和扫描隧道显微镜得到证实。拉曼光谱显示,插入的 BLG 的 G 和 2D 峰恢复到独立 BLG 特征。角分辨光电子能谱测量表明,BLG 中打开了约 0.2 eV 的带隙。密度泛函理论计算表明,大带隙打开是 BLG 中掺杂和波纹/应变共同作用的结果。这项工作为 BLG 中带隙打开的机制提供了深刻的理解,并增强了基于石墨烯的器件开发的潜力。关键词:双层石墨烯、带隙、协同机制、插层、硅烯 ■ 介绍

ETMOS:外延过渡金属二硫属化物到宽带隙六方半导体上,用于先进

ETMOS 项目旨在通过分子束外延 (MBE) 和脉冲激光沉积 (PLD) 开发电子级过渡金属二硫属化物 (TMD) 的大面积生长。根据最近关于在六方晶体衬底上生长的 MoS2 外延质量的报告和初步结果,我们将推动这些材料在宽带隙 (WBG) 六方半导体 (SiC、GaN、AlN、AlGaN 合金) 和绝缘蓝宝石上的外延层生长。五个合作伙伴在薄膜生长 (CNRS、SAS)、高级特性和模拟 (CNR、HAS、U-Pa)、加工和电子设备原型 (CNR) 方面拥有互补的技能。将在不同衬底 (Si、蓝宝石、SiC、块状 GaN) 上生长 WBG 半导体模板/薄膜,以完全控制起始材料的特性并制备外延就绪表面,从而实现高质量和均匀的 TMD MBE 和 PLD 生长。沉积范围将从单层 (1L) 到几层 (最多 5) MoS2 和 WSe2,并在直径最大为 100 毫米的晶片上控制亚单层厚度。将开发 MBE 或 PLD 期间的 TMD 替代掺杂,重点是 MoS2 的 p+ 掺杂,这对设备应用具有战略意义。除了生长设施外,ETMOS 联盟还拥有整套形态、结构、化学、光学和电扫描探针表征,有助于在每个生长步骤中实现高质量。将通过专门设计的测试设备研究 TMD 的电性能 (掺杂、迁移率、电阻率等) 以及跨 TMD/WBG 异质结的电流传输。实验将通过生长模拟和 WBG 上 TMD 电子能带结构的从头计算来补充。将制定多尺度表征协议,以将我们的外延 TMD 与使用相同或互补沉积方法的其他小组的结果进行对比。最后,将制造利用 TMDs/WBG 异质结特性的器件原型,包括:(i) 基于 p+-MoS2 与 n-GaN 或 n-SiC 原子突变异质结的带间隧穿二极管和晶体管;(ii) MoS2/GaN 和 MoS2/SiC UV 光电二极管;(iii) 具有 Al(Ga)N/GaN 发射极和 1L TMD 基极的热电子晶体管。开发的材料/工艺的目标是在项目结束时达到 TRL=5。由于 ETMOS 合作伙伴与 SiC 和 GaN 领域的领先工业企业(STMicroelectronics、TopGaN、Lumilog)保持着持续合作,因此来自行业的代表将成为 ETMOS 顾问委员会的成员,为工艺与生产环境的兼容性提供指导。我们的 TMDs 生长活动与常用的 CVD 方法高度互补。我们预计与石墨烯旗舰项目第 1 和第 3 部门的团队将产生强大的协同作用,从而促进欧洲在 TMD 和设备应用大面积增长方面的能力。

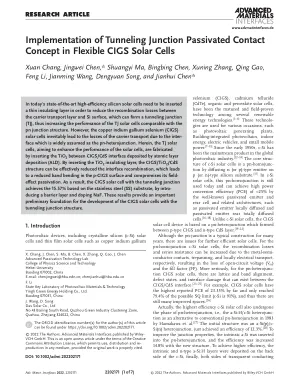

隧道结钝化接触概念在柔性 CIGS 太阳能电池中的实现

在众多可再生能源技术中,铜铟镓硒(CIGS)、碲化镉(CdTe)、有机和钙钛矿太阳能电池是技术成熟且经过现场验证的技术。[1–6] 这些技术用于各种场合,如光伏发电厂、光伏建筑一体化、室内能源、电动汽车和小型移动电源。[7–11] 自20世纪50年代初以来,c-Si一直是全球光伏产业的主流产品。[12–14] c-Si太阳能电池的核心结构是在p(或n)型硅衬底上扩散n(或p)型发射极形成的pn同质结。 [15] 在 c-Si 太阳能电池中,这种 pn 同质结至今仍在使用,并且可以通过众所周知的钝化发射极和背面电池及相关架构(例如钝化发射极局部扩散电池和钝化发射极背面全扩散电池)实现约 25% 的高功率转换效率 (PCE)。[16–18] 与 c-Si 太阳能电池不同,CIGS 太阳能电池器件基于 p 型 CIGS 和 n 型 CdS 层之间形成的 pn 异质结。[19–22]

铁电/非铁电材料界面的电荷捕获效应...

我们研究了限制具有金属/铁电/夹层/Si (MFIS) 栅极堆栈结构的 n 型铁电场效应晶体管 (FeFET) 耐久性的电荷捕获现象。为了探索电荷捕获效应导致耐久性失效的物理机制,我们首先建立一个模型来模拟 n 型 Si FeFET 中的电子捕获行为。该模型基于量子力学电子隧穿理论。然后,我们使用脉冲 I d - V g 方法来测量 FeFET 上升沿和下降沿之间的阈值电压偏移。我们的模型很好地符合实验数据。通过将模型与实验数据拟合,我们得到以下结论。(i)在正工作脉冲期间,Si 衬底中的电子主要通过非弹性陷阱辅助隧穿被捕获在 FeFET 栅极堆栈的铁电 (FE) 层和夹层 (IL) 之间的界面处。 (ii) 基于我们的模型,我们可以得到在正操作脉冲期间被捕获到栅极堆栈中的电子数量。 (iii) 该模型可用于评估陷阱参数,这将有助于我们进一步了解 FeFET 的疲劳机制。

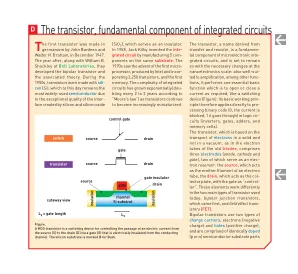

晶体管,集成电路的基本元件

晶体管的名称来自“传输”和“电阻”,它是微电子集成电路的基本元件,在纳米电子尺度上经过必要的改变后,它仍将保持原有的地位:它还非常适合放大等功能,它还执行一项基本功能,即根据需要打开或关闭电流,就像一个开关装置(图)。因此,它的基本工作原理可直接应用于逻辑电路(反相器、门、加法器和存储单元)中二进制代码的处理(0,电流被阻止,1,电流通过)。晶体管基于电子在固体中而不是在真空中的传输,就像旧式三极管的电子管一样,它由三个电极(阳极、阴极和栅极)组成,其中两个电极用作电子储存器:源极用作电子管的发射极灯丝,漏极用作集电板,栅极用作“控制器”。这些元件在当今使用的两种主要晶体管类型中以不同的方式工作:先出现的双极结型晶体管和场效应晶体管 (FET)。双极晶体管使用两种类型的电荷载体,电子(负电荷)和空穴(正电荷),并由相同掺杂(p 或 n)的半导体衬底部分组成

采用湿法钪蚀刻在硅基板上形成硬掩模

如今,微电子技术需要寻找新材料,包括用于创建结构的掩模。中间硬掩模策略是实现微电子制造中光刻和蚀刻之间良好平衡的关键问题之一。微电子和光伏技术中一个有趣的挑战是在 Si 衬底上创建间距垂直取向的硅阵列,用于多功能半导体器件。制造这种结构仍然是一个严重的技术问题,需要寻找新的方法和材料。在这项工作中,我们建议使用钪作为硅上的新硬掩模材料,因为它具有高抗等离子化学蚀刻性和低溅射系数。我们已经证明,对厚度为几纳米的钪层进行湿法蚀刻可用于在硅上获得分辨率高达 4 微米的图案结构,这对于湿法蚀刻方法来说是一个很好的结果。在选定的等离子蚀刻条件下,与其他金属掩模相比,钪是一种具有极佳抗性的硅掩模,蚀刻速率最低。因此,钪硬掩模可以为形成不同的微尺度地形图案开辟新的可能性。

电荷的实验提取与模拟...

摘要 — 我们研究了具有 TiN/Hf 0.5 Zr 0.5 O 2 /SiO 2 /Si (MFIS) 栅极结构的 FeFET 在耐久疲劳过程中的电荷捕获。我们提出了一种通过测量金属栅极和 Si 衬底中的电荷来实验提取存储器操作期间捕获电荷数量的方法。我们验证了在耐久疲劳过程中捕获电荷的数量会增加。这是第一次通过实验直接提取捕获电荷并验证其在耐久疲劳过程中会增加。此外,我们模拟了耐久疲劳过程中捕获电荷和铁电极化切换之间的相互作用。通过实验结果和模拟数据的一致性,我们证明了随着存储窗口的减小:1) Hf 0.5 Zr 0.5 O 2 的铁电特性没有降低。2) 栅极堆栈上带隙中的陷阱密度增加。3) 存储窗口减小的原因是编程操作后捕获电子增加,而与空穴捕获/去捕获无关。我们的工作有助于研究FeFET的电荷捕获行为和相关的耐久疲劳过程。

选择性生长的 Bi2Te3 纳米带的拓扑表面态中的量子传输

拓扑绝缘体的准一维纳米线是基于马约拉纳费米子的量子计算方案的超导混合架构的候选结构。本文研究了低温下选择性生长的 Bi 2 Te 3 拓扑绝缘体纳米带。纳米带定义在硅 (111) 衬底上深蚀刻的 Si 3 N 4 /SiO 2 纳米沟槽中,然后通过分子束外延进行选择性区域生长过程。选择性区域生长有利于提高器件质量,因为不需要进行后续制造来塑造纳米带。在这些无意 n 掺杂的 Bi 2 Te 3 拓扑绝缘体纳米带的扩散传输区域中,通过分析角度相关的通用电导波动谱来识别电子轨迹。当样品从垂直磁场方向倾斜到平行磁场方向时,这些高频电导调制与低频 Aharonov-Bohm 型振荡合并,后者源自沿纳米带周边的拓扑保护表面状态。对于 500 nm 宽的霍尔棒,在垂直磁场方向上可识别出低频 Shubnikov-de Haas 振荡。这揭示了一个拓扑、高迁移率、2D 传输通道,部分与材料本体分离。