XiaoMi-AI文件搜索系统

World File Search System基于聚合物PEG的生物正交触发器,用于乳腺癌的前药激活

前药或可以激活前药的成分,特定于肿瘤。生物正交化学已成为按需前药激活的一种有希望的平台,因为它包括可以在生理条件下进行的化学反应而不会干扰生物学过程。4,5这些反应的选择性,特定城市和相当快的动力学允许精确控制非毒性前药的激活。6 - 8据报道,许多生物正交反应具有很高的选择性前药激活的潜力,例如叠氮化物和三苯基芬丁基之间的Staudinger连接,9和跨环环烯(TCO)和四嗪(TZ)之间的四津连接。10,Staudinger连接主要用于连接应用,因为其动力学相对较慢(K 2〜10-3 m-1 s-1),并且少量报告揭示了其前药激活的潜力。11 - 13在低浓度下,四嗪连接以其快速点击释放反应动力学(K 2〜10 4 m-1 s-1)而闻名,许多报告表明,TZ部分的反应性,

超导体 - 触发器系统中的Andreev and Majorana结合状态的非热零能量

在有限长度的超导型杂种系统中,Majorana结合状态的出现已预测以振荡能水平的形式发生,而奇偶校验横梁围绕零能量。每次零能量交叉都有望产生量化的零偏置电导峰值,但有几项研究报告了电导率峰值固定在零能量的一系列Zeeman领域,但其起源并不清楚。在这项工作中,我们考虑在Zeeman场下与旋转轨道耦合的超导系统,并证明,由于与Ferromagnet Lead的耦合,非富裕效应引起了Majorana和Trivial Andreev结合状态的零能量。我们发现,这种零能量固定效应是由于形成了被称为异常点的非弱势光谱退化性的,其出现可以通过非热性的相互作用,应用的Zeeman Fierd和化学势来控制。此外,根据非热空间空间验证,我们发现非热性会改变单点赫尔米尔拓扑相变为受到多个低能水平的特殊点的特殊点界定的零能量线。这种看似无辜的变化显着使差距截断远低于Hermitian拓扑相过渡,这原则上可以简单地实现。此外,我们揭示了将主要和琐碎的Andreev结合状态与准核定状态分开的能量差距对于产生零能量固定效应的值仍然是强大的。因此,我们的发现对于理解Majorana设备中微不足道和拓扑状态的零能量固定可能很有用。尽管合理的非热性价值确实可以是有益的,但非常强大的非热效应可能会破坏超导性。

神经影像学时间序列中的箭头 - 标识脑功能的因果触发器

图4箭头识别运动任务中的时空定位因果效应。(a)在运动任务范式中,因果效应(τ,顶部),活动(中间)和连通性(底部)的度量。范式由运动时期(左右手和脚,舌头)组成,被休息块隔开。(b)左半球大脑区域的因果效应的详细视图,显示了面板(a)(舌运动)突出显示的间隔中最强的AOT波动。正值表明该区域充当因果效应的下水道,而负值表明该区域是因果关系的来源。(c)面板(b)中四个大脑区域的可视化以及当受试者开始移动舌头时招募的假定因果途径。VIS24和PFC13之间的虚线表示,这两个区域之间的直接信息流不能仅从分析的四个区域中推断出来,并且可能涉及中间体。

arXiv:2304.02786v1 [cs.LG] 2023 年 4 月 5 日

后门攻击是对深度神经网络 (DNN) 模型的严重威胁,攻击者使用带有触发器的输入 (例如补丁) 来激活预先植入的恶意行为。触发器反演是识别后门模型和理解嵌入式对抗行为的有效方法。触发器反演的挑战在于构造触发器的方法有很多种。现有方法无法通过做出某些假设或特定于攻击的约束来推广到各种类型的触发器。根本原因是现有工作在制定反演问题时没有考虑触发器的设计空间。这项工作正式定义并分析了注入不同空间的触发器和反演问题。然后,它基于触发器的形式化和从我们的分析中识别出的后门模型的内部行为,提出了一个统一的框架来反演后门触发器。我们的原型 UNICORN 具有通用性,并且能够有效地反转 DNN 中的后门触发器。代码可在 https://github.com/RU-System-Software-and-Security/UNICORN 找到。

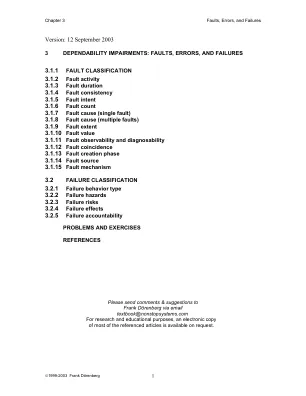

2003 年 9 月 12 日 - 3 项可靠性损害

宇宙辐射导致基于 SRAM 的现场可编程门阵列 (FPGA) 单元发生位翻转,该 FPGA 可实现触发器功能。结果,该触发器的布尔输出被卡住。只要触发器的时钟信号试图将改变的触发器输入传输到该输出,就会激活此故障。故障会产生错误的触发器状态,这是一个错误。反过来,软件会将触发器输出解释为表示即将与附近车辆发生碰撞的标志,并最终向车辆驾驶员发出警报。也就是说,这个无意的警报出现在系统的服务接口上:发生了故障。注意:根据我们的定义,如果将触发器视为一个系统本身而不是一个组件,那么相同的位翻转代表单元级别的故障。

第一学期和第二学期 BCA 课程大纲

组合电路-半加器和全加器,触发器-SR触发器、D触发器、JK触发器、T触发器,序贯电路-触发器输入方程、状态表、状态图和问题。数字元件:集成电路,解码器-3到8线解码器,NAND门解码器,八进制到二进制编码器,多路复用器-4到1线多路复用器,寄存器-带并行负载的4位寄存器,移位寄存器-带并行负载的双向移位寄存器,二进制计数器-4位同步二进制计数器。

使用传输晶体管的条件数据 D 触发器设计,适用于低功耗应用 1 DINESH SALE、2 ASHWANI RANA

1,2 E&CED NIT Hamirpur 摘要- 降低 IC 功耗是当今人们关注的重点。随着 MOS 器件的广泛应用,人们越来越需要功耗更低的电路,尤其是对于使用电池供电的便携式设备,如笔记本电脑和手持式电脑。存储元件消耗了 IC 总功耗的 70%。由于触发器是便携式设备中使用的存储元件的主要部分,因此降低触发器功耗的主要关注点将有助于我们在很大程度上降低 IC 的功耗。减少时钟晶体管的数量可以很好地降低其功耗。由于使用传统 CMOS 逻辑设计的触发器比使用传输门和传输晶体管设计的触发器消耗更多功率,而门控触发器将减少输入和输出相同时不必要的晶体管切换。因此,使用传输门和传输晶体管的门控触发器可用于降低平均功耗。本文提出了一种门控触发器,并将其功耗与输入频率结果与时钟对共享触发器 (CPSFF) 进行了比较。采用 180nm 技术的 Tanner EDA 工具。使用 Cadence EDA 工具设计布局 关键词 - 传输晶体管、传输门、CPSFF、功耗

TC5X配置和配件指南

TC5X触发器手柄附件为用户提供了明显的灵活性,因为他们将TC5X设备调整到零售环境中的不同操作中。TC5X触发器手柄附件被认为是一种易于使用的物品,在TC5X设备的使用寿命中可能需要更换。因此,斑马强烈建议购买斑马触发器手柄服务计划。

亚稳态和同步器:教程 - Typeset.io

主锁存器如何进入亚稳态?考虑图 2 左侧的触发器。假设时钟为低,节点 A 为“1”,输入 D 从“0”变为“1”。结果,节点 A 下降,节点 B 上升。当时钟上升时,它会断开节点 A 的输入并关闭 A—B 循环。如果 A 和 B 恰好在其亚稳态水平附近,则它们需要很长时间才能偏离合法数字值,如下所示。事实上,一个定义是,如果触发器的输出变化晚于标称时钟到 Q 传播延迟 (t pCQ ),则触发器一定是亚稳态的。我们可以通过调整时钟和数据的相对时序来模拟这种效果,直到获得所需的结果,如图 3 所示。顺便说一句,触发器的其他时序不当的输入(异步复位、清除,甚至由于时钟门控不良导致的时钟脉冲太短)也可能导致亚稳态。

![arXiv:2304.02786v1 [cs.LG] 2023 年 4 月 5 日](/simg/6\6572104c226cb2e6beb8c0175c9011d97b43372c.webp)