XiaoMi-AI文件搜索系统

World File Search SystemApplied Digital 使用 Supermicro AI 服务器

Applied Digital 认为,最适合其用户的系统是 Supermicro SYS- 821GE-TNHR,它配备双第四代英特尔® 至强® 铂金处理器 8462Y+。这些服务器使用 NVIDIA HGX H100 GPU,每个 GPU 配备 80GB 内存。NVIDIA H100 为 HPC 提供 67 万亿次浮点运算的 FP64 Tensor Core 计算,而融合 AI 的 HPC 应用程序可以利用 H100 的 TF32 精度实现单精度矩阵乘法运算的 1 千万亿次浮点运算吞吐量。该系统在计算节点内托管八个 H100 Tensor Core GPU 和 900GB/s NVSwitch,用于 GPU 到 GPU 的通信。Applied Digital 选择 2TB 的系统 RAM 来在转移到 GPU 内存之前暂存工作负载。对于网络,Applied Digital 使用 100GbE 进行带内管理和对象存储,并使用 NDR 结构进行 GPU Direct 和融合闪存文件系统流量。利用 NVIDIA DGX 参考架构,Applied Digital 可扩展到在单个并行计算集群中工作的数千个 H100 GPU。

AN10902 使用 LPC32xx VFP - NXP 半导体

ARM 提供基于硬件的矢量浮点 (VFP) 协处理器,可加速浮点运算。ARM VFP 支持以 CPU 时钟速度执行单精度和双精度加法、减法、乘法、除法、乘法累加运算和除法/平方根运算。ARM VFP 可用于提高成像应用程序(如缩放、2D 和 3D 变换、字体生成、数字滤波器或任何使用浮点运算的应用程序)的性能。由于 ARM VFP 是由 ARM 开发和支持的协处理器,因此它在各种工具链、RTOS 和操作系统(如 Keil MDK 开发环境或 Linux)中都受到支持。ARM VFP 符合 IEEE 754 标准。

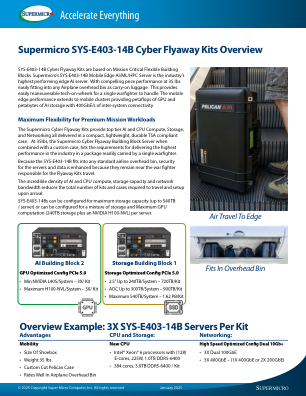

Supermicro SYS-E403-14B Cyber Flyaway 套件概述

SYS-E403-14B Cyber Flyaway 套件基于任务关键型灵活构建模块。Supermicro 的 SYS-E403-14B 移动边缘 AI/ML/HPC 服务器是业界性能最高的边缘 AI 服务器。35 磅的重量具有极具吸引力的性价比,可轻松作为随身行李放入任何飞机行李架。这为单个作战人员提供了易于操作的轮式技术。移动边缘性能扩展到移动集群,提供千万亿次浮点运算的 GPU 和千万亿字节的 AI 存储,以及 400GbE/s 的系统间连接。

模块化中的控制、诊断和错误更正...

确保 CS 容错性的一个有希望的领域是广泛使用可以检测和纠正数据处理过程动态中发生的错误的校正码。此类代码的一个典型特征是校正码的构造结构中存在相互依赖的部分:信息和控制。对已知位置代码的分析表明,这些代码部分在算术运算方面并不平等。获取校正码校验位的过程的非算术性质不允许控制执行算术运算的结果 [1-4]。因此,很明显,在以位置数字系统 (PSN) 运行的 CS 中实现算术运算时,使用位置校正码是不可能的。

数学一年级与 NJSLS 2020 标准一致...

1.NBT.2a 10 可以看作是十个一的组合,称为“十”。 1.NBT.2b 从 11 到 19 的数字由一个十和一个、二、三、四、五、六、七、八或九个一组成。 1.OA.6 在 20 以内进行加减运算,展示在 10 以内进行加减运算的流畅性。使用以下策略:继续计数;凑成十(例如,8 + 6 = 8 + 2 + 4 = 10 + 4 = 14);分解一个数字得到十(例如,13 – 4 = 13 – 3 – 1 = 10 – 1 = 9);使用加法和减法之间的关系(例如,知道 8 + 4 = 12,就知道 12 – 8 = 4);并创建等效但更简单或已知的总和(例如,通过创建已知等效的 6 + 6 + 1 = 12 + 1 = 13 来添加 6 + 7)。

AI 引擎内核编码最佳实践指南

虽然大多数标准 C 代码都可以为 AI 引擎编译,但代码可能需要重构才能充分利用硬件提供的并行性。AI 引擎的强大之处在于它能够使用两个向量执行乘法累加 (MAC) 运算、为下一个运算加载两个向量、存储上一个运算的向量以及在每个时钟周期增加指针或执行另一个标量运算。称为内在函数的专用函数允许您定位 AI 引擎向量和标量处理器并提供几个常见向量和标量函数的实现,因此您可以专注于目标算法。除了向量单元之外,AI 引擎还包括一个标量单元,可用于非线性函数和数据类型转换。

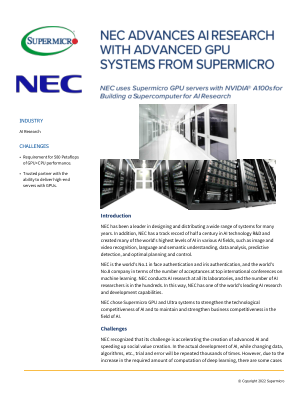

NEC AI 使用 Supermicro 服务器来增加 AI 研究

NEC 选择使用 NVIDIA A100 Tensor Core GPU,主要原因是使用 NVIDIA A100 进行 AI 运算的总计算速度非常出色。此外,A100 的 GPU 内存带宽为 2TB/s,但在深度学习中,这基本上是内存带宽限制。因此,使用 A100 中的 TF32,范围与 FP32 相同,但精度可以视为 FP16,虽然精度没有受到影响,但可以缓解内存带宽瓶颈。换句话说,更容易利用 A100 的计算性能。特别是,NEC 内部许多小组都在研究和开发使用图像的 AI,例如生物特征认证、图像识别和视频识别,这对 GPU 的内存限制更大。因此,NEC 采用了支持 TF32 的 A100。

矩阵理论在量子计算中的应用

矩阵理论是支撑量子计算原理的基本数学框架,有助于操纵和分析量子系统。在量子力学中,信息使用量子比特或量子位来表示,量子比特可以存在于状态叠加中。矩阵理论提供了将这些量子比特状态描述为复杂向量空间中的向量所需的工具,从而允许通过张量积高效地表示多量子比特系统。量子门是量子电路的基本构建块,由酉矩阵表示,确保在操作过程中保持概率幅度。矩阵运算的应用对于量子算法的制定至关重要,例如 Grover 搜索和 Shor 因式分解算法,它们利用量子力学的独特性质来实现优于传统算法的计算优势。

arXiv:2007.14288v1 [quant-ph] 2020 年 7 月 28 日

人工神经网络已被提议作为潜在的算法,可以从在量子计算机上实施和运行中受益。特别是,它们有望大大增强人工智能任务,例如图像处理或模式识别。神经网络的基本构建块是人工神经元,即对输入向量形式的一组数据执行简单数学运算的计算单元。在这里,我们展示了如何实现先前引入的量子人工神经元 [npj Quant. Inf. 5, 26] 的设计,该设计充分利用了叠加态来编码二进制值输入数据,可以进一步推广到接受连续值而不是离散值输入向量,而无需增加量子比特的数量。这一进一步的步骤对于直接应用自动微分学习程序至关重要,该程序与二进制值数据编码不兼容。

![arXiv:2007.14288v1 [quant-ph] 2020 年 7 月 28 日](/simg/c\cf4bcb0444f831488946c85870a570128bf227e2.webp)