XiaoMi-AI文件搜索系统

World File Search SystemIH-ViT:基于视觉变压器的集成电路问世

摘要:针对传统检测方法在IC外观缺陷检测中存在的识别率不高、识别速度慢的问题,提出一种IC外观缺陷检测算法IH-ViT。提出的模型利用CNN和ViT各自的优势,从局部和全局两个角度获取图像特征,最终将两种特征融合进行决策判断缺陷类别,从而获得更高的IC缺陷识别准确率。针对IC外观缺陷主要体现在细节上的差异,传统算法难以识别的问题,对传统ViT进行了改进,在batch内部进行了额外的卷积操作。针对数据集来源多样导致的样本信息不平衡问题,采用双通道图像分割技术,进一步提高IC外观缺陷的识别准确率。最后经过测试,提出的混合IH-ViT模型取得了72.51%的准确率,比单独的ResNet50和ViT模型分别提高了2.8%和6.06%。所提算法可以快速准确地检测出IC外观缺陷状况,有效提高IC封测企业的生产效率。

电子与光子集成电路计划(EPIC)

EPIC 计划下硅光子学平台的成功开发和可行性验证使一系列国防应用成为可能。这些应用包括先进的定位、导航和授时 (PNT) 技术、自主导航、远程 3-D 测绘和高速通信。由于这些贡献以微电子行业长期采用的制造工艺和设备为基础,它们催化了硅光子学的商业化。这种新型技术已被大学、商业公司、国防部和代工服务提供商迅速采用,这些供应商可以根据电路设计师的规格制造微系统。此外,EPIC 催生的制造生态系统简化了创新光子电路概念的快速原型设计。

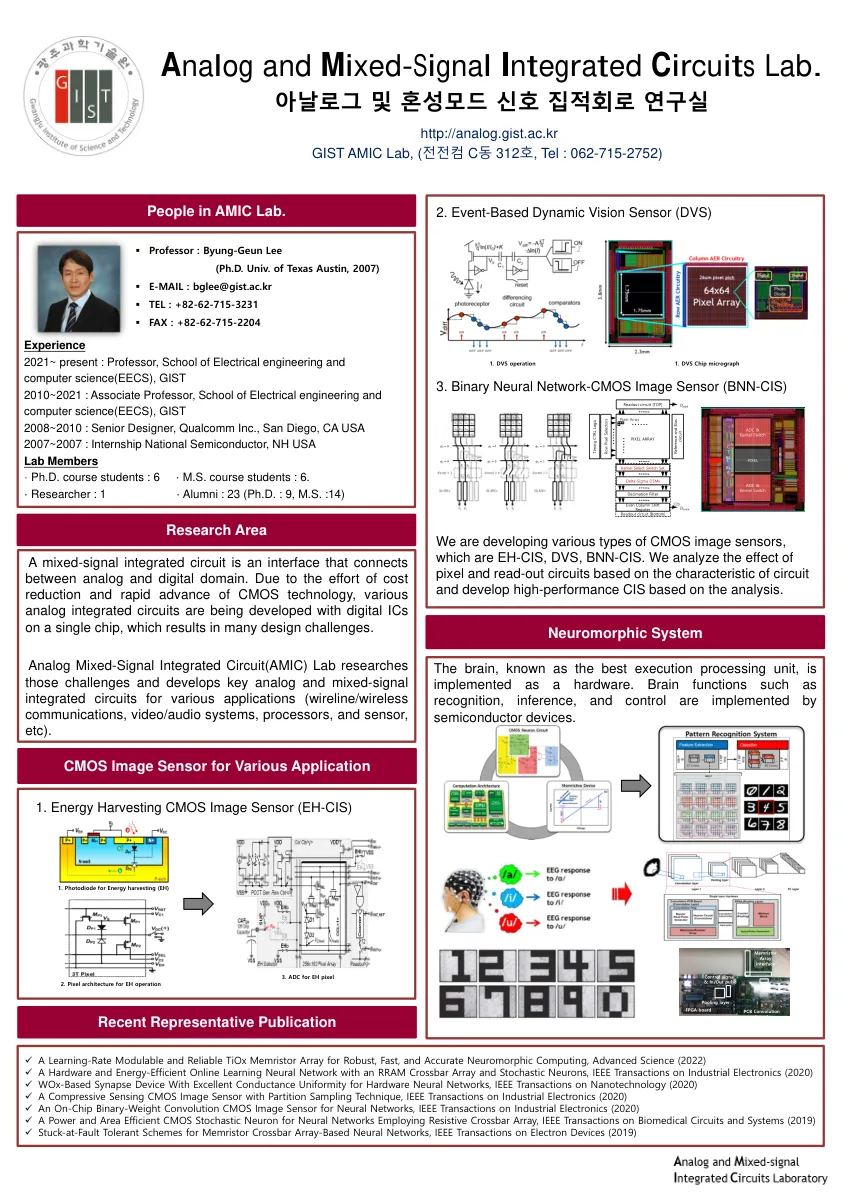

模拟和混合信号集成电路实验室。

一种学习率可靠和可靠的Tiox回忆录阵列,可用于稳健,快速,准确的神经形态计算,高级科学(2022)一种具有RRAM Crossbar阵列和随机神经元的硬件和能源有效的在线学习神经网络,具有对工业性电子构造的功能,具有良好的工业单位(2020)(202020)Wox wox Networks, IEEE Transactions on Nanotechnology (2020) A Compressive Sensing CMOS Image Sensor with Partition Sampling Technique, IEEE Transactions on Industrial Electronics (2020) An On-Chip Binary-Weight Convolution CMOS Image Sensor for Neural Networks, IEEE Transactions on Industrial Electronics (2020) A Power and Area Efficient CMOS Stochastic Neuron for使用电阻横梁阵列的神经网络,生物医学电路和系统的IEEE交易(2019年)基于Memristor跨BAR阵列的神经网络,IEEE Transactions,电子设备上的IEEE Transactions(2019)

超高密度 3D 集成电路的热支架

与传统的 2D 计算系统相比,超密集 3D 集成电路(3D IC),例如单片 3D IC(图 1),可以为数据密集型应用带来巨大的能量延迟积(EDP)优势 [1,2]。为了实现这些优势,需要将多层逻辑和存储器(例如,逻辑和/或存储器设备的薄层,以及相关的信号/全局金属布线)以 3D 形式集成,并使用有限长宽比的后端制程(BEOL)层间过孔(ILV)建立超密集(例如,间距 ≤ 100 纳米)垂直连接 [3]。现有的 BEOL 布线结构已经在使用这种纳米级 ILV。3D IC 变得至关重要,因为工艺技术小型化的根本限制使得传统的缩放路径更加困难。但是,必须克服重大的热挑战才能在多个 3D 层上实现高速和高功率计算引擎 [4-5]。如果没有新技术,未来 3D IC 的上层最高温度将大大超过可靠运行所需的上限(例如 [6] 中的 125°C)。我们使用图 1 中的单片 3D IC 来了解 3D 层中的温升和热耗散(详细分析见第 III 部分)。图 1 中的 N 层中的每一层都包含一层高速、高功率硅逻辑器件(例如,计算引擎)和由铜布线和超低κ 层间电介质 (ILD) 组成的 BEOL 层(例如,用于信号布线)。各层通过超密集 ILV 电连接。在某些设计中,每层还存在硅存储器、存储器访问设备和额外的 BEOL。3D IC 由附加的散热器进行外部冷却,散热器将产生的所有热量以散热器比传热系数 h(W/m 2 /K)散发到环境中。最高温度 T j 取决于散热器、环境温度和 N 层的热特性。散热器创新(如 [7])只需散热器上 10°C 的温升(即 h= 10 6 W/m 2 /K)即可消除 1000 W/cm 2 的热量,尽管

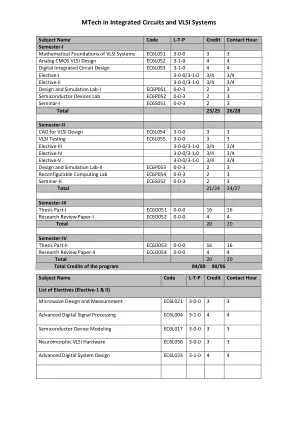

集成电路和超大规模集成电路系统技术硕士

科目名称 代码 LTP 学分 学时 第一学期 VLSI 系统的数学基础 EC6L051 3-0-0 3 3 模拟 CMOS VLSI 设计 EC6L052 3-1-0 4 4 数字集成电路设计 EC6L053 3-1-0 4 4 选修课-I 3-0-0/3-1-0 3/4 3/4 选修课-II 3-0-0/3-1-0 3/4 3/4 设计和仿真实验室-I EC6P051 0-0-3 2 3 半导体器件实验室 EC6P052 0-0-3 2 3 研讨会-I EC6S051 0-0-3 2 3 总计 23/25 26/28 第二学期 VLSI 设计的 CAD EC6L054 3-0-0 3 3 VLSI 测试EC6L055 3-0-0 3 3 选修课-III 3-0-0/3-1-0 3/4 3/4 选修课-IV 3-0-0/3-1-0 3/4 3/4 选修课-V 3-0-0/3-1-0 3/4 3/4 设计与仿真实验室-II EC6P053 0-0-3 2 3 可重构计算实验室 EC6P054 0-0-3 2 3 研讨会-II EC6S052 0-0-3 2 3 总计 21/24 24/27 第三学期论文第一部分 EC6D051 0-0-0 16 16 研究评论论文-I EC6D052 0-0-0 4 4 总计 20 20 16 16 研究评论论文-II EC6D054 0-0-0 4 4 总计 20 20 课程总学分 84/89 90/96

电气工程理学硕士(集成电路专业)

和传输线、PCB 和 IC 材料、阻抗匹配、电源分配网络、并行性和串扰。EMI 和 EMC、反射和终端和 IO 焊盘、片上无源器件、ESD 保护管理、IC 和分立元件封装、热考虑、IC 故障和可靠性、微系统封装和应用。实验室教程:使用集总模型的阻抗匹配、使用微带模型的阻抗匹配、EMC 和 TL 不连续性建模和仿真、键合线建模和仿真、电源分配网络建模、并行传输线建模和分析、串扰和噪声分析、EMI/EMC 干扰分析、片上无源器件和角分析。2. RTL 合成和数字后端:HDL(Verilog)编码基础。可合成的 RTL,

光子集成电路(图片):从INP到Gan- ...

关键字:从第一个实用的(商业)系统实现(SOC)实现到当前状态的基于INP的光子积分电路(PICS)的光子集成电路,光发射器,光子接收器,光子传感器,量子计算抽象进步的抽象进步。使用基于GAN的半导体扩展到光子IC到可见的和近脉冲光谱,有望在光学通信,传感和量子溶液中大量应用。ntroduction Modern Electronics始于晶体管的发明和少数载体注入的发现[1]。综合电路(IC)的发明以及半导体技术的可扩展性[2,3]急剧改变了我们的现代世界,因为晶体管和半导体技术的能力不断提高固态循环的功能,性能和可靠性,同时降低其大小,电力,电力,成本和成本。此缩放率是指数级的,如今导致了每芯片超过500亿晶体管的综合电路,每晶体管成本<0.1微米。集成电路的关键值是通过消除需要通过半导体批处理和晶圆刻度处理来提供设备和电路连接来实现这些改进的能力。半导体激光[4],半导体合金激光[5]以及化合物半导体合金[5]的相关可行性引发了将电子集成电路概念扩展到光子学的可能性。这是Miller [6]在《贝尔系统技术杂志》中首次提出的:本文概述了针对激光束电路微型形式的提案……光刻技术可能允许同时构建复杂的电路模式……如果实现……经济应产生。在该提案以来的过去50多年中,有许多有关图片的研究演示。但是,从综合组成部分中得出的经济价值通常不会超过整合本身的成本,这限制了图片的商业成功和发展。迄今为止,图片的介绍和缩放主要是由它们用于光学通信的使用

UNIT-I 集成电路技术简介-MOS、PMOS、NMOS、...

氧化是将晶圆上的硅转化为二氧化硅的过程。硅和氧的化学反应在室温下就开始了,但在形成非常薄的天然氧化膜后停止。为了获得有效的氧化速率,晶圆必须在高温下放入有氧气或水蒸气的炉子中。二氧化硅层用作高质量绝缘体或离子注入的掩模。硅形成高质量二氧化硅的能力是硅仍然是 IC 制造中的主要材料的重要原因。氧化技术 1. 将清洁的晶圆放置在晶圆装载站中,然后将干氮 (N2) 引入腔室。当炉子达到所需温度时,氮气可防止发生氧化。

EC 536 VLSI制造和集成电路的测试

1技术和过程技术的选择BJT,CMOS和BICMOS集成电路,硅技术与GAAS。2个材料特性。3相图和固体溶解度。4晶体生长。 5热氧化。 6扩散(1)。 7扩散(2)。 +第7周评估 +中期考试。 8离子植入。 9蚀刻和清洁。 10种现代印刷技术。 11外延和化学蒸气沉积(CVD)。 12金属化。 +第12周考试13过程集成(CMOS和BJT)。 14测试程序和测试模式,测试流程图,计划和策略。 15故障诊断和模拟,测试设备。 s t u d e n t g r a d i n g&a s s s s s s s s s s s s s s s m n t4晶体生长。5热氧化。 6扩散(1)。 7扩散(2)。 +第7周评估 +中期考试。 8离子植入。 9蚀刻和清洁。 10种现代印刷技术。 11外延和化学蒸气沉积(CVD)。 12金属化。 +第12周考试13过程集成(CMOS和BJT)。 14测试程序和测试模式,测试流程图,计划和策略。 15故障诊断和模拟,测试设备。 s t u d e n t g r a d i n g&a s s s s s s s s s s s s s s s m n t5热氧化。6扩散(1)。 7扩散(2)。 +第7周评估 +中期考试。 8离子植入。 9蚀刻和清洁。 10种现代印刷技术。 11外延和化学蒸气沉积(CVD)。 12金属化。 +第12周考试13过程集成(CMOS和BJT)。 14测试程序和测试模式,测试流程图,计划和策略。 15故障诊断和模拟,测试设备。 s t u d e n t g r a d i n g&a s s s s s s s s s s s s s s s m n t6扩散(1)。7扩散(2)。+第7周评估 +中期考试。8离子植入。9蚀刻和清洁。10种现代印刷技术。11外延和化学蒸气沉积(CVD)。12金属化。+第12周考试13过程集成(CMOS和BJT)。14测试程序和测试模式,测试流程图,计划和策略。15故障诊断和模拟,测试设备。s t u d e n t g r a d i n g&a s s s s s s s s s s s s s s s m n t

基于二维材料的晶体管,用于未来集成电路

硅互补金属氧化物半导体 (CMOS) 技术的缩放已达到 10 纳米以下技术节点,但进一步缩放越来越具有挑战性,因为器件的栅极静电要求大幅减少沟道厚度以保持所需的性能 1 。场效应晶体管 (FET) 的最终沟道厚度可能在 1 纳米以下范围内。但是,任何三维 (3D) 半导体晶体都无法轻易实现这一点,因为在沟道到电介质界面处电荷载流子的散射增加,导致迁移率严重下降 2 。二维 (2D) 半导体材料单层厚度约为 0.6 纳米,可以提供解决方案。这类材料包括过渡金属二硫属化物 (TMD),其通式为 MX 2 ,其中 M 是过渡金属(例如,Mo 或 W),X 是硫属元素(例如,S、Se 或 Te)3 – 8。材料中没有悬空键也提供了实现更好的通道到电介质界面的潜力。基于机械剥离的单晶 2D 薄片的早期研究,以及基于大面积生长的合成 2D 单层的最新发展,都表明了 2D 晶体管的良好特性。然而,仍有许多挑战有待解决,这使得 2D FET 在未来超大规模集成 (VLSI) 技术中的应用潜力尚不明确。在本篇评论中,我们探讨了 2D FET 在未来集成电路中的发展。我们首先考虑大面积生长