XiaoMi-AI文件搜索系统

World File Search System高密度安全存储器 DDR2 SDRAM

128MB 64M x 16 W3H64M16E-XB2X 400-667 1.8 79 PBGA 11 毫米 x 14 毫米 C、I、M 256MB 2 x 64M x 16 W3H264M16E-XB2X 400-667 1.8 79 PBGA 11 毫米 x 14 毫米 C、I、M 256MB 32M x 64 W3H32M64E-XBX 400-667 1.8 208 PBGA 16 毫米 x 20 毫米 C、I、M 256MB 32M x 72 W3H32M72E-XBX 400-667 1.8 208 PBGA 16 毫米 x 20 毫米 C、I、M 512MB 64M x 64 W3H64M64E-XBX 400-667 1.8 208 PBGA 16 毫米 x 20 毫米 C、I、M 512MB 64M x 72 W3H64M72E-XBX 400-667 1.8 208 PBGA 16 毫米 x 20 毫米 C、I、M 512MB 64M x 72 W3H64M72E-XBXF 400-667 1.8 208 PBGA 16 毫米 x 20 毫米 C、I、M 1GB 128M x 72 W3H128M72E-XSBX 400-667 1.8 208 PBGA 16 毫米 x 22 毫米 C、I、M 1GB 128M x 72 W3H128M72E-XNBX* 400-667 1.8 208 PBGA 16 毫米 x 22 毫米 C、I、M

半导体

Amperex OC50、OC51 CBS-Hytron PT-2A、PT-2S 通用电气 G11、G11A、SX4A、Z2、2N30、2N31 Hydro-Aire A-0、A-1、A-2、A-3、S-0、S-1、S-2 Nat'l Union Electr T18A、T18B 无线电接收器 R1698、R1729、R1734 Raytheon CK716 RCA 2N32、2N33、TA165K、TA166、TA172 Sprague Electric 5A、2N159 Sylvania 2N32、2N33、3N21(四极管!) 德州仪器 100、101、102、103 晶体管产品 2A、2B、2C、 2D、2E、2F、2G、2H、2L 2N32、2N33、2N50、2N51、2N52、2N53 西电 2A、3A(光电二极管)、A1698、A1723、A1729、A1768、AN2891 2N21、2N21A、 2N22、2N23、2N24、2N25、2N26 2N67、2N110 贝尔实验室 BL115、M1689、M1698、M1729、M1734、M1768、M1832 1698、1729、1734、1768 西屋 WX3347、 WX4811、WX4812未知 2N72

'半导体:

比较大的SOC(较小的硅区域)可行,但能够合并以近似较大(更昂贵)的SOC。航空航天应用寻求高性能,但低量使它很困难,因为即使是单个应用程序案例,大型定制ASIC的费用也很难,而在各种航空航天项目中发现的多样性都要少得多。使用chiplet概念,可以承销较小的图1。四核SOC参考体系结构。图2。参考体系结构的扩展。4个基本块,可以在许多安排中结合使用,以适合这些不同的应用程序,以适合许多单独的自定义设计的价格。与当代的耐受性处理器相比,该处理器是内置的,这些处理器是内置的,即尾随边缘半导体技术(例如150 nm),即使是建立在更先进的节点(例如32nm)中的单个芯片组也代表了替代性能的增长。追求chiplet作为模块化策略的希望是要比以前的处理器的逐步实现越来越多地实现,而是提供一种能够将有效扩展到更高水平的性能和更大的功能的方法。很高兴地,奇普特概念可以收获嵌入式构成中的重要发展。主要的是MulɵcoreCompuɵng的出现。现在不是这种情况,很难忘记清洁大型conty的大型耦合的单片locaɵon的方法,而芯片组的想法可能会不利。出于多种原因,在过去的15年中越来越有能力的整体式(单核)组合的进展(借助时钟速度的升级速度标记),将企业推向了整体式的企业,以将整体式的量化计划(核心)(核心)(内核)保存为整体性能,以保持整体性能。嵌入式组合中的第二种criɵcal时尚是朝着异质构成的方式,那里有许多类型的计算机存在于同一复杂的小工具中。在这种情况下,使用“样式”,我们指出,人们相信,几种倾向于通过常规结构驱动(例如,可预测的基于流的处理,可以利用管道上的“可电路”形式,这些形式可以在区域可编程阵列中实现,甚至可以随机地进行了更少的预测分支(又有一个更加可预测的分门形状)(甚至更易于预测的形状)(并且都具有更大的分支形式(以及一个更大的线程形状)(并且都具有一个更大的分类形状(和图形)。没有任何单个处理体系结构可以彻底完成所有操作,主要用于包含处理类型的组合的结构。通常将具有mulɵcore处理器(对于标准 - 摩尔vecompuɵng,尤其是在深度处理中的线程处理),照片处理单元(用于大量的基于移动的处理),以及几个虚拟指示器处理单元(用于额外的型号的频率和无线电频率)。对,再次,chiplet的想法可以通过使用

半导体

Markets News 6 5G smartphone market share to rise from 19% to 43% this year Microelectronics News 10 Nexperia agrees to buy Newport Wafer Fab •Qorvo's quarterly revenue grows as infrastructure recovers despite supply constraints • Skyworks reports record fiscal Q3 revenue, up 52% year-on-year Wide-bandgap electronics News 16 ST manufactures its first 200mm SiC wafers • Cree | Wolfspeed和St扩展150毫米SIC晶圆供应协议超过8亿美元•Transphorm的JV Fab从Fujitsu到新的多数合作伙伴JCP•Akhan制造了首个300mm钻石片和加工设备新闻32 RIBER和LAAS-CNRS创建关节实验室Epenter•Veeco的Q2 Expenter•Veeco的Q2 Exenter Y YEAR 48%48%•AUIS AUICT HEAR 48•AN 48•AN 48 AN 48 AN 48 AN AN 48 AN AN 48 AN 48岁•AN 48 AN 48岁•AN•AN 48•AN 48岁• revenue up 21% • AXT's Q2 revenue up 52% • IQE sees strong Wireless growth for 5G handsets & WiFi 6 routers, offsetting drop for 5G infrastructure rollouts LED News 48 Porotech teams with μ LED panel firm Jade Bird Display • UCSB's DenBaars to receive AAFM-Nakamura Award • Osram presents first quantum dot LED in 2835 package Optoelectronics News 56 LiDAR receiver maker Luminar acquiring InGaAs photodetector chip partner OptoGration • BluGlass demos first RPCVD tunnel-junction laser diodes • PhotonicLEAP awarded over €5m in EU funding • SMART Photonics gains €13m loan from Rabobank Optical communications News 62 II-VI's CEO Mattera to replace Kramer as Chair • NeoPhotonics' revenue第二季度增长的回报•EMCORE的季度收入同比增长56%,这是由宽带驱动的,倍增了Photovoltaics News 67 Fraunhofer ISE Reports Reports Reports Record创敬的GAAS薄膜PV细胞在激光下的GAAS薄膜PV效率为68.9%。

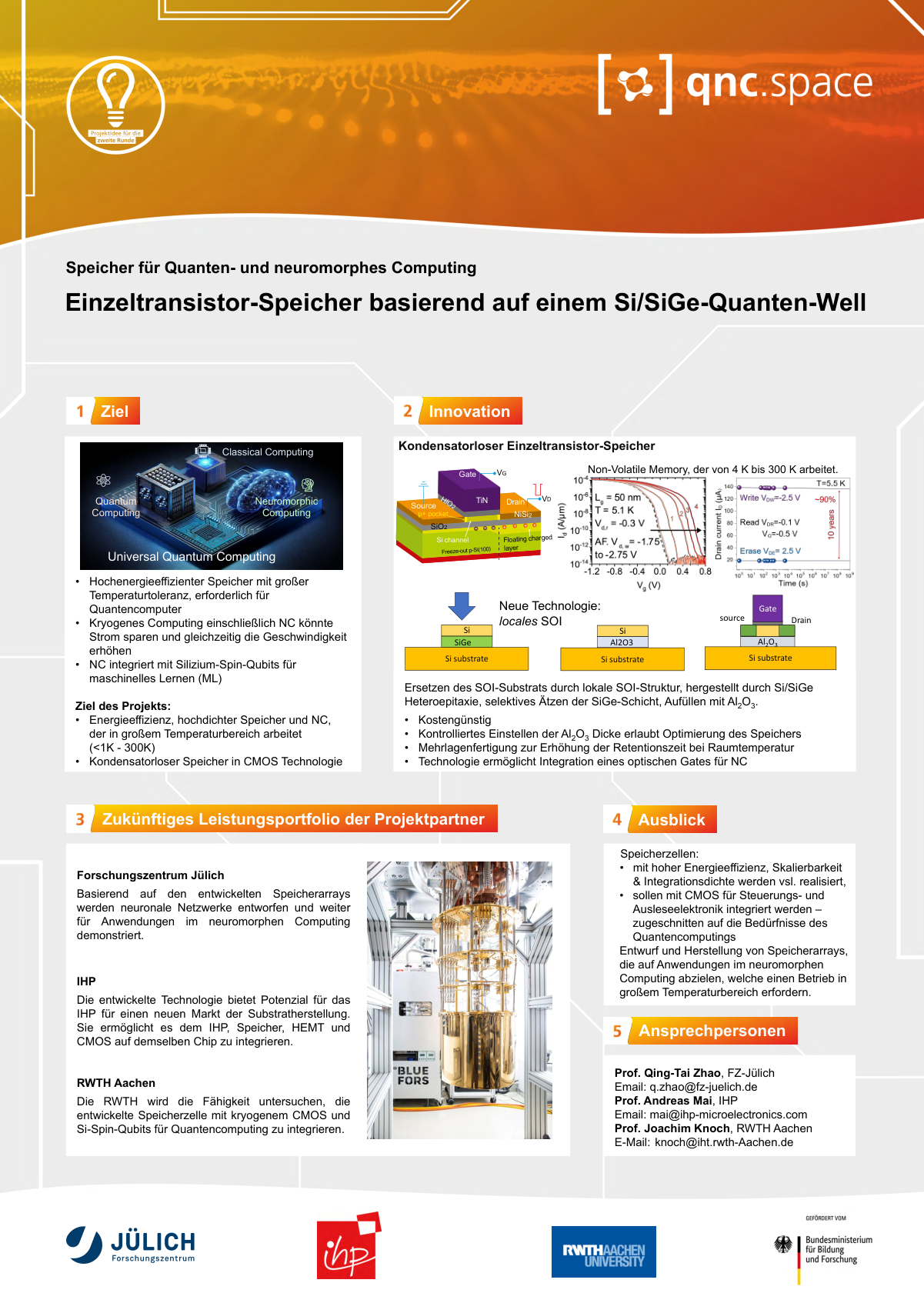

基于 Si/SiGe 的单晶体管存储器...

存储单元:• 可能实现高能效、可扩展性和集成密度,• 将与 CMOS 集成用于控制和读出电子设备 - 根据量子计算的需求设计和制造存储阵列,旨在满足需要在宽温度范围内操作的神经形态计算应用。

四路串行持久性 SRAM 存储器

SRAM 闪存 EEPROM MRAM 非易失性 − √ √ √ 写入性能 √ − − √ 读取性能 √ − − √ 耐久性 √ − − √ 功率 − − − √ MRAM 是一种真正的随机存取存储器;允许在内存中随机进行读取和写入。MRAM 非常适合必须存储和检索数据而不会产生较大延迟损失的应用程序。它提供低延迟、低功耗、无限耐久性和可扩展的非易失性存储器技术。 ASxxxx208 具有串行外设接口 (SPI)。SPI 是一种同步接口,它使用单独的数据和时钟线路来帮助保持主机和从机的完美同步。时钟告诉接收器何时对数据线上的位进行采样。这可以是时钟信号的上升沿(从低到高)或下降沿(从高到低)或两个沿;有关更多详细信息,请参阅本数据表中的指令序列。当接收器检测到正确的边沿时,它可以锁存数据。 ASxxxx208 用双 CS# 连接两个四通道 SPI 设备,提供 8 位 I/O 数据路径。每个设备都可以使用自己的寄存器组进行配置和独立操作,由单独的 CS# 进行管理。ASxxxx208 采用 96 球 FBGA 封装。该封装具有单独的球,用于 CS1#、CLK1# 和 INT1(双四通道 SPI 设备 1)以及 CS2#、CLK2# 和 INT2(双四通道 SPI 设备 2)。该封装与类似的低功耗易失性和非易失性产品兼容。

10T SRAM 存储器单元的设计

1. 简介 当今社会,微电子技术被广泛应用于各种设备中。电子设备在世界范围内的快速普及,促使人们开始审视新技术,尤其是存储器。存储器越来越多地用于生物、无线和可实现设备中。存储器的各个部分在现代 VLSI 系统中组织起来。半导体存储器是 VLSI 架构不可或缺的一部分。RAM(随机存取存储器)有两种形式:SRAM(静态随机存取存储器)和 DRAM(动态随机存取存储器)[2]。动态一词表示理想存储电容器的电荷必须定期刷新,这就是 DRAM 很少使用的原因。为了提高稳定性和功耗,已经提出了许多SRAM单元设计,但传统的6T单元仍然提供了尺寸和性能的良好平衡,因为传统的6T单元具有非常紧凑和简单的结构,但是其操作电压最小并且受到相互冲突的读写稳定性要求的限制,因此它不用于超低电压操作。有几种针对存储器单元的设计提案以提高速度和功率,其中一种技术专注于提高SNM的低功耗(其他存储器配置(7T,8T,9T)各有优缺点)[1]。六个MOSFET组成一个典型的SRAM单元。四个晶体管(PM0,PM1,NM0和NM1)存储一位并形成两个交叉耦合的反相器。有两种稳定状态,用数字 0 和 1 表示。传统的 6T 单元很简单,但在低压下稳定性较差,因此我们努力通过各种方法提高其读写稳定性,例如双轨电源、负位线、带动态反馈管理的单位线等。然而,为了正常运行,6T SRAM 的

高密度安全存储器 DDR3 SDRAM

4GB 512M x 64 W3J512M64X-XPB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 512M x 72 W3J512M72X-XPB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 512M x 64 W3J512M64X-XLB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 512M x 72 W3J512M72X-XLB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 高清 512M x 64 W3J512M64X(T)-XHDX 800-1600 K=1.35,G=1.5 399 PBGA 14 毫米 x 21.5 毫米 C、I、M 4GB 高清 512M x 72 W3J512M72X(T)-XHDX 800-1600 K=1.35,G=1.5 399 PBGA 14 毫米 x 21.5 毫米 C、I、M 8GB 8GB x 64 W3J1G64X-XPBX 800-1600 K=1.35,G=1.5 543 PBGA 24 毫米 x 32 毫米 C、I、M 8GB 8GB x 72 W3J1G72X-XPBX 800-1600 K=1.35,G=1.5 543 PBGA 24 毫米 x 32 毫米 C、I、M