XiaoMi-AI文件搜索系统

World File Search SystemMHLW批准UPTRAVI®片0.2 mg和0.4 ...

京都,日本,2024年12月27日-Nippon Shinyaku Co.动脉高血压(PAH),以及针对小儿0.05 mg的UPTRAVI®片剂的新药物应用。 PAH是一种预后较差的疾病,其特征是肺动脉中血压异常高。它分为特发性PAH,可遗传的PAH和与各种疾病有关的PAH,例如结缔组织疾病和先天性心脏病。由于小儿和成人患者的疾病病理相似,因此还建议针对儿科PAH患者使用前列环素途径药物的联合治疗,内皮素受体受体拮抗剂和磷酸二酯酶5抑制剂。但是,日本的小儿PAH治疗方案受到限制。尤其是在前列环素途径药物的情况下,只有需要连续静脉输注的注射式配方。因此,对前列环蛋白途径药物的口服制剂的需求未满足。UPTRAVI®是一种口服前列环素受体(IP受体)激动剂,对前列环素途径药物中IP受体的选择性很高。UPTRAVI®被认为可以通过与血管平滑肌细胞上的IP受体结合并增加营地产生,从而降低肺动脉压,从而导致血管舒张和抑制血管平滑肌增殖。(右侧的图;下载图像单击此处)。通过剂量滴定确定每个患者的UPTRAVI®的最佳剂量。新的0.05 mg片剂可为儿科患者提供更好的给药,但是有些患者可能需要一次服用更多的片剂。为了支持服用和分配该药物的专利和医疗保健专业人员,我们制定了一个新的药丸案例,尤其是针对儿科配方。使用该案件的专用填充剂,医疗保健专业人员只需通过填充案件就可以分配正确数量的平板电脑。然后,患者每次服用药物时都可以通过单行将片剂分配到一行中,以获取正确的片剂。Nippon Shinyaku专注于稀有和顽固的疾病作为关键领域,并继续努力开发新疗法并提供产品信息。,随着UPTRAVI®最近批准儿科使用的批准,我们希望为患有PAH,家人和医疗保健提供者的小儿患者做出贡献。

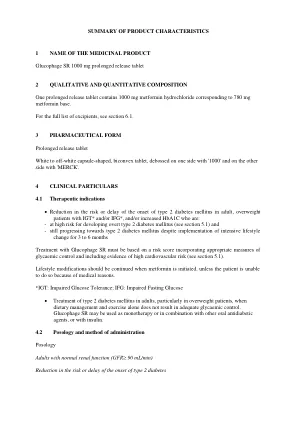

Glucophage SR 1000 mg长时间释放片

•晚餐时,应每天以最高建议的剂量为2片2片,每天服用每天服用1000毫克的葡萄脂SR 1000毫克。•Glucophage SR 1000 mg旨在作为目前用1000 mg或2000 mg二甲双胍盐酸盐治疗的患者进行维护治疗。在开关上,葡萄糖量SR的每日剂量应等于当前的二甲双胍盐酸盐的每日剂量。•在每天以2000毫克高于2000毫克的剂量治疗的患者中,不建议切换到葡萄糖噬细胞SR。•对于新手盐酸二甲双胍的患者,葡萄糖脂SR的通常起始剂量为500 mg,每天给晚餐一次。10至15天后,应根据血糖测量来调整剂量。缓慢的剂量增量可以提高胃肠道耐受性。•如果每天以2000毫克的最大剂量为2000毫克的葡萄糖量SR每天都无法获得血糖控制,则应在早晨和晚餐时用食物给予两次剂量的每日给药时间表。如果仍未实现血糖控制,则可以将患者改用标准的二甲双胍盐酸剂片至最大剂量为3000 mg。•如果从另一种口服抗糖尿病剂转移,则应从葡萄糖噬细胞SR 500 mg开始,然后再切换到葡萄脂SR 1000 mg,如上所述。

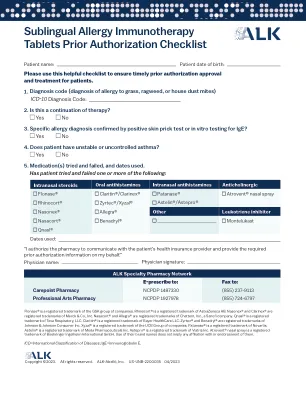

舌下过敏免疫治疗片事先授权清单

Flonase®是GSK公司集团的注册商标。Rhinocort®是阿斯利康AB的注册商标。nasonex®和Clarinex®是Merck&Co.,Inc。Nasacort®和Allegra®的注册商标。QNASL®是Teva Respiratory,LLC的注册商标。Claritin®是拜耳医疗保健有限责任公司的注册商标。Zyrtec®和Benadryl®是Johnson&Johnson Consumer Inc.的注册商标。Xyzal®是UCB公司集团的注册商标。patanase®是诺华的注册商标。astelin®是Meda Pharmaceuticals Inc.的注册商标。Astepro®是ViaTris Inc.的注册商标。Atrovent®NasalSpray是Boehringer Ingelheim International Gmbh的注册商标。使用其品牌名称并不意味着与它们的任何隶属关系或认可。

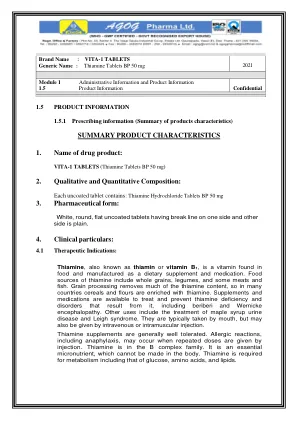

Vita-1片剂(硫胺素片BP 50 mg)

硫胺素是一种维生素,具有抗氧化剂,红细胞生成,认知和情绪调节性,抗动脉粥样硬化,推定的细胞生成和排毒活性。硫胺素已被发现可预防大鼠肝脏和肾脏中铅诱导的脂质过氧化。硫胺素缺乏会导致动物模型中的选择性神经元死亡。神经元死亡与自由基产生增加有关,这表明氧化应激可能在与硫胺素缺乏相关的脑损伤中起重要作用。硫胺素在细胞内葡萄糖代谢中起关键作用,据认为硫胺素抑制葡萄糖和胰岛素对动脉平滑肌细胞增殖的作用。抑制内皮细胞增殖也可能促进动脉粥样硬化。 培养中的内皮细胞已被发现响应高血糖条件的增殖率降低和延迟迁移。 硫胺素已被证明可以抑制葡萄糖对内皮细胞的这种影响。抑制内皮细胞增殖也可能促进动脉粥样硬化。培养中的内皮细胞已被发现响应高血糖条件的增殖率降低和延迟迁移。硫胺素已被证明可以抑制葡萄糖对内皮细胞的这种影响。

一种灌注,血管化的肾脏器官片

摘要能够控制性灌注肾脏器官的能力可以更好地概括天然组织微环境的应用,以进行从药物测试到治疗性的应用。在这里,我们在芯片模型上报告了一个灌注,血管化的肾脏器官,该模型由两个嵌入细胞外基质(ECM)中的两个单独寻址通道组成。分别用肾脏器官和人脐静脉内皮细胞播种,它们形成汇合内皮(Macrovessel)。在灌注过程中,肾脏器官中存在的内源性内皮细胞通过ECM迁移到宏观电池,在那里它们形成了由基质样细胞支撑的Lumen-Lumen吻合术。一旦实现了微观阀的整合,我们就将荧光标记的分子量变化的葡萄糖和红细胞的葡萄糖介绍到宏观电池中,这些葡萄糖通过微血管网络传输到肾脏体内的肾小球上皮氏菌。我们实现受控器官灌注的方法为产生其他灌注的人体组织开辟了新的途径。

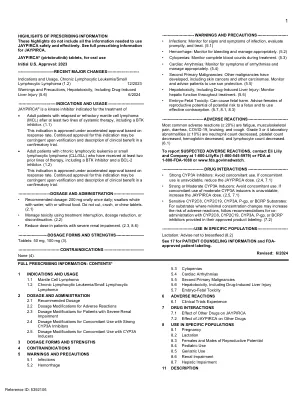

JAYPIRCA®(吡托布替尼)片,口服

BRUIN 试验在 110 名 CLL/SLL 患者中评估了 JAYPIRCA 的安全性,其中 98% 的患者至少接受过两线全身治疗,包括 BTK 抑制剂和 BCL-2 抑制剂[见临床研究(14.2)]。该试验要求血小板计数≥ 50 x 10 9 /L,绝对中性粒细胞计数≥ 0.75 x 10 9 /L,肝转氨酶≤正常上限 (ULN) 的 2.5 倍,ECOG 体能状态为 0 至 2。该试验排除了淋巴瘤活动性中枢神经系统 (CNS) 受累、严重心血管疾病、大出血、无法控制或有症状的心律失常、QTc 间期延长或需要强效 CYP3A 抑制剂或诱导剂或强效 P-gp 抑制剂的患者。

牛仔sr 200 mg胶囊 TicagrelorSandoz®60毫克薄膜涂层片牛仔sr 200 mg胶囊TicagrelorSandoz®60毫克薄膜涂层片

从实验室观测得出的频率(尿酸从下方或参考范围内的基线增加到> ULN。肌酐从基线增加> 50%),而不是粗略的事件报告频率。b,例如,膀胱癌,胃癌,结肠癌出血。c,例如,增加了瘀伤,自发性血肿,出血性核糖的趋势。d,例如结膜,视网膜,眼内出血。e,例如,鼻hemoptysis。f,例如,牙龈出血,直肠出血,胃溃疡出血。g,例如,癫痫病,皮肤出血,Petechiae。h,例如,出血,肌肉出血。i,例如血液,膀胱炎。j,例如阴道出血,出血性诊所,绝经后出血。k,例如,挫伤,创伤性血肿,创伤性出血。l即自发,手术相关或创伤性颅内出血。

基于物理的波纹翅片潜热储能系统建模与数据驱动优化

研究了相变材料在带有波纹翅片的矩形外壳中的固液相变。采用基于物理的模型,探索了翅片长度、厚度和波幅对热场和流体流场的影响。将翅片纳入热能存储系统可增加传热表面积和热穿透深度,从而加速熔化过程。波纹翅片比直翅片产生更多的流动扰动,从而提高熔化性能。更长更厚的翅片可提高熔化速度、平均温度和热能存储容量。然而,翅片厚度对热特性的影响似乎微不足道。较大的翅片波幅会增加传热表面积,但会破坏自然对流,从而减慢熔化前沿的进程。开发了一种基于人工神经网络和粒子群优化的替代模型来优化翅片几何形状。与平面翅片相比,优化后的几何形状使每单位质量的热能存储提高了 43%。数据驱动模型预测的液体分数与基于物理的模型的差异小于 1%。所提出的方法提供了对系统行为的全面理解,并有助于热能存储系统的设计。