XiaoMi-AI文件搜索系统

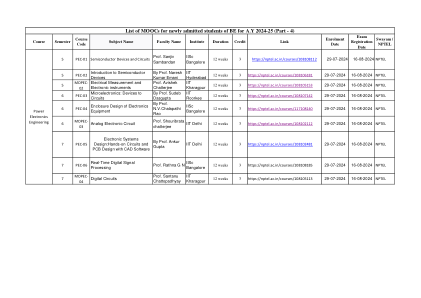

World File Search System2024-25 学年 BE 新生 MOOC 列表(第 4 部分)

03 模拟电子电路 Prof. Shouribrata chatterjee 印度理工学院德里分校 12 周 3 https://nptel.ac.in/courses/108102112 2024 年 7 月 29 日 2024 年 8 月 16 日 NPTEL

本科生手册 - 史密斯工程

电气工程是一门广泛的学科,涵盖从物理世界到纯信息世界。电气工程师是开发电子电路、半导体激光器、微处理器、电动机、数据通信系统和网络、智能机器人系统、医疗器械、航空电子设备等的人才。

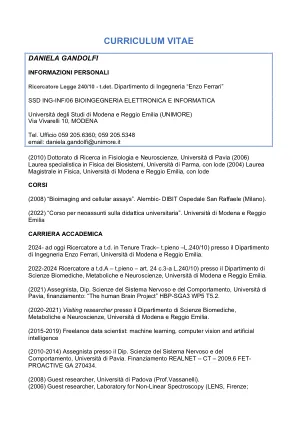

Gandolfi Danie

将神经元活性的计算模型应用于神经形态电子电路。开发用于数据分析和图像分析的机器学习和人工智能算法。分析神经回路活性。非线性光学方法,用于同时记录单个神经元的多重活性。

ES2C0-15模拟电子设计

模拟电子产品是任何电子和电气工程师的核心要求之一。该模块旨在提供有关现代电子中常用的不同模拟电子电路和设备的实际应用的学习。有四个基本类别的组件类别对于任何电子设备或电气工程师都需要理解至关重要。这些是:

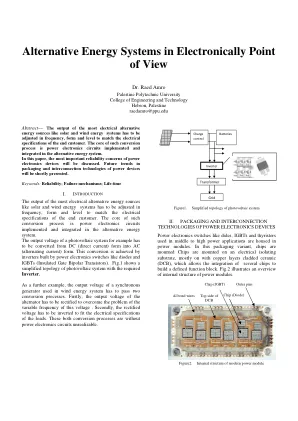

从电子角度看替代能源系统

大多数替代能源(如太阳能和风能系统)的输出必须在频率、形式和水平上进行调整,以符合最终客户的电气规格。这种转换过程的核心是替代能源系统中实施和集成的电力电子电路。例如,光伏系统的输出电压必须从 DC(直流)形式转换为 AC(交流)形式。这种转换是通过由二极管和 IGBT(绝缘栅双极晶体管)等电力电子开关构建的逆变器实现的。图 1 显示了带有所需逆变器的光伏系统的简化拓扑。再举一个例子,风能系统中使用的同步发电机的输出电压必须经过两个转换过程。首先,必须对交流发电机的输出电压进行整流,以克服该电压频率变化的问题。其次,必须对整流后的电压进行逆变,以适应负载的电气规格。如果没有电力电子电路,这两个转换过程都无法实现。

傅里叶级数在电气工程中的应用

电气工程处理的是时间函数信号——各种形状的电振荡。使用简单信号作为示例更容易理解电子电路中发生的基本过程。傅里叶级数展开式包括这样的事实:任何复杂形状的振荡都被具有一定振幅和相位的正弦振荡的总和所取代。

ECE 3311 课程大纲和日历

ECE 3311 – 电子学 I 2021 年夏季第 101 和 D01 节利弗莫尔中心 101 MF 10:00 – 11:50 上午 讲师:Samuel Mark Storrs,博士,PE,EE 115 室,电话 834 – 0144,电子邮件:m.storrs@coe.ttu.edu。课程网站:课程信息将发布在 Blackboard 上。课程描述:电子设备、放大器和电子系统简介。电子电路设计和分析原理。预期学习成果:完成本课程后,学生应该能够做到以下几点:1. 使用运算放大器分析和设计电子电路。2. 使用二极管分析和设计电子电路。3. 使用晶体管分析和设计电子电路。4. 无需使用计算机即可分析偏置电路和小信号单级放大器。 5. 使用计算机分析偏置电路和小信号单级放大器。 6. 描述基本半导体器件的物理操作。 学习成果评估:预期学习成果将通过考试问题进行评估。 教科书:Sedra 和 Smith,《微电子电路》,牛津大学出版社。 软件:LTSpice。 家庭作业:家庭作业将来自教科书和其他来源。家庭作业将发布在网站上。 考试:每周将有四次考试和一次期末考试。不会有补考! ADA 合规声明:任何因残疾而需要特殊安排以满足课程要求的学生应尽快联系教师以做出任何必要的安排。学生应在教师办公时间内出示学生残疾服务部门的适当证明。请注意,在学生残疾服务部门提供适当证明之前,教师不得为学生提供课堂住宿。

半导体气体传感器:材料,技术,设计和应用

摘要:thispaperPapernoverviewofsemenductormaterialsessensessors,其技术,设计和应用。半导体材料包括金属氧化物,导电聚合物,碳纳米管和2D材料。金属氧化物通常是由于其易于制造,低成本,高灵敏度和稳定性而成为首选。他们的一些缺点是低选择性和高工作温度。导电聚合物具有低工作温度的优势,可以检测许多有机蒸气。它们很灵活,但受湿度的影响。碳纳米管在化学和机械上都是稳定的,对NO和NH 3敏感,但需要掺杂剂或修饰来感知其他气体。石墨烯,过渡金属辣椒剂,氮化硼,过渡金属碳化物 /氮化物,金属有机框架和金属氧化物纳米片作为2D材料代表未来的气体感应材料,尤其是在医疗设备中,例如呼吸感应。此概述涵盖了气体传感中最常用的半导体材料,它们的合成方法和形态,尤其是氧化物纳米结构,异质结构和2D材料,以及传感器技术和设计,从现代技术的角度来看,电子电路和系统以及在电子电路和系统中进行应用。

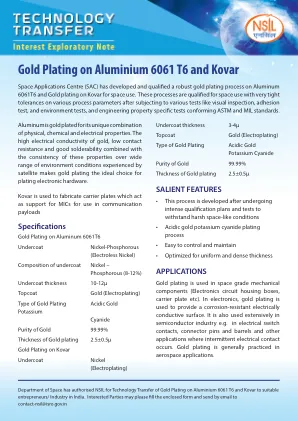

6061 T6 铝和 Kovar 铝镀金

镀金用于航天级机械部件(电子电路外壳盒、载板等)。在电子领域,镀金用于提供耐腐蚀的导电表面。它还广泛用于半导体行业,例如电气开关触点、连接器插针和管筒以及其他发生间歇性电接触的应用。镀金通常用于航空航天应用。